# A WIDEBAND SINGLE-CHANNEL RECEIVER FRONT-END FOR $\rm C/X/KU/KA\text{-}BAND$ SATCOM SYSTEMS

$\label{eq:by} \text{TAHSIN ALPER \"OZKAN}$

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Sabancı University July 2025

# A WIDEBAND SINGLE-CHANNEL RECEIVER FRONT-END FOR $\rm C/X/KU/KA\text{-}BAND$ SATCOM SYSTEMS

| Appro | ved by:                           |

|-------|-----------------------------------|

|       | Prof. YAŞAR GÜRBÜZ                |

|       | Prof. ERKAY SAVAŞ                 |

|       | Asst. Prof. MELİK YAZICI          |

|       | Prof. SERKAN TOPALOĞLU            |

|       | Assoc. Prof. MUSTAFA BERKE YELTEN |

|       |                                   |

Date of Approval: July 22, 2025

#### ABSTRACT

# A WIDEBAND SINGLE-CHANNEL RECEIVER FRONT-END FOR C/X/KU/KA-BAND SATCOM SYSTEMS

### TAHSIN ALPER ÖZKAN

Electronics Eengineering, Ph.D. Dissertation, July 2025

Dissertation Supervisor: Prof. Yaşar Gürbüz

Keywords: SATCOM, receiver, beamforming, phased arrays, SiGe BiCMOS

This thesis focuses on the design and implementation of a radio frequency (RF) integrated receiver for satellite communication (SATCOM). Increasing the bandwidth is one of the key enablers to achieve higher data rates. In mm-wave, a larger bandwidth can be allocated. Since Low-Earth orbit (LEO) SATCOM systems are promising for global connectivity and internet coverage, these SATCOM applications have gathered attention recently. Currently licensed frequency bands for SATCOM reception are C-, X-, Ku-, and Ka-bands. A wideband receiver RF module that covers these SATCOM bands would be cost-efficient. On the other hand, due to orbiting around Earth at more than 200 km altitudes and utilizing mm-wave, the atmospheric path loss is increased. To compensate for increased path loss, one can employ MIMO arrays.

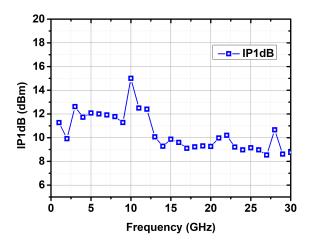

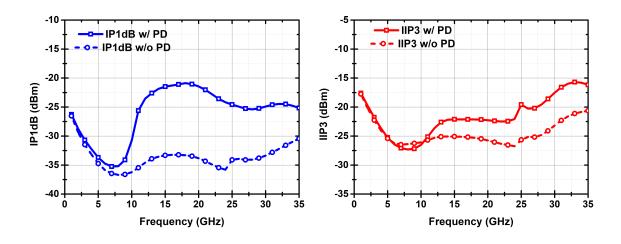

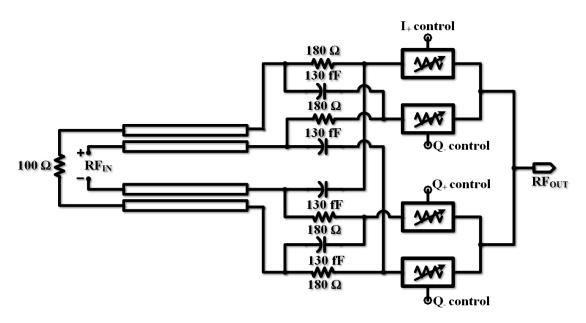

This thesis presents two separate single-channel receiver-ICs for SATCOM applications. The first receiver includes a low-noise amplifier (LNA) and a phase shifter. The designed receiver achieved a 6-bit phase resolution over a bandwidth of 5.7-25 GHz. The first receiver exhibits a peak output referred the third-order intercept point (OIP3) and input referred 1-dB compression point (IP $_{1dB}$ ) of -22 dBm and -23.4 dBm, respectively, thanks to the post-distortion technique employed in the LNA. The second receiver is based on sub-blocks: an LNA, a phase shifter-attenuator, and a variable gain amplifier (VGA). The same post-distortion method is applied in the LNA. A passive vector sum phase shifter topology is adopted to enhance linearity performance. The phase shifter architecture is based on a novel close-loop voltage variable attenuator (VVA). The proposed VVA enables to achieve

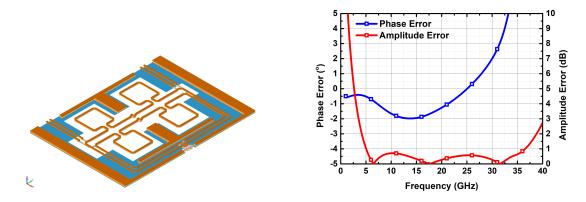

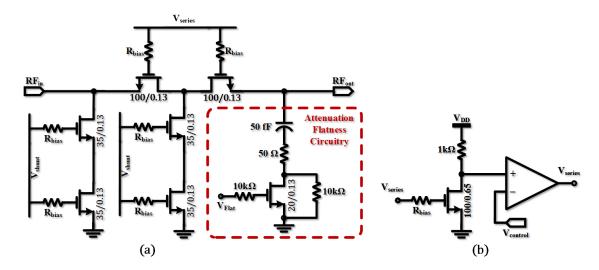

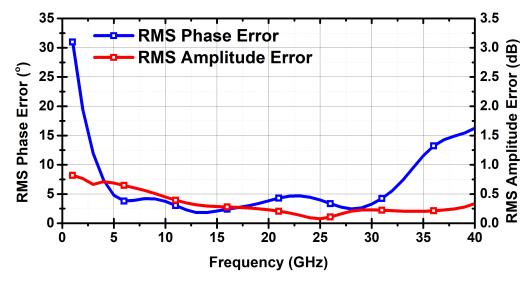

both phase and amplitude control functionality in a single block with low RMS phase and amplitude error. Also, a quadrature hybrid coupler is utilized with a  $1^{st}$ -order polyphase filter (PPF) to obtain 6-bit phase resolution over a wide bandwidth. The VGA is based on a distributed amplifier topology with an RC-feedback to obtain wideband low amplitude error. The second receiver achieves a gain of 25 dB, a minimum noise figure (NF) of 2.7 dB, and -23 dBm IP<sub>1dB</sub> over a wide frequency range of 7-26.4 GHz, which covers multiple licensed frequency bands for SATCOM reception. The second receiver provides 6-bit phase resolution with 5.6° RMS phase error and 36-dB attenuation range. To the best of the authors' knowledge, this receiver achieved the highest attenuation range and highest linearity that supports the multiple licensed frequency bands for SATCOM reception thanks to passive vector sum with the proposed VVA and the post-distortion method applied in the LNA.

## ÖZET

# C/X/KU/KA-BANT SATCOM SİSTEMLERİ İÇİN GENİŞ BANT TEK KANALLI ALICI ÖN UCU

### TAHSIN ALPER ÖZKAN

Elektronik Mühendisliği, Doktora Tezi, Temmuz 2025

Tez Danışmanı: Prof. Dr. Yaşar Gürbüz

Anahtar Kelimeler: SATCOM, alıcı, hüzmeleme, faz dizileri, SiGe BiCMOS

Bu tez, uydu haberleşmesi (SATCOM) için bir radyo frekansı (RF) entegre alıcının tasarımı ve uygulamasına odaklanmaktadır. Bant genişliğinin artırılması, daha yüksek veri hızlarına ulaşmanın temel unsurlarından biridir. mm dalga boylarında daha büyük bir bant genişliği tahsis edilebilir. Alçak Dünya yörüngesi (LEO) SATCOM sistemleri küresel bağlantı ve internet kapsamı için umut vaat ettiğinden, bu SATCOM uygulamaları son zamanlarda dikkat çekmektedir. Şu anda lisanslı SATCOM yayın frekans bantları C, X, Ku ve Ka bantlarıdır. Bu SATCOM bantlarını kapsayan geniş bantlı bir alıcı RF modülü uygun maliyetli olacaktır. Öte yandan, Dünya etrafında 200 km'den fazla irtifada yörüngede olması ve mm dalga boylarını kullanması nedeniyle atmosferik yol kaybı artmaktadır. Artan yol kaybını telafi etmek için MIMO dizileri kullanılabilir.

Bu tez, SATCOM uygulamaları için iki ayrı tek kanallı alıcı-IC sunmaktadır. İlk alıcı, düşük gürültülü bir yükselteç (LNA) ve bir faz kaydırıcı içerir. Tasarlanan alıcı, 5,7-25 GHz bant genişliği üzerinde 6 bit faz çözünürlüğü elde etti. İlk alıcı, LNA'da kullanılan bozulma sonrası tekniği sayesinde, üçüncü dereceden kesme noktasına (OIP3) referanslı tepe çıkışı (-22 dBm) ve 1 dB sıkıştırma noktasına (IP1dB) referanslı girişte sırasıyla -23,4 dBm'lik bir tepe çıkışı sergiledi. İkinci alıcı, alt bloklara dayanmaktadır: bir LNA, bir faz kaydırıcı-zayıflatıcı ve bir değişken kazançlı amplifikatör (VGA). Aynı bozulma sonrası yöntemi LNA'da da uygulandı. Doğrusallık performansını artırmak için pasif vektör toplamı faz kaydırıcı topolojisi benimsenmiştir. Faz kaydırıcı mimarisi, yeni bir kapalı çevrim gerilim kontrollü zayıflatıcıya (VVA) dayanmaktadır. Önerilen VVA, düşük RMS faz ve genlik hatası ile tek

bir blok içinde hem faz hem de genlik kontrol işlevselliğini gerçekleştirmeye olanak tanımıştır. Ayrıca, geniş bir bant genişliği üzerinde 6 bit faz çözünürlüğü elde etmek için bir-dereceli çok fazlı filtre (PPF) ile bir kareel hibrit kuplör kullanılmıştır. VGA, geniş bant düşük genlik hatası elde etmek için RC geri beslemeli dağıtılmış bir amplifikatör topolojisine dayanmaktadır. İkinci alıcı, SATCOM alımı için bir-den fazla lisanslı frekans bandını kapsayan 7-26,4 GHz geniş bir frekans aralığında 25 dB'lik bir kazanç, 2,7 dB'lik minimum gürültü değeri (NF) ve -23 dBm IP $_{1dB}$  elde ediyor. İkinci alıcı, 5.6° RMS faz hatası ile 6 bit faz çözünürlüğü ve 36 dB zayıflatma aralığı sağlamaktadır. Yazarların bilgi birikimine göre, bu alıcı; LNA'da uygulanan bozulma sonrası yöntemi, ve önerilen VVA'nın kullanıldığı pasif vektör toplamı metotları sayesinde, SATCOM alımı için birden fazla lisanslı frekans bandını destekleyen en yüksek zayıflatma aralığını ve en yüksek doğrusallığı elde etmiştir.

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my supervisor Prof. Yaşar Gürbüz, for his invaluable guidance not only in academia but also my life over the past ten years. I am also grateful for his confidence in me, as well as for his unwavering support, and dedication. His extensive expertise and continuous encouragement have been instrumental in making this thesis possible.

In addition to my thesis advisor, I would also like to thank my thesis jury members, Prof. Erkay Savaş, Asst. Prof. Melik Yazıcı, Prof. Serkan Topaloğlu, and Assoc. Prof. Mustafa Berke Yelten for their valuable time to spare in my thesis committee and for their precious comments, advice, and feedback.

I thank to my friends and colleagues at the Sabanci University Microelectronics Research Group (SUMER), Asst. Prof. Ömer Ceylan, Samira Firouz, Mehmet Emre Çakır, Oğuzhan Yıldırım, Mete Kaan Lermi, Alp Bilgin, Yankı Doğa Pekindil, Hüseyin Kaya, Oğuz Çınar, Uğur Dizer, and Talha Kerem Bilgin for their friendship which makes the working environment comfortable for me and keep me motivated, including the former members of SUMER İlker Kalyoncu, Can Çalışkan, Elif Gül Arsoy, Abdurrahman Burak, Cerin Ninan Kunnatharayil, Hamza Kandiş, Berke Güngör, Mir Hassan Mahmud, Umut Barış Göğebakan, Ali Bahadir Özdöl, Kutay Altıntaş, Cengizhan Kana, Ajten Fejzullahu, Erkut Gürol, Nezih Kaan Veziroğlu, Serhan Özboz, and Umut Barut for their support and guidance. I also thank the laboratory specialist, Ali Kasal and Enver Kaan Çabuk, for his support and help.

I am grateful to Meliz, İlke, Kubilay, Gizem, Burak, Baran, Tekin, and Oytun and many others for their friendship throughout the years in high school and university.

I would like to thank IHP-Microelectronics for fabricaation support. This work was supported by Turkish Scientific and Technology Research Institution (TUBITAK) under grant 123E566 Also, I would like to thank TUBITAK BIDEB 2211-A for supporting me with scholarship throughout my studies.

Finally, I would like to express my gratitude to my family who has supported me in every decision I have taken and help me to be the person now. Also, I would like to thank my dear wife, Sevgi for her endless love and support in being anchor for me. I would not be at this position without them.

Eşime ve aileme...

To my wife and my family...

# TABLE OF CONTENTS

| LI | ST ( | OF TABLES                                                          | xii  |

|----|------|--------------------------------------------------------------------|------|

| LI | ST ( | OF FIGURES                                                         | xiii |

| LI | ST ( | OF ABBREVIATIONSx                                                  | vii  |

| 1. | INT  | TRODUCTION                                                         | 1    |

|    | 1.1. | Satellite Communication Systems                                    | 3    |

|    | 1.2. | SiGe BiCMOS Technology                                             | 5    |

|    |      | 1.2.0.1. IHP 0.13 $\mu m$ SiGe BiCMOS (SG13S) Tehcnology           | 9    |

|    | 1.3. | Thesis Overview                                                    | 9    |

|    | 1.4. | Thesis Organization                                                | 11   |

| 2. | BA   | CKGROUND                                                           | 12   |

|    | 2.1. | Phased Arrays                                                      | 12   |

|    |      | 2.1.1. Operating Principle                                         | 12   |

|    |      | 2.1.2. Phased Array Architectures                                  | 13   |

|    | 2.2. | Phase and Amplitude Control Blocks                                 | 16   |

|    |      | 2.2.1. Attenuators and VGAs                                        | 17   |

|    |      | 2.2.2. Phase Shifters                                              | 20   |

|    | 2.3. | Existing Literature in Phased Array Systems for Satellite Communi- |      |

|    |      | cations                                                            | 22   |

| 3. | WI   | DEBAND SINGLE-CHANNEL RECEIVER FRONT-ENDS                          |      |

|    | FOI  | R C/X/Ku/Ka-BAND SATCOM SYSTEMS                                    | 24   |

|    | 3.1. | Receiver with LNA and Phase Shifter                                | 24   |

|    |      | 3.1.1. Low Noise Amplifier                                         | 25   |

|    |      | 3.1.2. Passive Vector-Sum Phase Shifter                            | 34   |

|    |      | 3.1.2.1. I/Q Signal Requirements                                   | 35   |

|    |      | 3.1.2.2. Quadrature All-Pass Filter Design                         | 38   |

|    |      | 3.1.3. Voltage Variable Attenuator                                 | 39   |

|    |      |        | 3.1.3.1.  | The Design of Opamp                            | 42 |

|----|------|--------|-----------|------------------------------------------------|----|

|    |      |        | 3.1.3.2.  | Attenuator Core                                | 42 |

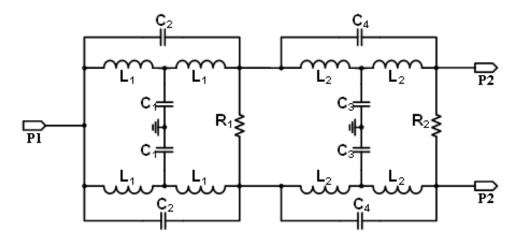

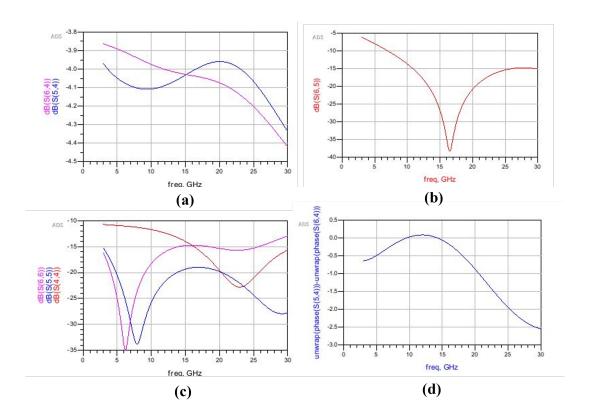

|    |      |        | 3.1.3.3.  | Power Combiner Design                          | 47 |

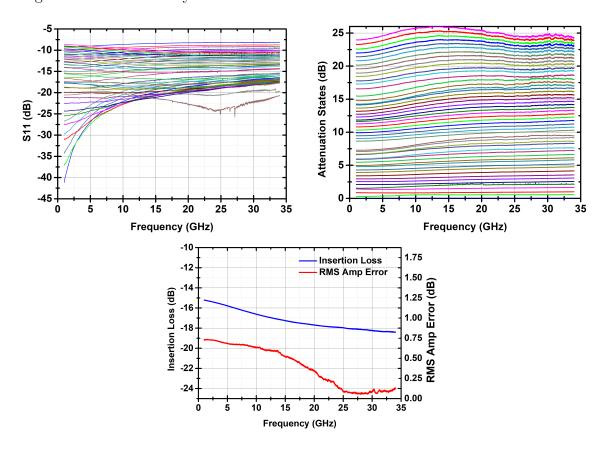

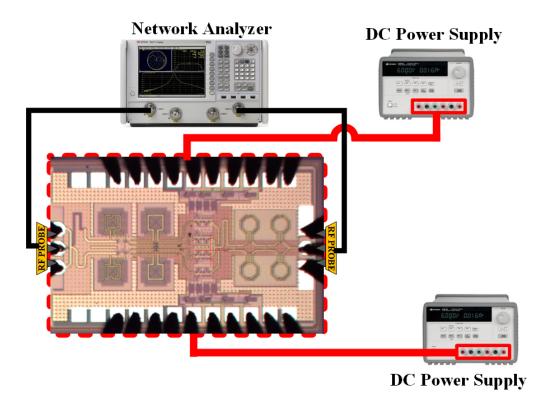

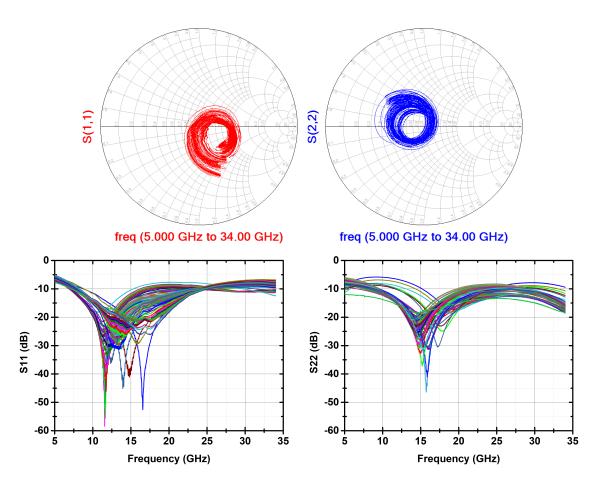

|    |      |        | 3.1.3.4.  | Measurement Results of The Phase Shifter       | 47 |

|    |      | 3.1.4. | Receiver  | Measurements                                   | 51 |

|    | 3.2. | A Wie  | deband Si | ngle-Channel Receiver Front-End For C/X/Ku/Ka- |    |

|    |      | Band   | SATCOM    | System                                         | 54 |

|    |      | 3.2.1. | Low Noi   | se Amplifier                                   | 55 |

|    |      | 3.2.2. | Passive Y | Vector-Sum Phase Shifter                       | 59 |

|    |      |        | 3.2.2.1.  | VVA and Attenuation Flatness Circuitry         | 60 |

|    |      |        | 3.2.2.2.  | Voltage DAC                                    | 62 |

|    |      |        | 3.2.2.3.  | SPI                                            | 62 |

|    |      | 3.2.3. | Variable  | Gain Amplifier                                 | 69 |

|    |      | 3.2.4. | Receiver  | Simulations                                    | 75 |

| 4. | CO   | NCLU   | SION A    | ND FUTURE WORK                                 | 81 |

|    | 4.1. | Summ   | ary of Wo | ork                                            | 81 |

|    | 4.2. | Future | e Work    |                                                | 82 |

| ΒI | BLI  | OGRA   | PHY       |                                                | 83 |

| ΔΊ | PPE  | NDIX   |           |                                                | 90 |

# LIST OF TABLES

| Table 1.1. | Performance comparison of numerous device technologies for            |    |

|------------|-----------------------------------------------------------------------|----|

| radio      | frequency integrated circuits                                         | 8  |

| Table 3.1. | Comparison with the Si-based wideband LNA works                       | 33 |

| Table 3.2. | Comparison of the designed phase shifter with the state-of-the-art $$ | 68 |

| Table 3.3. | Comparison of the designed VGA with the state-of-the-art              | 74 |

| Table 3.4. | Performance comparison of state-of-the-art beamformers in             |    |

| SATO       | COM bands                                                             | 80 |

# LIST OF FIGURES

| Figure 1.1. | Cellular-technology generations in the world-wide market in             |    |

|-------------|-------------------------------------------------------------------------|----|

| the pa      | st decades                                                              | 1  |

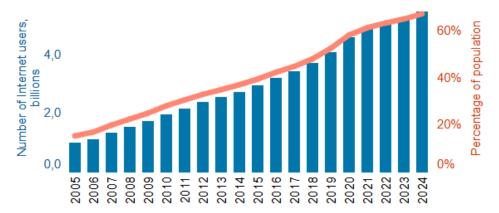

| Figure 1.2. | The number of people using internet in 2005-2024                        | 2  |

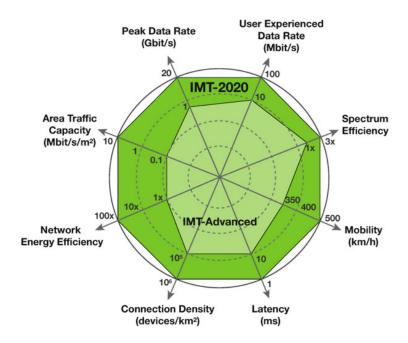

| Figure 1.3. | IMT-2020 specifications                                                 | 3  |

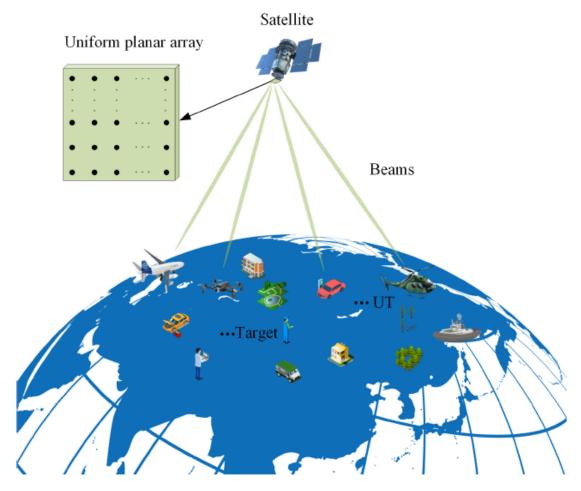

| Figure 1.4. | A LEO satellite system with a massive MIMO                              | 5  |

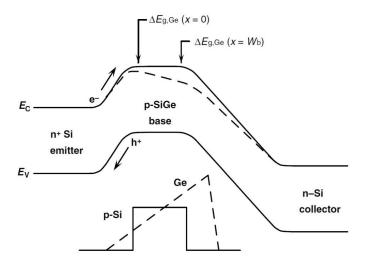

| Figure 1.5. | The representation of the energy band diagram of SiGe HBT               |    |

| (top) a     | and Si BJT (bottom)                                                     | 6  |

| Figure 1.6. | The cross-section of IHP's 0.13 $\mu\mathrm{m}$ SiGe BiCMOS SG13S tech- |    |

| nology      | ······································                                  | 10 |

| Figure 2.1. | Phased array systems, in reception (left) in transmission (right)       | 13 |

| Figure 2.2. | (a) Passive and (b) active phased array architectures                   | 14 |

| Figure 2.3. | Beamformers, analog beamformer (left) digital beamformer                |    |

| (right)     |                                                                         | 15 |

| Figure 2.4. | RF phase shifting methods (a) digital, (b) IF, (c) LO, and (d)          |    |

| RF          |                                                                         | 16 |

| Figure 2.5. | Peak SLL due to N bits of quantization with respect to the              |    |

| numbe       | er of phase control bits (left) and Required antenna number to          |    |

| reach       | the same RMS side-lobe level with different phase resolutions           |    |

| (right)     |                                                                         | 17 |

| Figure 2.6. | Attenuator networks                                                     | 18 |

| Figure 2.7. | The schematics of conventional VVAs                                     | 20 |

| Figure 2.8. | The schematics of passive phase shifters: Switched-line (a),            |    |

| Switch      | ned-filter (b) and Reflection-type (c) phase shifters                   | 21 |

| Figure 2.9. | The block diagram of the vector sum phase shifter                       | 22 |

| Figure 3.1. | The block diagram of the first receiver chain                           | 25 |

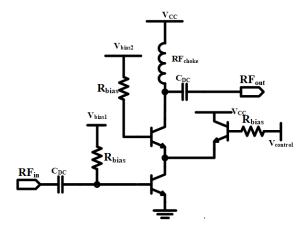

| Figure 3.2. | The schematic of the designed LNA                                       | 28 |

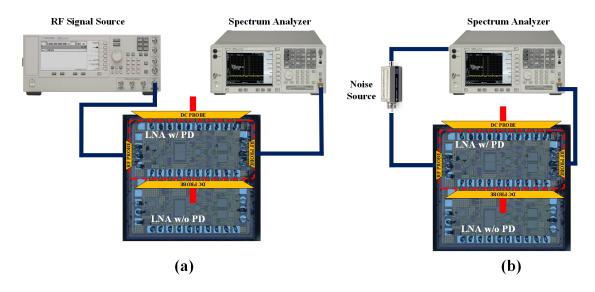

| Figure 3.3. | The S-parameter measurement setups for the designed LNA $\dots$         | 29 |

| Figure 3.4. | The measurement setups for the designed LNA: (a) Linearity              |    |

| and (b      | o) NF                                                                   | 29 |

|             |                                                                         |    |

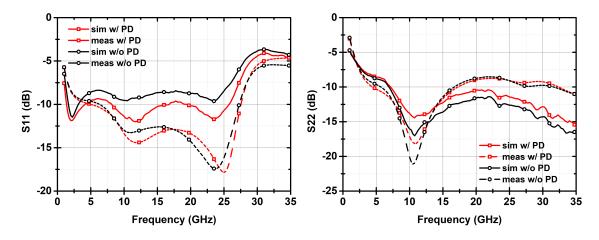

| Figure 3.5. The measured input and output matchings of the designed                  |

|--------------------------------------------------------------------------------------|

| LNA: (left) S11 and (right) S22                                                      |

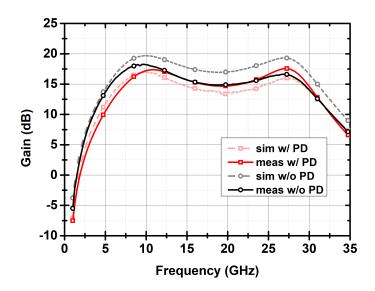

| Figure 3.6. The measured gain of the designed LNA                                    |

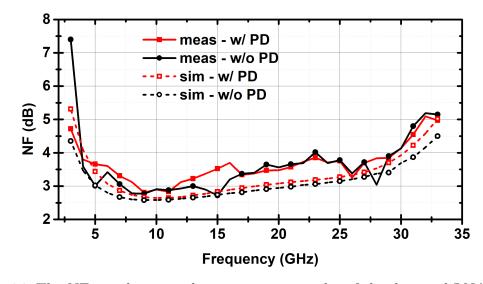

| Figure 3.7. The NF simulation and measurement results of the designed                |

| LNA                                                                                  |

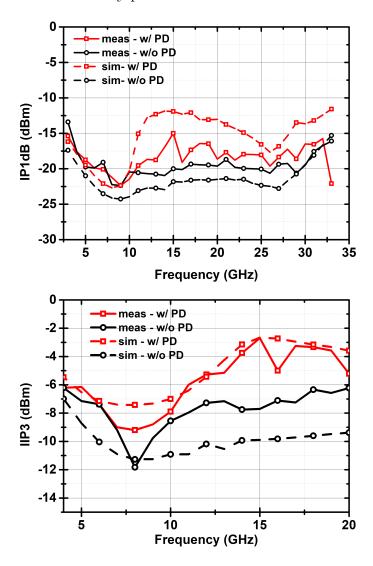

| Figure 3.8. The linearity simulation and measurement results of the de-              |

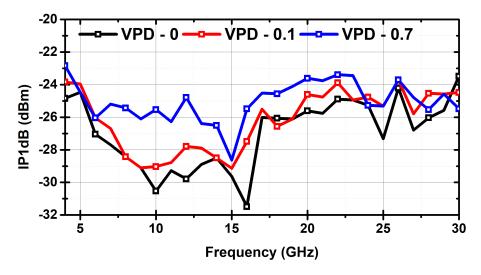

| signed LNA: (top) IP1dB and (bottom) IIP3                                            |

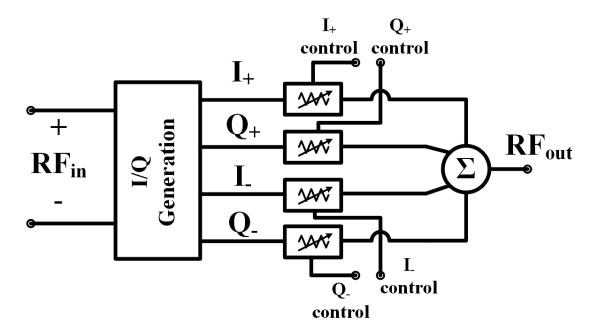

| Figure 3.9. The block diagram of the phase shifter                                   |

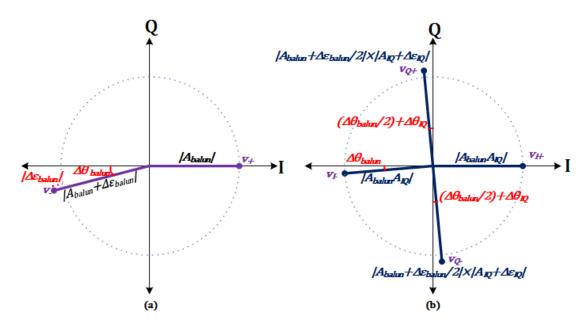

| Figure 3.10. Signals after (a) balun (b) I/Q generation networks $\dots$             |

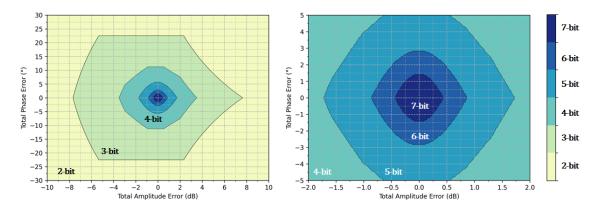

| Figure 3.11. Bit resolution regions for different phase and amplitude errors         |

| Figure 3.12. The schematic of QAF                                                    |

| Figure 3.13. The simulation results of QAF                                           |

| Figure 3.14. The proposed closed-loop VVA                                            |

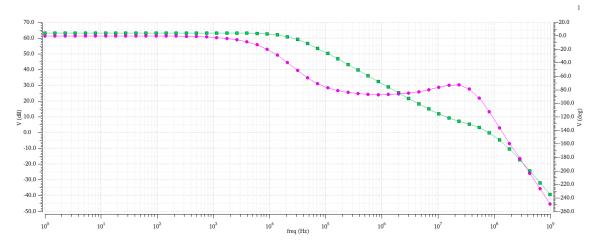

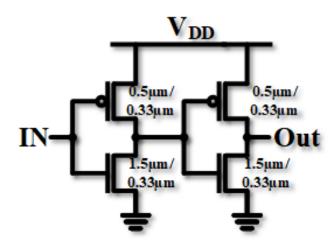

| Figure 3.15. (a) Schematic and (b) layout of the designed Opamp                      |

| Figure 3.16. The simulation results of the designed Opamp                            |

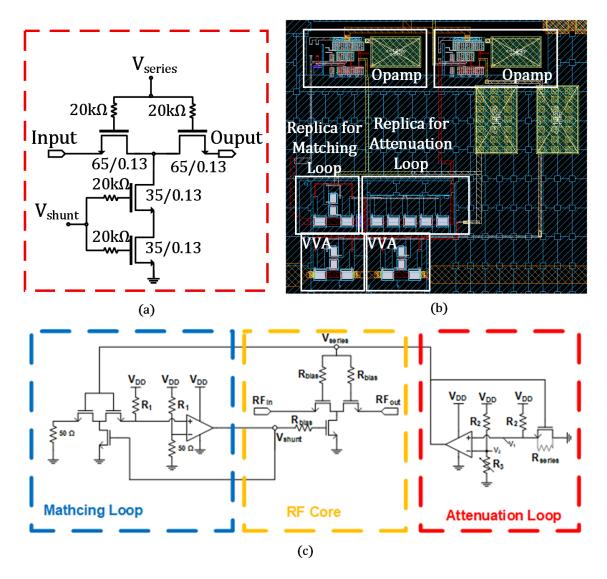

| Figure 3.17. The designed closed-loop VVA: (a) attenuation core, (b) the             |

| layout of the close-loop VVA, (c) the schematic of the proposed close-               |

| loop VVA                                                                             |

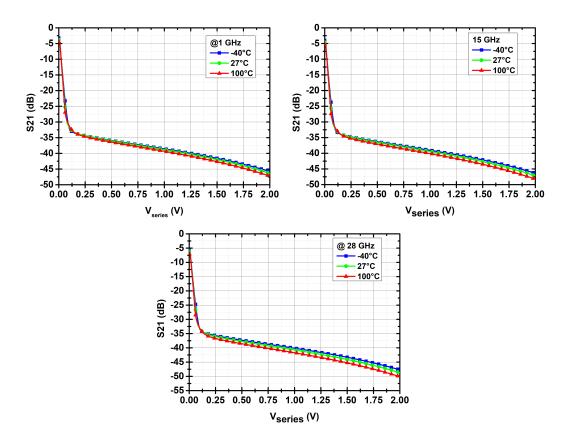

| Figure 3.18. Attenuation of VVA at different temperatures (top left) at $1$          |

| GHz, (top right) at 15 GHz, and (bottom) at 28 GHz                                   |

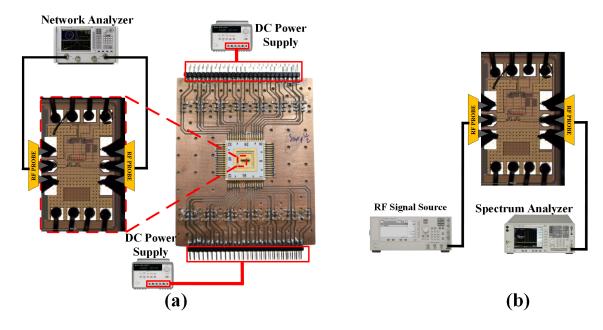

| Figure 3.19. The measurement setups of VVA: (a) S-parameter and (b) ${\rm IP}_{1dB}$ |

| Figure 3.20. The linearity measurements of VVA                                       |

| Figure 3.21. The S-parameter measurement results of VVA                              |

| Figure 3.22. The schematic of power combiner                                         |

| Figure 3.23. The simulation results of power combiner. (a) insertion loss            |

| (b) isolation (c) return losses (d) amplitude imbalance                              |

| Figure 3.24. The measurement setup of the designed phase shifter with QAF $$         |

| Figure 3.25. The input and output matchings of phase shifter                         |

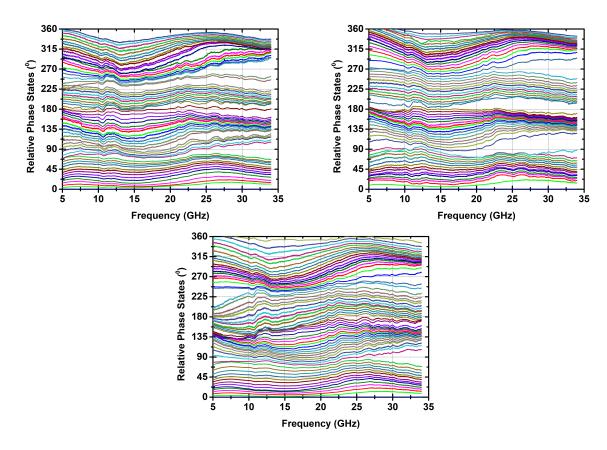

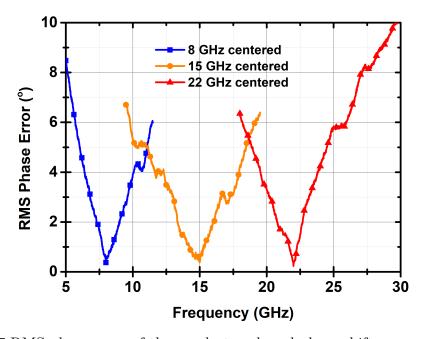

| Figure 3.26. The relative phase states of the quadrature based phase shifter         |

| selected for different center frequencies: 8 GHz (top left), 15 GHz                  |

| (right top) and 22 GHz (bottom)                                                      |

| Figure 3.27. RMS phase error of the quadrature based phase shifter                   |

| Figure 3.28. The amplitude response of the quadrature based phase shifter            |

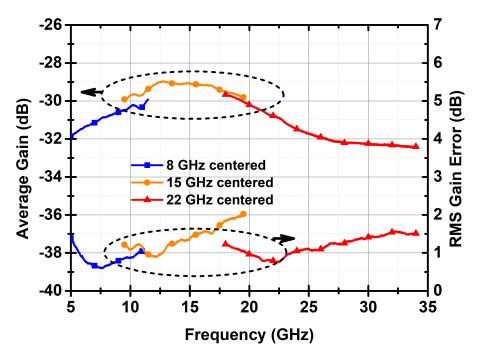

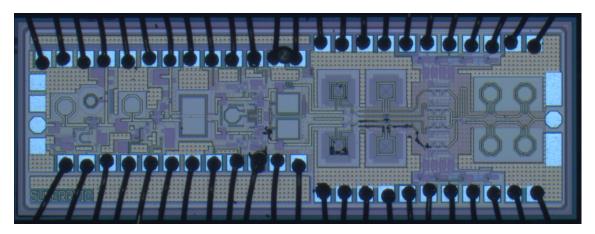

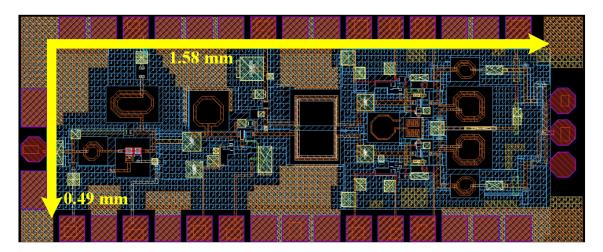

| Figure 3.29. The micrograph of the receiver                                          |

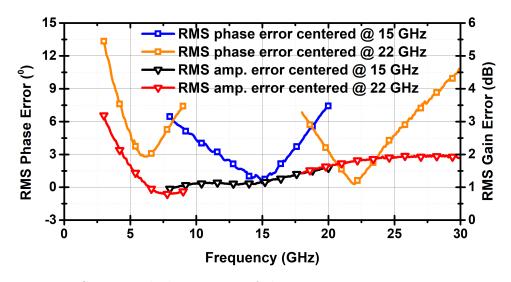

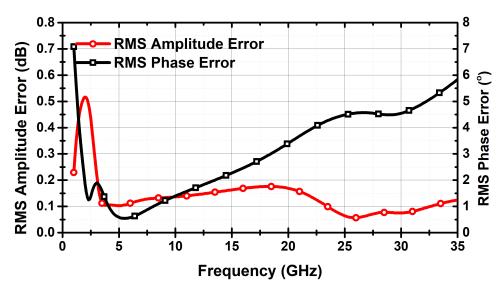

| Figure 3.30. RMS gain and phase errors of the receiver                               |

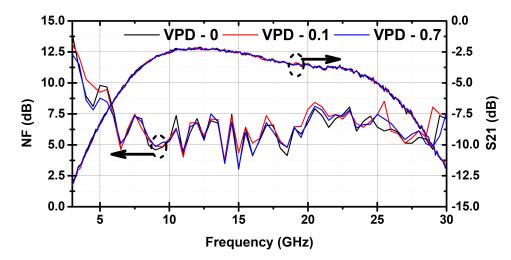

| Figure 3.31. The NF and gain performance of the receiver                             |

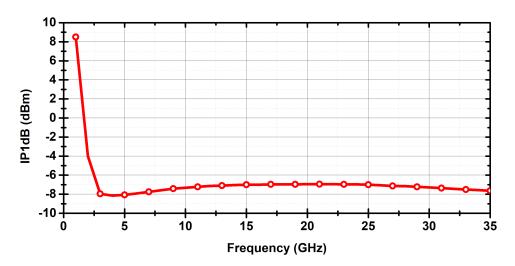

| Figure 3.32. The $IP_{1dB}$ of the receiver                                          |

| Figure 3.33. The IIP3 of the receiver                                                |

| Figure 3.34 The block diagram of the second receiver chain                           |

| Figure 3.35. The schematic of the designed LNA                                   | 56 |

|----------------------------------------------------------------------------------|----|

| Figure 3.36. The layout of the designed LNA                                      | 57 |

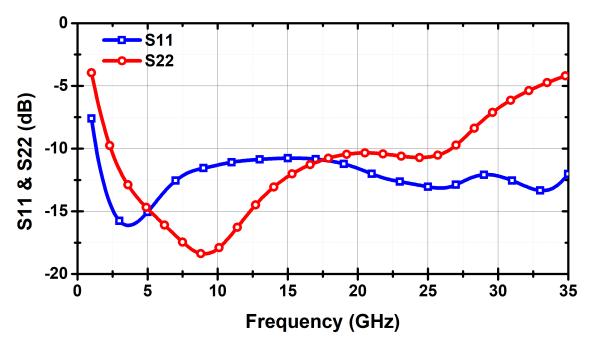

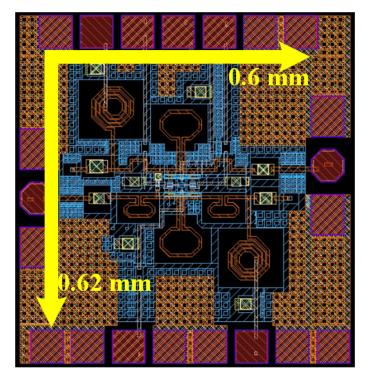

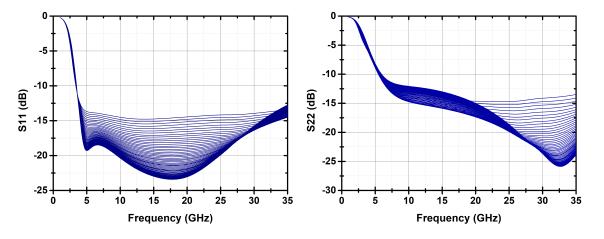

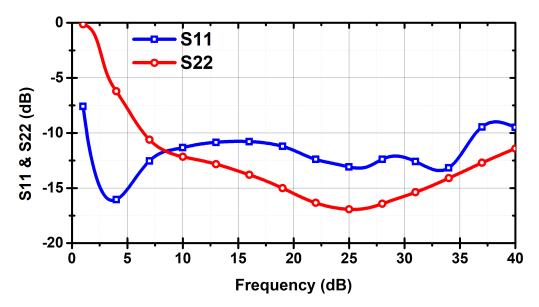

| Figure 3.37. The input and output matchings of the designed LNA                  | 57 |

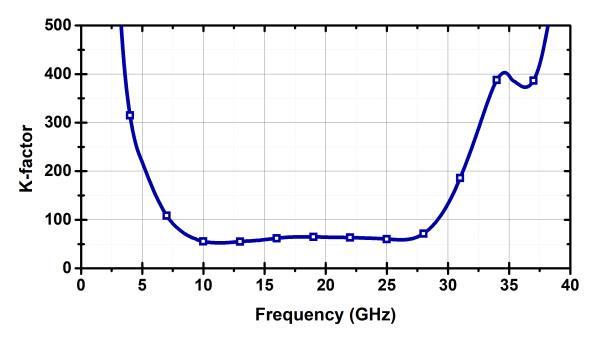

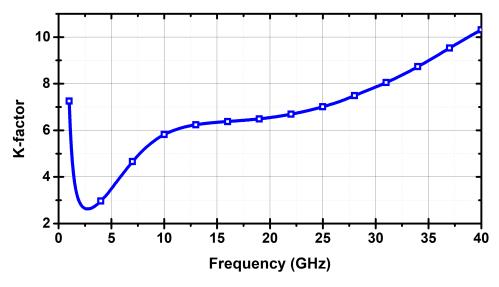

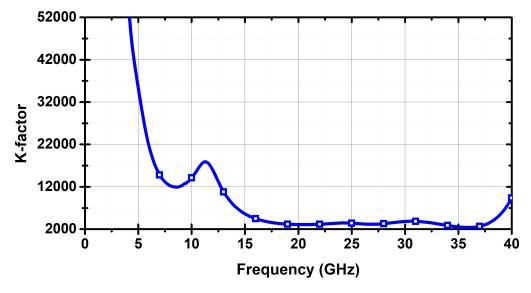

| Figure 3.38. Simulated K-factor results for the stability of the LNA             | 58 |

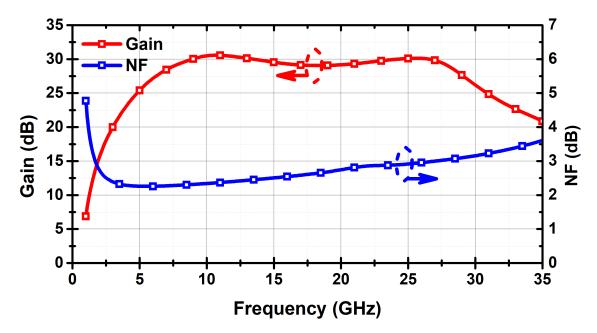

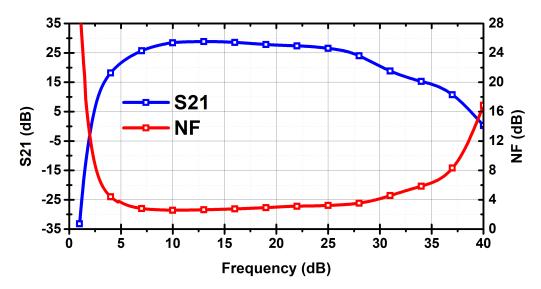

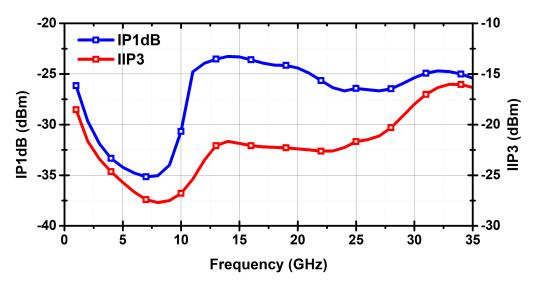

| Figure 3.39. The gain and NF performance of the designed LNA                     | 58 |

| Figure 3.40. The $IP_{1dB}$ (left) and $IIP_{3}$ (right) of the designed LNA     | 59 |

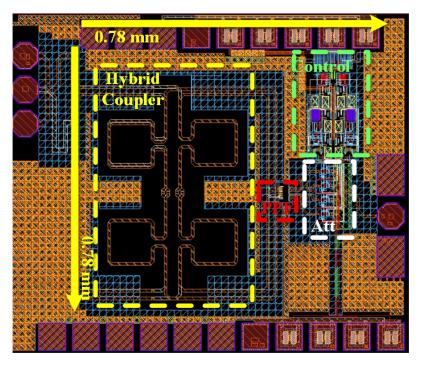

| Figure 3.41. The schematic of the designed coupler based phase shifter           | 59 |

| Figure 3.42. The 3D view (left), and the phase and amplitude errors (right)      |    |

| of I/Q generation network                                                        | 60 |

| Figure 3.43. The schematic of the designed VVA: (a) VVA core, (b) atten-         |    |

| uation loop                                                                      | 61 |

| Figure 3.44. The effect of the attenuation compensation circuitry on the         |    |

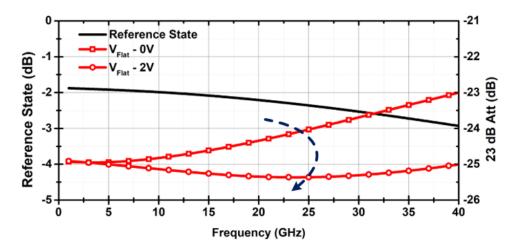

| 23-dB attenuation state                                                          | 61 |

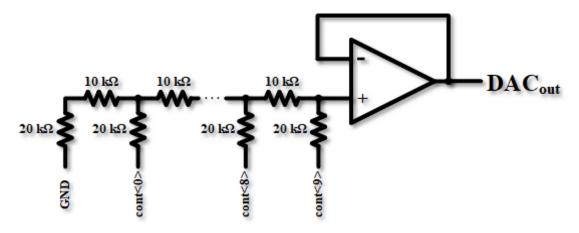

| Figure 3.45. The schematic of 10-bit R-2R DAC                                    | 62 |

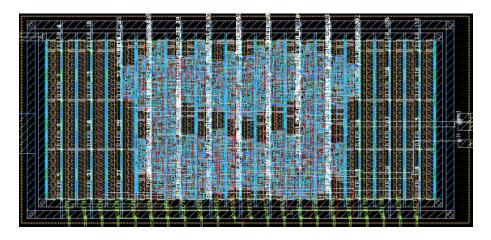

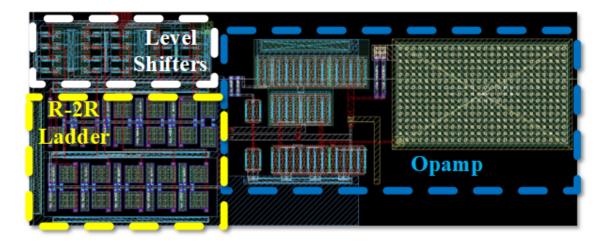

| Figure 3.46. The layout of the designed SPI                                      | 63 |

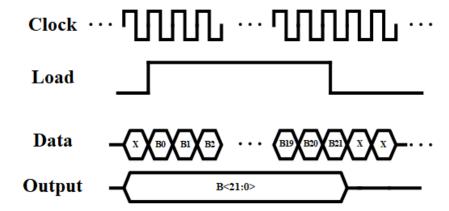

| Figure 3.47. An example for SPI timing diagram                                   | 63 |

| Figure 3.48. The schematic of a level shifter                                    | 64 |

| Figure 3.49. Combined layout of the DAC and level shifters                       | 64 |

| Figure 3.50. The layout of the designed coupler based phase shifter              | 65 |

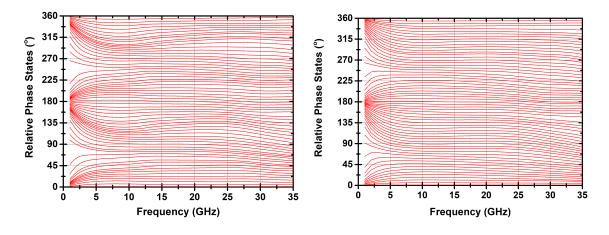

| Figure 3.51. The relative phase states of the designed coupler based phase       |    |

| shifter at reference amplitude level (left) and with 10 dB attenuation           |    |

| (right)                                                                          | 65 |

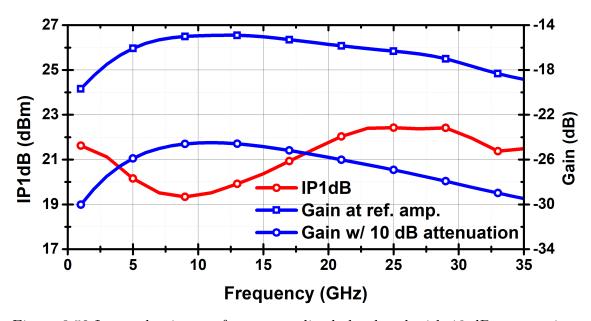

| Figure 3.52. Inserted gain at reference amplitude level and with 10 dB           |    |

| attenuation, and $\mathrm{IP}_{1dB}$ of the designed coupler based phase shifter | 66 |

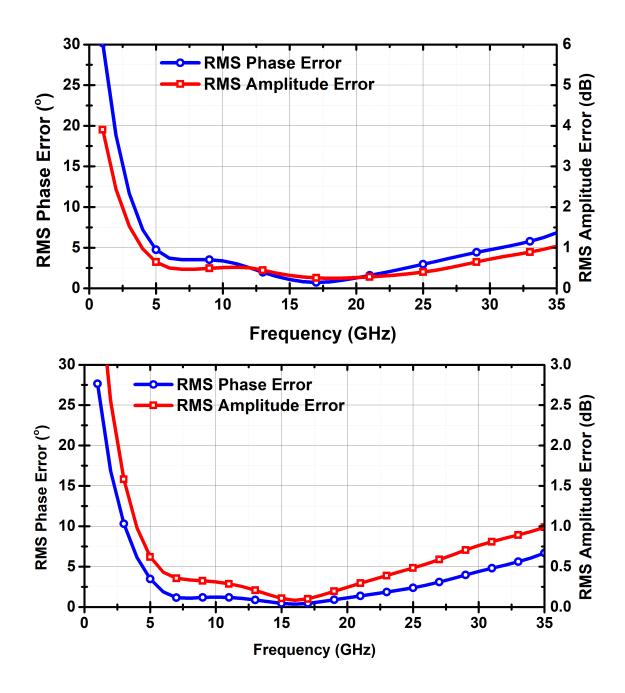

| Figure 3.53. RMS phase and amplitude errors of the designed coupler based        |    |

| phase shifter at reference amplitude level (top) and with 10 dB at-              |    |

| tenuation (bottom)                                                               | 67 |

| Figure 3.54. The schematic of conventional current-steering VGA                  | 69 |

| Figure 3.55. The schematic of the designed VGA                                   | 70 |

| Figure 3.56. The layout of the designed VGA                                      | 70 |

| Figure 3.57. The input (left) and output (right) matchings of VGA                | 71 |

| Figure 3.58. Simulated K-factor for the stability of the VGA                     | 71 |

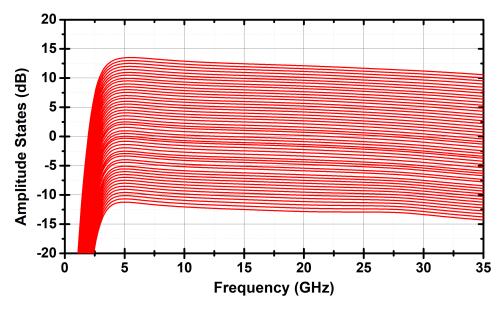

| Figure 3.59. The amplitude states of the designed VGA                            | 72 |

| Figure 3.60. RMS amplitude and phase errors of the designed VGA                  | 72 |

| Figure 3.61. The $IP_{1dB}$ of the designed VGA                                  | 73 |

| Figure 3.62. The simulated input and output matchings of the wideband            |    |

| receiver                                                                         | 75 |

| Figure 3.63. Simulated K-factor for the stability of the second receiver         | 76 |

| Figure 3.64. The simulated gain and NF of the wideband receiver                  | 76 |

| Figure 3.65. The simulated $IP_{1dB}$ and $IIP_{3}$ of the wideband receiver      | 77 |

|-----------------------------------------------------------------------------------|----|

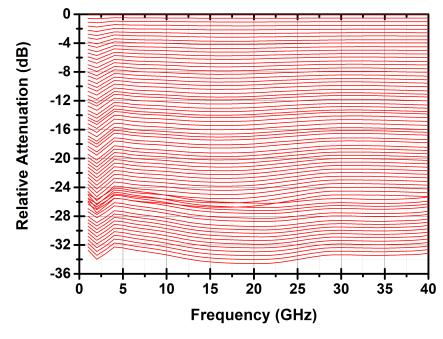

| Figure 3.66. The simulated relative attenuation states of the wideband re-        |    |

| ceiver                                                                            | 77 |

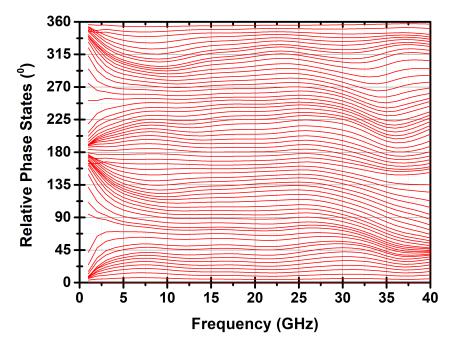

| Figure 3.67. The simulated relative phase states of the wideband receiver $\dots$ | 78 |

| Figure 3.68. The simulated RMS phase and amplitude errors of the wide-            |    |

| band receiver                                                                     | 78 |

| Figure 3.69. The simulated average group delays of 64-phase states, and           |    |

| average group delay variation among 64 phase states                               | 79 |

# LIST OF ABBREVIATIONS

| ADC Analog-to-Digital Converter                                |

|----------------------------------------------------------------|

| CB Common-Base                                                 |

| CE Common-Emitter                                              |

| CMRR Common Mode Rejection Ratio                               |

| FSPL Free Space Path Loss                                      |

| GaAs Gallium Arsenide                                          |

| <b>GEO</b> Geostationary Earth Orbit                           |

| HD High-Definition                                             |

| IC Integrated Circuit                                          |

| IIP3 Input Referred Third-Order Intercept Point                |

| IL Insertion Loss                                              |

| IM3 Third-Order Inter-Modulation Product                       |

| InP Indium Phosphide 5                                         |

| $\mathbf{IP}_{1dB}$ Input 1-dB Compression Point               |

| ITU-R International Telecommunication Union Radiocommunication |

| LEO Low-Earth Orbit                                            |

| LNA Low-Noise Amplifier                                        |

| LSB Least-Significant Bit                                      |

| MEO Medium Earth Orbit                                         |

| MIM Metal-Insulator-Metal                                      |

| MIMO Multiple-Input-Multiple-Output                                 |

|---------------------------------------------------------------------|

| NF Noise Figure                                                     |

| Opamp Operational Amplifier                                         |

| PPF Poly-Phase Filters                                              |

| QAF Quadrature All-Pass Filter                                      |

| RF Radio Frequency                                                  |

| RMS Root Mean Square                                                |

| SATCOM Satellite Communication                                      |

| SLL Side-Lobe Level                                                 |

| SMS Short Message Service                                           |

| SoC System-on-Chip                                                  |

| SOLT Short-Open-Load-Thru                                           |

| SPI Serial-to-Parallel Interface                                    |

| T/R Transmit/Receive                                                |

| TTD True-Time Delay                                                 |

| TUBITAK Turkish Scientific and Technology Research Institution viii |

| UHD Ultra High Definition                                           |

| VGA Variable Gain Amplifier                                         |

| VVA Voltage-Variable Attenuator                                     |

#### 1. INTRODUCTION

Since the invention of cell phones, successive generations of wireless communication technologies has been part of our daily life. Each successive generation has consistently aimed for, and achieved, higher data rates, as illustrated in Fig. 1.1 (Al Mtawa, Haque & Bitar, 2019). These enhanced data rates have opened up the way for more sophisticated and high-quality applications. For instance, the 2G introduced short message service (SMS) whereas video call was enabled with the 3G. As a consequence, the expected application domains for subsequent generations have become significant drivers for technological advancements. For context, current high-definition (HD) video streaming demands bandwidths between 1-5 Mbps, but it's projected that 16K high-definition streaming will require a much more high data rate of 100-500 Mbps (Clemm, Vega, Ravuri, Wauters & Turck, 2020). Sectors such as healthcare, immersive Ultra High Definition (UHD) and three-dimensional (3D) video services, augmented reality, and smart homes highlight the transformative potential of 5G technology (Xiang, Zheng & Shen, 2016; Yifei & Longming, 2014). On top of the growing bandwidth demand, the number of internet users has been gradually increasing from 1 billion (16% of internet users) in 2005 to 5.5 billions (68% of internet users) in 2024 as shown in 1.2.

|    | Network<br>nology | Theoretical<br>Bandwidth | Practical<br>Bandwidth                      |

|----|-------------------|--------------------------|---------------------------------------------|

| 2G | GPRS              | 50 kbps                  | 40 kbps                                     |

| 20 | EDGE              | 1 Mbps                   | 500 kbps                                    |

|    | WCDMA             | 384 kbps                 |                                             |

| 3G | HSPA              | 7.2 Mbps                 | 4.3 Mbps                                    |

|    | HSPA+3            | 21.6 Mbps                | 7.3 Mbps                                    |

|    | LTE               | 150 Mbps                 | 18.6 Mbps<br>downlink;<br>9 Mbps for upload |

| 4G | LTE-A             | 1 Gbps                   | 30 Mbps downlink;<br>10 Mbps for<br>upload  |

|    | LTE-A<br>Pro      | 3 Gbps                   |                                             |

| 5G |                   | 20 Gbps                  |                                             |

Figure 1.1 Cellular-technology generations in the world-wide market in the past decades (Al Mtawa et al., 2019)

# Individuals using the Internet

Figure 1.2 The number of people using internet in 2005-2024 (ITU, 2025)

The 4G cellular communication systems operates below 6 GHz where the frequency spectrum is excessively dense (Rappaport, Xing, Kanhere, Ju, Madanayake, Mandal, Alkhateeb & Trichopoulos, 2019). To accommodate the requirements of the aforementioned applications and to establish the necessary infrastructure for these domains, the International Telecommunication Union Radiocommunication (ITU-R) has delineated specific criteria. As illustrated in Fig. 1.3, these specifications include: peak data rates of up to 20 Gb/s; a user-experienced data rate of 100 Mb/s; a spectral efficiency threefold that of IMT-Advanced; network energy efficiency improved by a factor of 100 compared to IMT-Advanced; support for mobility speeds up to 500 km/h; nearly 1 million simultaneous connections per km<sup>2</sup>; an area traffic capacity close to 10 Mbit/s/m<sup>2</sup>; and an end-to-end latency of less than 1 ms (ITU-R-M.2083-0, 2015; Navarro-Ortiz, Romero-Diaz, Sendra, Ameigeiras, Ramos-Munoz & Lopez-Soler, 2020).

Shannon's theorem formulates the maximum achievable data rate for a given bandwidth, B, received signal power, S, noise power, N, and temperature, T as in equation (1.1) (Shannon, 1948).

(1.1)

$$C = B \cdot \log(1 + S/N)$$

$$where N = kTB$$

To enhance channel capacity, it is imperative to enlarge the bandwidth, despite the resultant rise in noise levels. Conversely, as indicated by the received signal power,  $P_R$ , formula in equation (1.2), the power decreases with increasing signal frequency, primarily due to the escalation of free space path loss (FSPL) in the transmission

Figure 1.3 IMT-2020 specifications (ITU-R-M.2083-0, 2015)

medium.

$$(1.2) \qquad P_R[dB] = P_T[dB] + G_T[dB] + G_R[dB] - FSPL[dB]$$

$$where \ FSPL = \left(\frac{4\pi df}{c}\right)^2$$

$P_T$ ,  $G_T$ ,  $G_R$ , c, and d are the transmitted signal power, transmitter antenna gain, receiver antenna gain, speed of light, and communication distance, respectively (Balanis, 2016). Thus, when leveraging millimeter waves (mm-waves) to exploit larger bandwidths, one must address the associated rise in attenuation. Strategies such as beamforming and the employment of multiple-input-multiple-output (MIMO), and phased arrays are essential to counteract this heightened attenuation.

# 1.1 Satellite Communication Systems

Another key aspect in communication systems is the covered area by these systems. Only 6% percent of global coverage is provided by terrestrial communication systems (You, Zhu, Qiang, Tsinos, Wang, Gao & Ottersten, 2024). Terrestrial networks fall

short in global coverage since the establishment of communication in environmentally challenging locations such as poles and ocean is extremely hard for terrestrial communication systems. On the other hand, satellite communication (SATCOM) systems offer longer communication distance which enables broader coverage compared to terrestrial networks. The effect of geographical conditions on the communication links in SATCOM is less than terrestrial networks. Moreover, satellite systems has and advantage to support communication links when the communication terminals or targets moves with high speed (You et al., 2024).

Satellites have long been employed to establish communication links between various locations on Earth. SATCOM facilitates global connectivity, particularly in remote and under-served regions. One of its primary application domains is telecommunications, where SATCOM enables services such as broadcast satellite television and radio, as well as internet access in rural areas. Low Earth Orbit (LEO) satellites operate at altitudes ranging from 200 to 2000 km. Due to their lower orbital altitude compared to Medium Earth Orbit (MEO) or Geostationary Earth Orbit (GEO) satellites, LEO systems experience reduced latency and path loss (You et al., 2024). SATCOM is also employed in secure communications for defense purposes, as well as in remote monitoring and navigation systems.

Notable LEO satellite constellations designed for telecommunications include Tele-Sat, Amazon Kuiper, Starlink, and OneWeb. Among these, OneWeb and Starlink utilize carrier frequencies of 12 GHz and 14 GHz for downlink and uplink, respectively, while Amazon Kuiper employs 20 GHz for downlink and 29 GHz for uplink (Lin, Cioni, Charbit, Chuberre, Hellsten & Boutillon, 2021). In addition, other frequency bands such as C-band (4–8 GHz), X-band (8–12 GHz), and Ku-band (12–18 GHz) are commonly used for applications including continuous satellite television broadcasting, weather monitoring, and air traffic control.

Electronically scanned phased arrays are generally more suitable for SATCOM applications than mechanically steered systems, as they enable low-latency communication with a compact and lightweight form factor. Another key advantage of phased arrays is their wide bandwidth, which allows coverage across the C-, X-, Ku-, and Ka-bands employed in SATCOM systems. Previously reported wideband integrated circuits (ICs), such as those in (Hu, Kazan & Rebeiz, 2023; Mondal, Singh, Hussein & Paramesh, 2018), have played a critical role in enabling these systems. Fig. 1.4 illustrates a LEO satellite system employing massive MIMO (You et al., 2024).

Figure 1.4 A LEO satellite system with a massive MIMO (You et al., 2024)

## 1.2 SiGe BiCMOS Technology

IC designs are predominantly based on three major technology platforms: III-V technologies (such as gallium arsenide (GaAs) and indium phosphide (InP)), CMOS technologies, and SiGe BiCMOS technology. III-V technologies offer distinct advantages over the others in terms of higher gain, lower noise figure (NF), and increased output power—parameters that are crucial for RF IC front-ends. For example, GaAs and GaN devices are employed in current E-band transceivers due to their ability to deliver the high output power and linearity required for mobile backhaul systems targeting ranges exceeding 2 km (Preez, Sinha & Sengupta, 2023). Despite their superior performance, III-V technologies suffer from higher defect densities and a greater susceptibility to physical damage, which complicates the fabrication process. Additionally, they are characterized by low yield rates (Cressler & Niu, 2003). These challenges significantly escalate production costs. Consequently, their high cost limits their applicability in industries that demand large-scale manufac-

Figure 1.5 The representation of the energy band diagram of SiGe HBT (top) and Si BJT (bottom) (Cressler, 2007)

turing. Furthermore, integration of III-V technologies with other platforms is not feasible, necessitating the design of each sub-block on separate ICs to achieve adequate system-level performance. Nevertheless, their high output power makes them suitable for high-power applications, such as base stations.

Si is one of the most abundant elements on Earth. The ability to produce defect-free, large-diameter Si wafers contributes to a higher number of ICs per wafer. Owing to these attributes, CMOS technologies offer the lowest cost among the available semi-conductor technologies (Cressler & Niu, 2003). In recent years, significant advancements in CMOS technologies—particularly in RF performance metrics such as  $f_T$ ,  $f_{max}$ , and  $NF_{min}$ —coupled with improvements in digital circuitry, including digital signal processing and data converters, have enabled the development of System-on-Chip (SoC) solutions based on single-chip architectures for complex transceivers (Preez et al., 2023). However, these technologies are subject to considerable process variations. Specifically, MOS devices are well known for their modeling challenges (Preez et al., 2023). Variations in parasitic capacitance and resistance can alter circuit performance, thereby introducing reliability concerns for these technologies.

SiGe BiCMOS technology emerged as an enhancement to Si-based technologies through the application of bandgap engineering. In this process, a SiGe alloy is grown epitaxially. The bandgap energies of Si and Ge are 1.12 eV and 0.66 eV, respectively. Increasing the Ge content leads to a reduction in the bandgap energy of the alloy. A smaller bandgap enhances electron injection efficiency within the device, thereby resulting in a higher current gain, denoted as Beta. Furthermore, the Ge composition is introduced in a graded profile, as illustrated in Fig. 1.5, rather than being kept constant. This graded profile creates a built-in electric field

that accelerates minority carriers in the base region, effectively reducing their base transit time,  $\tau_b$ .

Although forming a graded SiGe alloy in the base region increases fabrication complexity and cost, the overall manufacturing expense remains significantly lower than that of III-V technologies. Unlike III-V technologies, SiGe processes are not hindered by low yield, and they exhibit greater resilience to process variations than CMOS technologies. The performance characteristics of SiGe technology rival those of III-V technologies. The impact of these enhancements on a pure Si wafer is reflected in performance metrics such as  $f_T$ ,  $f_{max}$ , and  $NF_{min}$ . The parameters  $f_T$ and  $f_{max}$  are critical figures of merit that define the frequency limits of an electronic device. Specifically,  $f_T$  denotes the frequency at which the short-circuit current gain drops to unity. The expression for  $f_T$  is provided in equation (1.3), where  $\tau_b$  and  $\tau_c$  represent the base and collector transit times,  $g_m$  is the transconductance of the device,  $C_{\pi}$  and  $C_{\mu}$  are the base-emitter and base-collector capacitances, respectively, and  $r_e$  and  $r_c$  denote the emitter and collector resistances (Cressler, 2007). While  $f_T$ can be adjusted during the design phase—since  $g_m$  and the capacitances are dependent on biasing conditions and device dimensions—the transit times are inherently determined by the fabrication process. The reduced base transit time resulting from graded Ge doping directly contributes to an increase in  $f_T$ , as indicated by equation (1.3).

(1.3)

$$f_T = \frac{1}{2\pi} \left( \tau_b + \tau_c + \frac{1}{g_m} \left( C_\pi + C_\mu \right) + \left( r_e + r_c \right) C_\mu \right)^{-1}$$

The other critical frequency parameter,  $f_{max}$ , represents the maximum oscillation frequency. Its formulation is given in equation (1.4), where  $r_b$  denotes the intrinsic base resistance. An enhancement in  $f_T$  directly contributes to an increase in  $f_{max}$ , as the two are proportionally related. By adjusting the Ge grading profile within the base region, higher doping concentrations can be achieved. This modification leads to a reduction in the intrinsic base resistance, thereby enabling higher values of  $f_{max}$  without compromising current gain.

Conversely, in conventional Si BJTs, reducing the intrinsic base resistance can also be achieved by increasing the doping concentration in the base region. However, this approach comes at the cost of diminished current gain. Therefore, SiGe technology offers a favorable trade-off by enabling lower base resistance while preserving performance metrics critical to high-frequency operation.

$$f_{max} = \sqrt{\frac{f_T}{8\pi C_\mu r_b}}$$

The last of the previously mentioned figures of merit is the minimum achievable noise figure,  $NF_{min}$ . Its analytical expression is provided in equation (1.5), where  $\beta_{DC}$  denotes the DC current gain,  $J_c$  is the collector current density, and n represents the emitter-base junction ideality factor. Similar to the case of  $f_T$ , the designer retains a degree of control over  $NF_{min}$  by adjusting parameters such as  $J_c$  and  $\beta_{DC}$ . However, intrinsic resistances and the threshold voltage are determined by the fabrication process and are therefore beyond the designer's control.

A key advantage of SiGe HBTs over conventional Si BJTs is the ability to reduce the intrinsic base resistance,  $r_b$ , without degrading the current gain. This reduction leads to an improvement in  $NF_{min}$ . Moreover, it is generally observed that an increase in  $f_T$  contributes to a corresponding decrease in  $NF_{min}$ .

(1.5)

$$NF_{min} = 1 + \frac{n}{\beta_{DC}} + \sqrt{\frac{2J_c}{V_t}(r_e + r_b)\left(\frac{f^2}{f_t^2} + \frac{1}{\beta_{DC}}\right) + \frac{n^2}{\beta_{DC}}}$$

Table 1.1 Performance comparison of numerous device technologies for radio frequency integrated circuits (Preez et al., 2023)

| Technology            | IC Cost                                                                                        | Integration                                                                                                                                 | RF<br>Performance                                                                                                     | Target products                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| GaAs pHEMT<br>/ mHEMT | High RF modules;<br>requires multi-chip<br>approach                                            | Poor                                                                                                                                        | Excellent, preferred for many RF applications                                                                         | PA, LNA, complete<br>RF modules                                                                                            |

| GaN HEMT              | Relatively new<br>technology                                                                   | Poor                                                                                                                                        | Higher $P_{sat}$ but<br>worse linearity vs. GaAs                                                                      | Future PA, LNA                                                                                                             |

| InP pHEMT             | Generally more than<br>GaAs competitors                                                        | Poor, RF circuits are<br>highly complex                                                                                                     | Better $f_T$ , $f_{max}$ versus GaAs                                                                                  | Defense systems                                                                                                            |

| SiGe                  | Lower, function of<br>production volume,<br>comparable cost for<br>small-volume production     | Good, but not suited for A/D and baseband integration within SoCs                                                                           | High $f_T$ , $f_{max}$ ,<br>decent phase noise performance<br>& low-loss BEOL <sup>3</sup><br>layer stackup           | Medium to high-power<br>mm-wave transceivers ICs                                                                           |

| SiGe BiCMOS           | Lower than competitors,<br>but depending on production<br>volume; SoCs result in<br>good yield | Excellent integration with wide range of logic, good power consumption for A/D and D/A converters                                           | High $f_T$ , $f_{max}$ , decent phase noise performance & low-loss BEOL layer stackup                                 | Medium to high-power<br>mm-wave transceivers,<br>can readily integrate<br>with PLLs and A/D<br>converters                  |

| RF CMOS               | Mm-wave expansion of<br>digital CMOS, requires<br>advanced lithography<br>and costly NRE       | Facilitates high-density<br>digital circuitry integrated<br>with RF; SoC integration<br>possible with digital baseband<br>and memory blocks | Transistor $f_T$ , $f_{max}$ can reach mm-wave operation, but requires low breakdown voltages and miniaturized nodes  | Transceivers with A/D, PLL,<br>amplifier blocks with<br>digital control, well-suited<br>for lower-performance applications |

| CMOS FDSOI            | Lowest supply voltage<br>and<br>power consumption                                              | Can integrate with high-density<br>mixed-signal SoCs, relatively<br>low power requirement for<br>crossing chip boundaries                   | Substrate engineering can substantially improve RF performance; high $f_T$ , $f_{max}$ , good isolation and linearity | Very high-speed mixed-signal blocks (e.g., SerDes)                                                                         |

A relative performance comparison of various IC technologies is provided in Table 1.1. In summary, III-V technologies demonstrate superior performance characteristics compared to other platforms; however, their high fabrication costs and

low yield rates constrain their use to application-specific designs, such as power amplifiers requiring high output power or low-noise amplifiers (LNAs) demanding extremely low NF. Despite significant advancements in CMOS technology, process variability remains a fundamental limitation. Moreover, operating at large level of V<sub>DS</sub> might lead to a degradation in threshold voltage and transconductance. SiGe HBTs, by contrast, offer higher transconductance, improved 1/f noise characteristics, and greater output power, along with slightly enhanced efficiency relative to MOS devices. RF IC front-ends implemented in SiGe BiCMOS technology present a cost-effective and highly integrable solution, while delivering performance metrics that are comparable to those achieved with III-V technologies.

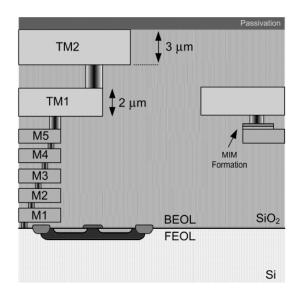

## 1.2.0.1 IHP $0.13~\mu m$ SiGe BiCMOS (SG13S) Tehcnology

In this thesis work, IHP Microelectronics 0.13  $\mu$ m SG13S technology process was preferred. It is reported that IHP's 0.13  $\mu$ m SiGe BiCMOS technology provides HBTs with  $f_t/f_{max}$  of 250/340 GHz and BV<sub>CEO</sub> of 1.7 V. The cross-section of the SG13S process is illustrated in Fig. 1.6. The process consists of five thin (M1-M5) and two thick metal (TM1-TM2) layers. The thick metal layers are located at the top. TM1 and TM2 are generally used to implement high quality-factor inductors and low loss transmission lines. The metal-insulator-metal (MIM) capacitor resides between TM1 and M5. The process offers three different polysilicon resistors (rsil, rppd and rhigh).

### 1.3 Thesis Overview

This thesis aims to design and implement a radio frequency (RF) receiver for SAT-COM applications. Increasing the bandwidth is one of the key enablers to achieve higher data rates. In mm-wave, a larger bandwidth can be allocated. Since LEO SATCOM systems are promising for global connectivity and internet coverage, these SATCOM applications have gathered attention recently. Currently licensed frequency bands for SATCOM reception are C-, X-, Ku-, and Ka-bands. A wideband receiver RF module that covers these SATCOM bands would be cost-efficient. On the other hand, due to orbiting around Earth at more than 200 km altitudes and uti-

Figure 1.6 The cross-section of IHP's 0.13  $\mu m$  SiGe BiCMOS SG13S technology (Özkan, 2020)

lizing mm-wave, the atmospheric path loss is increased. To compensate for increased path loss, one can employ MIMO arrays. In this thesis, two separate single-channel receiver-ICs for SATCOM applications are presented.

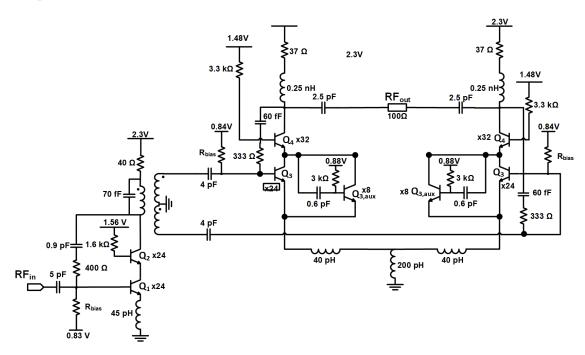

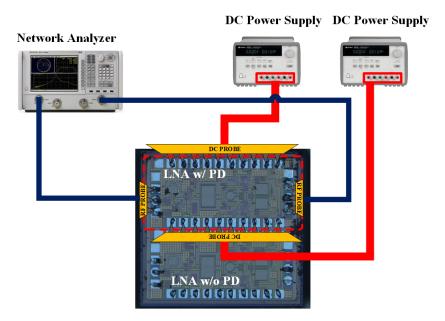

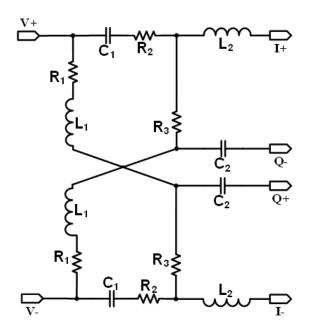

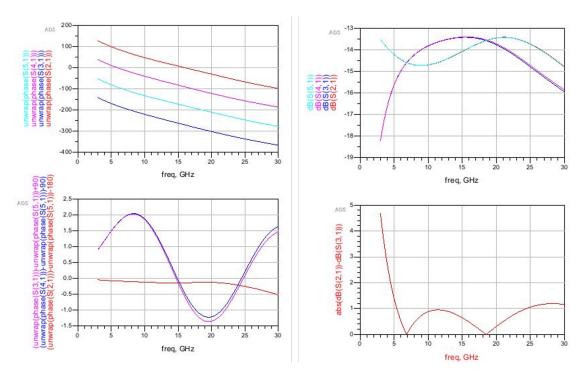

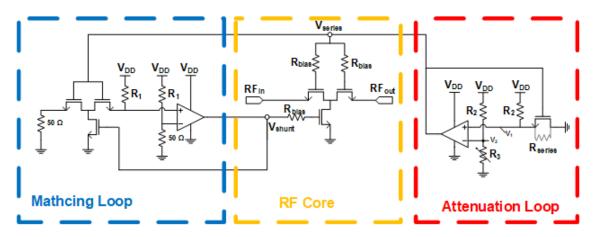

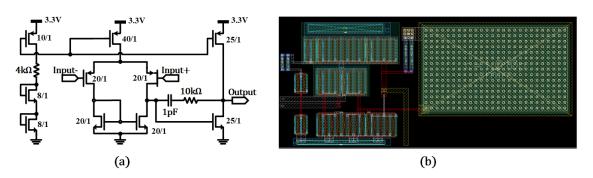

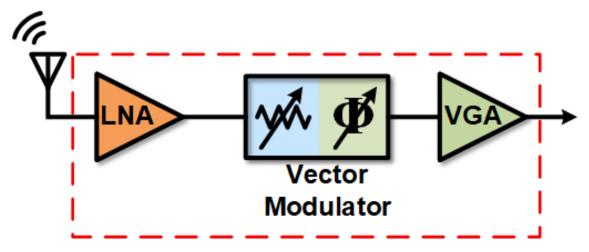

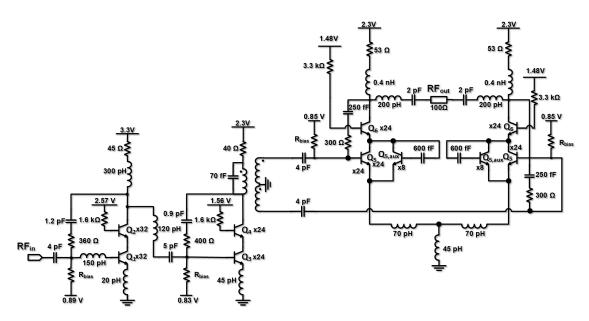

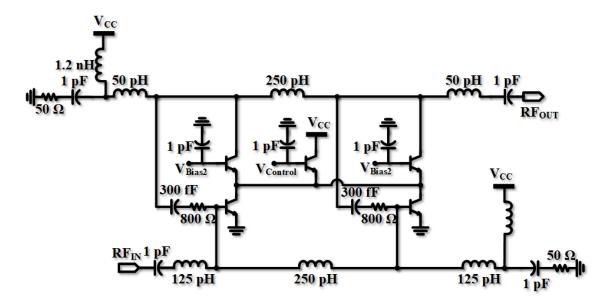

The first receiver consists of an LNA and a 6-bit phase shifter. The designed LNA comprises three stages. The first two stages are single-ended, while the third stage is differential since a passive balun is placed between the second and third stages. Each stage in the designed LNA employs a series RL-loaded cascode topology, which enables flat gain across a wide bandwidth. The last stage of the LNA employs a post-distortion method to enhance IIP3 linearity performance. The phase shifter is based on a passive vector-sum phase shifter topology to achieve high linearity. Analog-controlled voltage variable attenuators with a closed-loop for attenuation control are utilized in weighting the quadrature signals. A wideband Wilkinson power divider is finalized by summing the weighted vectors. In the second receiver, the phase shifter adopts a differential hybrid coupler and  $1^{st}$ -order polyphase filter to enlarge the bandwidth. Also, an RC attenuation compensation network is utilized in the attenuators to reduce amplitude errors in the high attenuation states. The control of the attenuators is switched to digital inputs by employing a 22-bit serial-to-peripheral interface, level shifters, and two 10-bit DACs. Finally, a distributed amplifier-based VGA is introduced in the second receiver as the last stage. The VGA employs RC-feedback to widen the frequency range. The system level schematic simulations of the receiver is presented by connecting the LNA, phase shifter-attenuator, and VGA in that order in ADS environment.

## 1.4 Thesis Organization

The rest of this thesis is organized as follows: Chapter 2 provides fundamental information about phased arrays. Amplitude and phase control blocks in phased arrays are briefly explained with various topologies. The working principle and design vector-sum phase shifter topology are analyzed with the inductance equations. The chapter is followed by a presentation of the current state-of-the-art in wideband receiver ICs.

Chapter 3 contains the analysis, design, simulation and measurements of both wideband receivers for SATCOM applications. This chapter begins with the design procedure of each sub-block; the LNA and phase shifter. After the design procedure, the measurement results are provided for each sub-block. The first receiver, the combination of the LNA and phase shifter, is presented and the measurement results are shown as well. Also, Chapter 3 also covers the design revisions in the LNA and phase shifter in the second receiver, and simulations of each sub-block in the second receiver. Finally, chapter 3 will is concluded with the system level simulations of the second receiver.

The last chapter of this dissertation will summarize the findings and the impacts of the presented works. Moreover, this chapter also opens up a discussion on the limitations and possible solutions to these limitations. A list of future work finalizes the thesis.

#### 2. BACKGROUND

## 2.1 Phased Arrays

A single antenna element operates with a low-directivity characteristic, resulting in omnidirectional radiation with a wide beam. Low directivity leads to lower antenna gain, which affects the link budget. Considering the increased path loss in mm-wave frequencies, high directivity should be required. When multiple antenna elements are arranged in an array configuration, the overall radiation pattern becomes significantly more directive, leading to a narrower main beam. By appropriately controlling the phase of each radiating element—such as by applying a constant phase taper between adjacent elements—the main beam can be electronically steered away from the broadside (normal) direction.

## 2.1.1 Operating Principle

Phased arrays have been employed across various domains, including medical applications (Bucci, Crocco, Scapaticci & Bellizzi, 2016) and automotive radars (Ku, Schmalenberg, Inac, Gurbuz, Lee, Shiozaki & Rebeiz, 2014). By utilizing multiple antenna elements, both the transmitter and receiver antenna gain can be enhanced. Consequently, the attenuation associated with mm-wave usage can be counterbalanced, enabling the establishment of extended communication links.

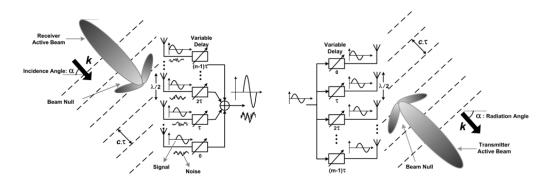

Fig. 2.1 separately illustrates phased array systems in both transmission and reception. The signal intended for transmission, denoted as S(t), is expressed in Eq.(2.1), where v(t) and  $\phi(t)$  symbolize the baseband signal modulating the carrier signal.

Figure 2.1 The operating principle of phased array in reception (left) in transmission (right) (Hajimiri, Hashemi, Natarajan, Guan & Komijani, 2005)

Here,  $\tau$  represents the time delay between successive elements (Natarajan, Komijani & Hajimiri, 2005). Under the narrow-band approximation, it's posited that phase shifts can substitute for time delays. This leads to more compact designs since time delay circuits occupy more area.

(2.1)

$$S(t) = \sum_{n=0}^{n-1} v(t - k\tau) \cos\left(\omega_{RF}t + \phi(t - k\tau)\right)$$

As equation (2.1) indicates the beam direction or angle is controlled by the phase of each element. The incremental phase shift between each element in an array along with the distance between the elements determines the angle between the main beam and the elements. To obtain the highest possible directivity, the distance between radiating antenna elements should be  $\lambda/2$ .

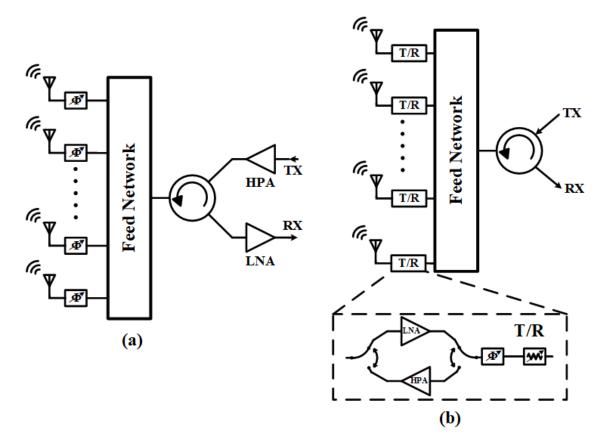

### 2.1.2 Phased Array Architectures

Phased arrays have been classified as active and passive depending on whether each element has its own RF chain or not. In passive phased arrays, each element has only its phase shifter as shown in Fig. 2.2a. The transmitter and receiver utilize separate central amplifiers. Due to losses in the feed network and phase shifter, the central amplifier in the transmitter must provide very high output power, and the central amplifier in the transmitter must perform high gain while introducing very low noise. Most of the passive phased arrays do not offer amplitude control (Parker & Zimmermann, 2002). Active phased arrays contain an RF chain for each antenna element. The RF chain includes an LNA, a PA, a phase shifter, RF switches, and a

variable gain amplifier (VGA)/attenuator. An example of a transmit/receive (T/R) module is presented in Fig. 2.2b.

Figure 2.2 (a) Passive and (b) active phased array architectures

The main advantage of passive phased arrays is very low power consumption compared to active phased arrays since there are only central amplifiers. Architectural simplicity makes passive phased arrays less expensive. On the other hand, active phased arrays offer better performance in terms of high gain and output power, lower NF. Due to element-wise amplitude and phase control in active phased arrays, beam steering is more precise. Another advantage of active phased arrays is the scalability. We can increase the number of antenna element since each element has its own RF chain. However, passive phased arrays suffer from increased losses introduced by the feed network as the number of element increased.

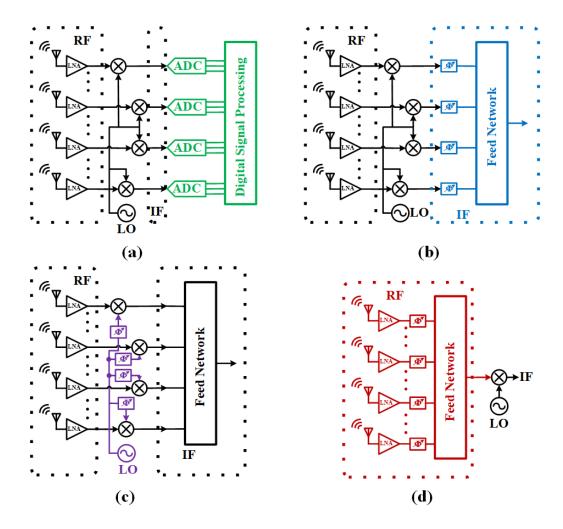

Controlling the phase and amplitude of each element for the beam direction or angle is referred as beamforming. Phased arrays are also classified with respect to their beamforming methodology. The beamforming in phased arrays is divided into analog or digital depending on where the phase and amplitude of an element is controlled. In the digital beamformers, the phase shift is determined at the baseband whereas the analog beamformers gives phase shift in the transmitter/receiver (transceiver) part as shown in Fig. 2.3. In digital beamforming, each transceiver element has its

own mixer and Analog-to-Digital converters (ADCs). Since the signal combining comes after ADCs, the ADCs must have high linearity (Kalyoncu, 2019). The high linearity requirement increases the power consumption dramatically. On the other hand, more precise control over phase and amplitude can be achieved at the baseband compared to in the RF path (Yang, Yu, Lan, Zhang, Zhou & Hong, 2018; Zhang, Wu & Fang, 2011). Analog beamformers offer lower power consumption by leveraging the employment of one ADC after signal combining. Moreover, the phase shifter in RF domain brings either high loss or low linearity performance depending on the phase shifter topology. Analog beamformers do not support multiple beams so, the number of users are limited. Unlike analog beamformers, digital beamformers can support multiple beams at a time. As a result, digital beamformers can support any number of user terminal, only limited by the number of elements in array. A third beamforming option exists as the hybrid beamforming which combines narrow beams shape of analog beamforming for longer distance with simplicity in design and performance of digital beamforming (Li, Wang, Li, Liu & Zhou, 2019; Maneiro-Catoira, Brégains, García-Naya & Castedo, 2018; Roth, Pirzadeh, Swindlehurst & Nossek, 2018).

Figure 2.3 Beamformers, analog beamformer (left) digital beamformer (right) (Puglielli, Townley, LaCaille, Milovanović, Lu, Trotskovsky, Whitcombe, Narevsky, Wright, Courtade, Alon, Nikolić & Niknejad, 2016)

There are several phase shifting methods in beamformers as shown in Fig. 2.4. LO phase shifting is a phase shifting that the phase shifting occurs in LO path. In RF and IF phase shifting, the phase shifting is performed before and after the downconversion in a receiver chain, respectively. In digital phase shifting, digital signal processing or ADC/DAC are responsible for phase shifting on digital I/Q samples. Among the phase shifting methods, contemporary phased arrays have been employed RF phase shifting since single mixer employed in RF phase shifting removes complex LO feed networks and degradation due to these feed networks (Kalyoncu, 2019).

Figure 2.4 RF phase shifting methods (a) digital, (b) IF, (c) LO, and (d) RF

## 2.2 Phase and Amplitude Control Blocks

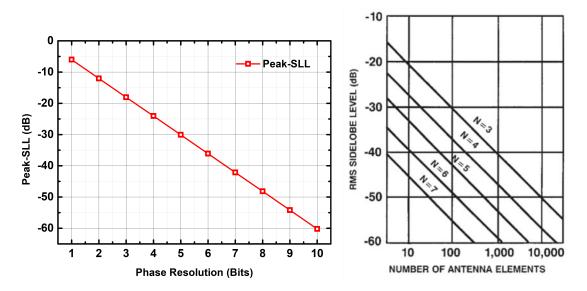

Beamforming has been a focal point of research over the years, especially given its significant role in fulfilling the high standards of 5G applications. As underscored by equation 2.1, the precise control of phase and amplitude is essential for the constructive combination of incoming signals and for steering the beam direction. Furthermore, the suppression of the side-lobe level (SLL) is intricately linked to phase resolutions. Figure 2.5 elucidates that with increased phase resolution, there is a concomitant decrease in SLL. Another critical insight derived from Fig. 2.5 is the inverse relationship between phase resolution and the required number of antennas for achieving a target SLL. A finer phase resolution implies fewer necessary antennas, consequently leading to reductions in system size and cost (Mailloux, 2017). Along with the phase resolution, the resolution of the amplitude control should be high to adjust the SLL and null points in the beamforming (Roques, Cazaux & Pouysegur,

1990; Walker, 1994). Therefore, amplitude and phase control blocks are crucial for beamforming.

Figure 2.5 Peak SLL due to N bits of quantization with respect to the number of phase control bits (left) and required antenna number to reach the same RMS side-lobe level with different phase resolutions (right) (Mailloux, 2017)

## 2.2.1 Attenuators and VGAs

VGAs and attenuators are employed in transceivers for amplitude control purposes. The main objective of these amplitude control blocks is to adjust the signal's power level by introducing the same phase shift. However, the amplitude control blocks insert different phase shifts across different amplitude levels due to parasitic effects in the transistors and layouts. Similarly, the amplitude levels vary with the frequency. Root mean square (RMS) amplitude and phase errors are parameters of an amplitude control block utilized to show error performance. RMS amplitude and phase error formulas are given in (2.2) and (2.3), respectively.

(2.2)

$$RMS - Amplitude \ Error(f) = \sqrt{\frac{1}{N} \sum_{n=1}^{N} (\Delta \Phi_n(f))^2}$$

(2.3)

$$RMS - Phase Error(f) = \sqrt{\frac{1}{N} \sum_{n=1}^{N} (\Delta \epsilon_n(f))^2}$$

VGAs can provide gain to compensate the losses of other blocks in the transmitter or receiver chain. The cost of gain that VGA brings is the deterioration in linearity. On the other hand, attenuators, often being passive structures, inherently possess a higher power handling capability. A noteworthy advantage of attenuators is their zero DC power consumption, which can significantly relax the other sub-blocks specifications. Furthermore, attenuators can operate over expansive bandwidths, often exceeding 10 GHz (Kandis, Burak, Kana, Yazici & Gurbuz, 2022; Ku & Hong, 2010; Song, Cho & Cressler, 2018). The attenuation range of attenuators is larger than VGAs since the large phase variation in low gain settings occurs in VGAs.

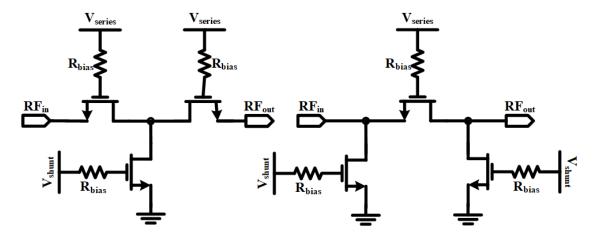

Attenuators can be classified as digital or analog controlled attenuators. The former is commonly realized using switched- $\Pi/T$  type resistive networks, as depicted in Fig. 2.6 (Kandis et al., 2022; Ku & Hong, 2010; Song et al., 2018; Yuan, Mu & Guo, 2018). One significant advantage of digitally-controlled attenuators is their independence from ADCs for operation.

Figure 2.6 Attenuator networks

The operation principle of digital-step attenuator is the selection between reference path and lossy path. When Q1 is ON and Q2 is OFF in Fig. 2.6, Q1 provides a direct connection between  $RF_{in}$  and  $RF_{out}$ , constituting the reference path. Conversely, when Q2 is ON and Q1 is OFF, the T-type resistive network occurs between  $RF_{in}$  and  $RF_{out}$ , delineating the lossy path.

The bandwidth of these attenuators is largely dependent on the parasitic capacitance of the OFF-state switches. Concurrently, the loss experienced in the reference path, commonly termed insertion loss (IL), hinges on the  $R_{ON}$  resistance of the series switch. In large attenuation networks, the phase variation becomes significant. To counteract this, R-L-R low pass network is employed as in (Kandis et al., 2022).

To increase attenuation range, the number of utilized networks should be increased which causes higher IL and larger area. The study presented in (Kandis et al., 2022) details a 6-bit, 24 dB digital step attenuator designed using 130nm SiGe BiCMOS technology. It operates over a frequency range from DC to 25 GHz, and the input 1-dB compression point (IP<sub>1dB</sub>) for this attenuator exceeds 20 dBm. The RMS phase error is  $2.4^{\circ}$ . Nevertheless, it exhibits an insertion loss greater than 9 dB, and its overall area measures  $1.1 \text{ mm}^2$ . Another digital step attenuator reported in (Yuan et al., 2018) has 31.5 dB attenuation range and 0.5 dB resolution. This work introduces two separate attenuators tailored for specific frequency bands: one covering the 15-18 GHz range and the other spanning 19-24 GHz. Combined, these attenuators occupy a total area of  $1.07 \text{ mm}^2$ .

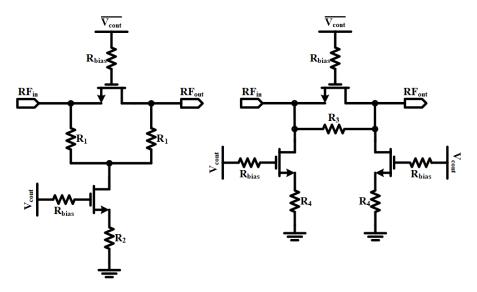

In prevalent analog-controlled attenuators, the resistance elements within the resistive  $\Pi/T$ -type networks are supplanted with NMOS devices. This design allows for control over attenuation by modulating the gate voltage, which in turn adjusts the channel resistance of the NMOS devices, as expressed in equation (2.4) (Dogan, Meyer & Niknejad, 2004,0). A distinct advantage of analog-controlled attenuators is their compactness, stemming from a compact design featuring merely three transistors. This simplicity also facilitates a straightforward design methodology. However, a notable drawback is their dependency on ADCs for system integration, a requirement not present in digital-step attenuators.

(2.4)

$$R_{channel} = \frac{1}{\mu_{n,p} C_{ox} \frac{W}{L} \left( V_{|GS|} - V_T \right)}$$

(Dogan et al., 2005) reported a voltage variable attenuator (VVA) which has 42 dB attenuation range and 0.9-3.5 dB insertion loss. Fig. 2.7 demonstrates the schematics of conventional VVAs.  $IP1_{dB}$  of this VVA is measured at 2.5 dBm while occupying 0.7 mm<sup>2</sup>. The operation frequency is DC-2.5 GHz. A VVA operates DC to 10 GHz (Dogan et al., 2004). The insertion loss is 0.8-3 dB and the attenuation range is 35 dB.  $IP1_{dB}$  is measured at 5 dBm while occupying 0.29 mm<sup>2</sup>. Another VVA is presented in (Wagner, Mayer, Wickert, Wolf, Joram, Strobel & Ellinger, 2013) with different topology. In this topology, input and output are differential signals. By adjusting channel resistances of the series and shunt devices, the attenuation is controlled. The purpose of the series devices is as the same as in  $\Pi/T$ -type networks whereas shunt devices determine the controlled leakage between the differential signals. The work in (Wagner et al., 2013) reported 3.6 dB insertion loss and 51.7 dB maximum attenuation. The phase variation is measured as 4°. The

total area is 0.7 mm<sup>2</sup>. However, this topology requires one balun at each input and output port to convert differential to single-ended for single-ended designs.

Figure 2.7 The schematics of conventional VVAs

#### 2.2.2 Phase Shifters

Phase control in communication systems typically relies on two primary components: true-time delay (TTD) circuits and phase shifters. TTDs are particularly suited for wideband systems as they avoid the beam-squint phenomenon (Ma, Leenaerts & Baltus, 2015). However, these circuits come with inherent drawbacks: they consume substantial area and introduce significant losses in the RF path. Due to these drawbacks, phase shifters often emerge as the more favorable choice over TTDs in many applications.

The main objective of these phase control blocks is to adjust the signal's inserted phase by the circuit without affecting the amplitude level of the input signal. However, the phase control blocks lead to variations in the signal's power across different phase states. Similarly, the inserted phases vary with the frequency. Similar to the amplitude control blocks, RMS amplitude and phase errors are parameters of a phase control block utilized to show error performance. RMS amplitude and phase error formulas are given in (2.2) and (2.3), respectively.

Phase shifters are classified into two categories in terms of DC power consumption: passive or active phase shifters. Former leveraging zero power consumption. Due to being passive structures, passive phase shifters have the capability to handle high powers. However, they introduce high loss and occupy large area which increases the cost of the system. Similar to digital step attenuators, higher phase resolution

requires additional networks which increase overall area.

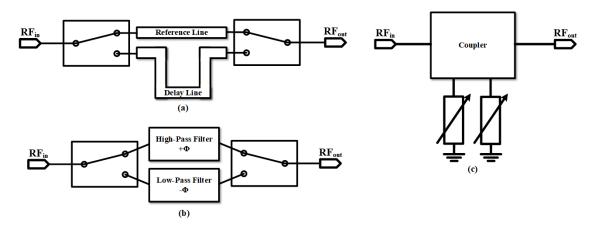

In the literature, several passive phase shifter works have been reported (Basaligheh, Saffari, Rasti Boroujeni, Filanovsky & Moez, 2020; Calışkan, Yazici & Gurbuz, 2021; Garg & Natarajan, 2017; Gong, Cho & Cressler, 2017; Gul, Duong, Kim & Lee, 2013). The schematics of some passive phase shifter topologies are illustrated in Fig. 2.8. (Gul et al., 2013) employs switch-line topology which the phase shift depends on the length difference between the reference line and longer line. In this work, 2-bit switch-line phase shifter with the minimum insertion loss of 8.2 dB is presented between 57-64 GHz in 130 nm CMOS technology. Another passive phase shifter topology is switched-filter type which replaces transmission line in switchline topology with the high-pass and low-pass filters. The phase shifter design in (Calışkan et al., 2021), implemented in 130 nm SiGe BiCMOS technology, integrated with an all-pass network, spans frequencies from 6-25 GHz and occupies 0.48 mm<sup>2</sup>. However, this design suffers a considerable loss of 20.4 dB. To mitigate this pronounced loss, (Gong et al., 2017) replaced the switches with active switches and obtained 11.5 dB gain, albeit at the expense of heightened power consumption of 195 mW. This phase shifter is also realized in 130 nm SiGe BiCMOS technology. In reflection-type passive phase shifters, phase modulation is achieved by modulating the load impedances of the coupler, as detailed in (Basaligheh et al., 2020; Garg & Natarajan, 2017) which are implemented in 65 nm CMOS.

Figure 2.8 The schematics of passive phase shifters: Switched-line (a), Switched-filter (b) and Reflection-type (c) phase shifters

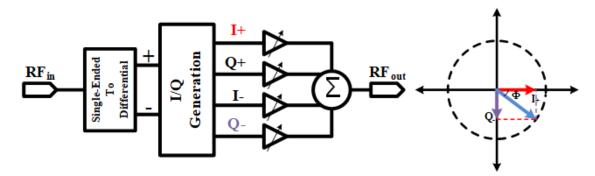

Active phase shifters provide the benefit of high phase resolution while also offering gain, thereby easing the performance requirements of other subsystems in terms of gain, noise etc. Moreover, they can be realized in a compact area. The vector-sum phase shifter topology is predominantly favored for active phase shifters. As depicted in Fig. 2.9, firstly, the single-ended input is converted to differential signals which are fed to I/Q generation network. I/Q network generates four different signals

that are 90° apart from each other. In the final stage, the two of these signals are combined with different weights controlled by the VGAs to obtain desired phase shift. Since the VGAs are analog-controlled, additional control circuit is required.

Figure 2.9 The block diagram of the vector sum phase shifter

There has been reported various active phase shifters in the literature (Cetindogan, Ozeren, Ustundag, Kaynak & Gurbuz, 2016; Kalyoncu, 2019; Kalyoncu, Ozeren, Burak, Ceylan & Gurbuz, 2019). (Cetindogan et al., 2016) achieved 6-bit phase resolution between 9.6-11.7 GHz with RMS phase error lower than 2.8°. Overall insertion loss is 2.5 dB while  $IP1_{dB}$  is -11 dBm. This phase shifter is implemented in 0.25  $\mu$ m SiGe BiCMOS technology.

## 2.3 Existing Literature in Phased Array Systems for Satellite

## Communications

There has been substantial amount of work on phased arrays in SATCOM bands both in academia. (Liu, Li, Li, Deng, Li, Liu & Xiong, 2016) demonstrated a phased array transceiver that operates at X-band, one of the licensed SATCOM bands. In receiver side, the transceiver achieves a gain of 25 dB, an NF of 3 dB, an IP<sub>1dB</sub> of -18 dBm, an rms phase error less than 3.8° with 5-bit phase resolution, and an rms gain error less than 1.2 dB in the frequency range between 9-11 GHz while consuming 352 mW DC power. A 25-30 GHz receiver was realized in 65-nm CMOS technogy (Mondal et al., 2018). The receiver provides 34 dB gain, 7.3 dB minimum NF, -29 dBm IP<sub>1dB</sub> with 27.5 mW DC power consumption. (Xie, Feng, Huang, Zhang, Zhao, Liu, Liu, Li & Wu, 2025) implemented RF phased array receiver front-end in Ku-band for SATCOM applications. 8-channel 64-beam receiver achieves 24.5 dB peak gain within the frequency range of 10-15 GHz. The receiver's amplitude control range is 23.5 dB, exhibiting amplitude control step of 0.5 dB. IP<sub>1dB</sub> of -15.8

dBm is obtained while consuming 465 mW. SATCOM phased arrays has not been a focus in only academia, but also in industry. Axiro F6212 is a Ka-band 16-channel RX active beamforming IC module that operates at 17.7-21.2 GHz, providing 28 dB gain with 26 dB gain control and 0.45 dB gain steps (Renesas Electronics (Axiro), 2025). Phase resolution is 6-bit.

(Sayginer & Rebeiz, 2016) and (Hu et al., 2023) demonstrate wideband operation that covers multiple SATCOM bands in a single IC, which eventually reduce the cost of IC. (Sayginer & Rebeiz, 2016) is an 8-element phased array receiver which operates in 2-16 GHz. In this frequency range, a channel in the receiver performs 4-bit phase control, 3-bit amplitude control with 8 dB, -20 dBm IP<sub>1dB</sub>, 11.5 minimum NF while consuming 250 mW DC power. This works utilizes QPSK modulation to achieve 122.9-Mbaud with an EVM of 6.3%. (Hu et al., 2023) achieves to operate between 3.1-25.5 GHz, covering C-, X-, Ku-, Ka-bands which are the licensed for SATCOM applications. The receiver consists of 16 channels, providing a peak gain of 26.6 dB, an NF of 2-2.4 dB. IP<sub>1dB</sub> performance of this receiver is -50 dBm. The amplitude control range is 25 dB while phase resolution is 5-bit with calibration. DC power consumption per channel is 112.5 mW. This work achieves 16-QAM 400-MBaud modulation with an EVM of 1.13-2.35%.

## 3. WIDEBAND SINGLE-CHANNEL RECEIVER FRONT-ENDS

# FOR C/X/Ku/Ka-BAND SATCOM SYSTEMS

In this chapter, the design, implementation and measurement of each block in the wideband SATCOM receivers. There are two different versions of the single-channel receivers. The first single-channel receiver consists of an LNA and a phase shifter. The design steps, simulation results and measurement results of each block, and the simulation and measurement results of the first receiver channel are provided in this chapter. The second receiver contains the updated block versions of the previous channel along with an additional VGA to increase the amplitude control range and relax the specifications of the phase shifter block. The design steps, simulation results and measurement results of each block in the second receiver channel, and system level simulation results for the second receiver channel are provided in this chapter. Finally, the comparison with similar works from the literature is presented.

## 3.1 Receiver with LNA and Phase Shifter

During the design of a receiver system, key performance metrics include noise figure (NF), gain, linearity, bandwidth, and power consumption. The noise performance of a receiver is critical for maintaining signal sensitivity. In other words, NF is a key performance parameter due to the extremely low power levels of the received signal. As defined by the NF equation given in (3.1), even a small amount of added noise power can render the signal undetectable (Pozar, 2011).

(3.1)

$$F_{total} = F_1 + \frac{F_2}{G_1} + \frac{F_3}{G_1 G_2} \dots$$

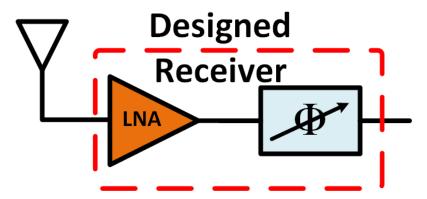

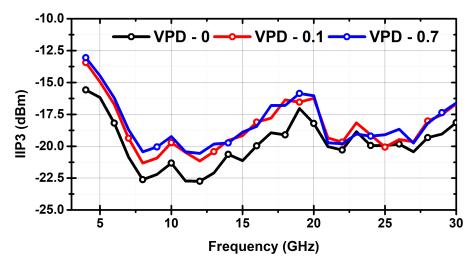

In this equation, F represents the noise factor, G represents the gain of each stage, and N denotes the noise power (including both added and initial contributions). In receiver architectures, the order of sub-blocks plays a crucial role in the overall NF performance of the system. The noise contribution of each sub-block, along with the total noise figure of the receiver system, can be calculated using the equation in (3.1). According to this relationship, the first sub-block in the receiver chain must exhibit very low noise and high gain to suppress the noise contributions of subsequent stages. Therefore, in many receiver systems, a high-gain LNA is positioned as the first block in the chain to achieve improved noise performance and gain. To support the intended number of users and to enable SATCOM applications within the target frequency band, appropriate bandwidth—especially the 3-dB bandwidth—is a critical design parameter. The designed system includes an LNA and a phase shifter as shown in Fig. 3.1. With this sub-block order, the receiver prioritizes NF performance over linearity.

Figure 3.1 The block diagram of the first receiver chain

## 3.1.1 Low Noise Amplifier