## ULTRA-WIDEBAND POWER AND LOW NOISE DISTRIBUTED AMPLIFIERS WITH AREA REDUCTION METHODS

$\begin{array}{c} \text{by} \\ \text{SELİM ARAS YAĞMURLU} \end{array}$

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfilment of the requirements for the degree of Master of Science

Sabancı University June 2025

# ULTRA-WIDEBAND POWER AND LOW NOISE DISTRIBUTED AMPLIFIERS WITH AREA REDUCTION METHODS

| Approved by:                      |

|-----------------------------------|

|                                   |

| Asst. Prof. KORKUT KAAN TOKGÖZ    |

| Prof. İBRAHİM TEKİN               |

| Assoc. Prof. MUSTAFA BERKE YELTEN |

| Date of Approval: July 16, 2025   |

All Rights Reserved

#### ABSTRACT

## ULTRA-WIDEBAND POWER AND LOW NOISE DISTRIBUTED AMPLIFIERS WITH AREA REDUCTION METHODS

#### SELİM ARAS YAĞMURLU

Electronics Engineering, M.Sc. Thesis, July 2025

Thesis Supervisor: Asst. Prof. Korkut Kaan Tokgöz

Keywords: ultra-wideband, distributed amplifiers, transconductance optimization, area reduction, CMOS, low-noise amplifier, power amplifier

Ultra-wideband (UWB) amplifiers are essential components of communication systems, radar, and fiber-optic technologies that require a wide bandwidth and minimal latency. Distributed amplifiers (DAs) effectively manage parasitic capacitances through artificial transmission-line structures, offering inherent broadband performance. However, conventional DAs typically consume large silicon areas due to numerous stages and extensive interconnections, and passives. This thesis introduces increased transconductance bandwidth with a fully-shunt peaking method in cascode and compact inductor-based area reduction methods with decreased quality factor optimization for distributed power amplifiers (DPA) and distributed low-noise amplifiers (DLNA). The proposed DPA achieves an average 13.75 dB gain and stable output power with average of 13.69 dBm across a minimum 70 GHz bandwidth. The DLNA has a noise figure below 6 dB with an average gain of 13.6 dB within the same frequency range. Both designs, implemented in TSMC's 65-nm bulk CMOS technology, outperform literature in noise figure, gain, and output power.

#### ÖZET

## ALAN AZALTMA YÖNTEMLERİYLE ULTRA GENİŞ BANT GÜÇ VE DÜŞÜK GÜRÜLTÜLÜ DAĞITILMIŞ YÜKSELTEÇLER

#### SELİM ARAS YAĞMURLU

Elektronik Mühendisliği, Yüksek Lisans Tezi, Temmuz 2025

Tez Danışmanı: Dr. Öğr. Üyesi Korkut Kaan Tokgöz

Anahtar Kelimeler: ultra-geniş bant, dağıtık amplifikatörler, alan azaltma teknikleri, CMOS, düşük gürültülü amplifikatör, güç amplifikatörü

Ultra geniş bant (UWB) amplifikatörler, geniş bant genişliği ve minimum gecikme gerektiren iletişim sistemleri, radar ve fiber optik teknolojilerinin temel bileşenleridir. Dağıtık amplifikatörler (DA'lar), yapay iletim hattı yapıları aracılığıyla parazitik kapasitansları etkili bir şekilde yöneterek doğal geniş bant performansı sunmaktadır. Ancak, geleneksel DA'lar, çok sayıda kademe, kapsamlı ara bağlantılar ve pasifler nedeniyle genellikle geniş silikon alanları tüketmektedir. Bu tez, kaskod ve kompakt indüktör tabanlı alan azaltma yöntemlerinde tam şönt tepe yöntemi ile artırılmış transkondüktans bant genişliğini, dağıtılmış güç amplifikatörleri (DPA) ve dağıtılmış düşük gürültülü amplifikatörler (DLNA) için azaltılmış kalite faktörü optimizasyonuyla sunmaktadır. Önerilen DPA, minimum 70 GHz bant genişliğinde ortalama 13,75 dB kazanç ve ortalama 13,69 dBm kararlı çıkış gücü sağlamaktadır. DLNA, aynı frekans aralığında ortalama 13,6 dB kazançla 6 dB'nin altında bir gürültü değerine sahiptir. TSMC'nin 65 nm toplu CMOS teknolojisinde uygulanan her iki tasarım da gürültü figürü, kazanç ve çıkış gücü açısından literatürden daha iyi sonuçlanmıştır.

#### ACKNOWLEDGEMENTS

This thesis was supported by the Scientific and Technological Research Council of Turkey (TÜBİTAK) under Grant No. 121C073, titled "Development of Critical Building Blocks for mm-Wave and sub-THz Front-End Transceivers on CMOS Towards 1 Tbps Wireless Communications."

First and foremost, I would like to express my sincere gratitude to my supervisor, Asst. Prof. Dr. Korkut Kaan Tokgöz, for his continuous guidance and support throughout my academic journey. His mentorship - extending from my undergraduate years into my master's studies - has profoundly shaped both my technical expertise and personal development.

I also wish to thank the members of my thesis committee, Prof. İbrahim Tekin and Assoc. Prof. Dr. Mustafa Berke Yelten, for their valuable time, insightful comments, and constructive feedback, all of which significantly contributed to the improvement of this work.

I am deeply grateful to my friends Helin, Sinan, Batu, İrem, Ekin, Bartu, Ege, Erkin, Efe, and many others, for their enduring friendship and the countless shared experiences that made my university life meaningful.

Lastly, I would like to thank my parents, Ash and First for their unwavering support, love, and encouragement throughout this journey. Their sacrifices and constant presence - both mentally and physically - have been instrumental in helping me move forward in life and complete this thesis.

| In memory of my grandfather, Kurtul Tülüveli, Bana hem öğrenmeyi hem de öğretmeyi sevdiren | learning and kuymetli dedem | the joy of teaching |

|--------------------------------------------------------------------------------------------|-----------------------------|---------------------|

|                                                                                            |                             |                     |

|                                                                                            |                             |                     |

## TABLE OF CONTENTS

| LI                                          | ST ( | OF TA                            | BLES                                        | X    |

|---------------------------------------------|------|----------------------------------|---------------------------------------------|------|

| LI                                          | ST ( | OF FIG                           | GURES                                       | xi   |

| LI                                          | ST ( | OF AB                            | BREVIATIONS                                 | xiii |

| 1.                                          | INT  | RODU                             | UCTION                                      | 1    |

|                                             | 1.1. | Need f                           | for Ultra-Wideband Amplifiers               | 1    |

|                                             | 1.2. | Ultra-                           | Wideband Amplifiers and Topologies          | 2    |

|                                             |      | 1.2.1.                           | What is Ultra-Wideband Amplifier?           | 2    |

|                                             |      | 1.2.2.                           | Various Ultra-Wideband Amplifier Topologies | 3    |

|                                             |      |                                  | 1.2.2.1. Resistive-Feedback Amplifier       | 3    |

|                                             |      |                                  | 1.2.2.2. Filter-Match Amplifier             | 3    |

|                                             |      |                                  | 1.2.2.3. Distributed Amplifier              | 4    |

|                                             | 1.3. | Motiva                           | ation                                       | 6    |

|                                             | 1.4. | Thesis                           | Organization                                | 7    |

| 2.                                          | BAG  | CKGR                             | OUND                                        | 8    |

| 2.1. Overview of Distributed Amplifiers     |      |                                  | 8                                           |      |

|                                             |      | 2.1.1.                           | Operation Principles                        | 10   |

| 2.2. Performance Limitations and Trade-Offs |      | mance Limitations and Trade-Offs | 14                                          |      |

|                                             |      | 2.2.1.                           | Number of Stages vs. Delay and Gain         | 14   |

|                                             |      | 2.2.2.                           | Noise                                       | 15   |

|                                             |      | 2.2.3.                           | Linearity                                   | 19   |

|                                             | 2.3. | Distrib                          | buted Amplifier Topologies                  | 20   |

|                                             |      | 2.3.1.                           | Conventional Distributed Amplifier          | 20   |

|                                             |      | 2.3.2.                           | Cascode Distributed Amplifiers              | 21   |

|                                             |      | 2.3.3.                           | Inductive Peaking Techniques                | 22   |

|                                             |      | 2.3.4.                           | Tapered Structures                          | 23   |

|                                             |      | 2.3.5.                           | Feedback-based distribute amplifiers        | 25   |

|                                             | 2.4. | Area I                           | Reduction Techniques                        | 26   |

|    |      | 2.4.1. | Slow-Wave Transmission Lines                               | 27 |

|----|------|--------|------------------------------------------------------------|----|

|    |      | 2.4.2. | Inductor Design Strategies                                 | 28 |

|    |      |        | 2.4.2.1. Different Shapes                                  | 29 |

|    |      |        | 2.4.2.2. Stacked Inductors                                 | 29 |

| 3. | DIS  | TRIB   | UTED POWER AMPLIFIER                                       | 31 |

|    | 3.1. | Design | Considerations of the Power Amplifier                      | 31 |

|    | 3.2. | Metho  | odology and Theoretical Calculations                       | 32 |

|    |      | 3.2.1. | Class-A Power Amplifier                                    | 32 |

|    |      | 3.2.2. | $G_m$ Peaking                                              | 32 |

|    | 3.3. | Propo  | sed Design Procedures                                      | 37 |

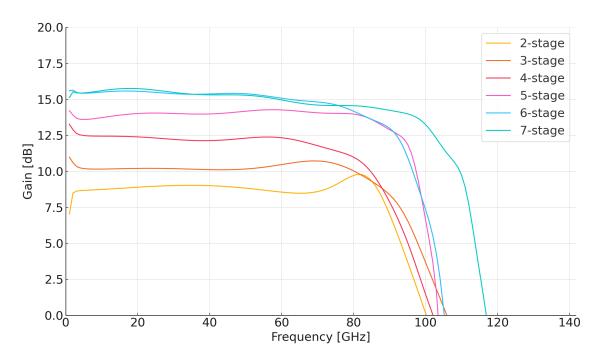

|    |      | 3.3.1. | Stage Number and Cascading Strategy                        | 37 |

|    |      | 3.3.2. | Low-Quality Factor Inductor-Based Area Reduction Technique | 39 |

|    | 3.4. | Simula | ation Results                                              | 43 |

|    | 3.5. | Comp   | arison to Literature                                       | 48 |

| 4. | DIS  | TRIB   | UTED LOW NOISE AMPLIFIER                                   | 51 |

|    | 4.1. | Design | n Considerations of the DLNA                               | 51 |

|    | 4.2. | Theore | etical Calculations                                        | 52 |

|    |      | 4.2.1. | NF Calculation                                             | 52 |

|    |      | 4.2.2. | Total Transconductance Peaking                             | 54 |

|    | 4.3. | Metho  | odology of Proposed Design or Proposed Design Procedures   | 55 |

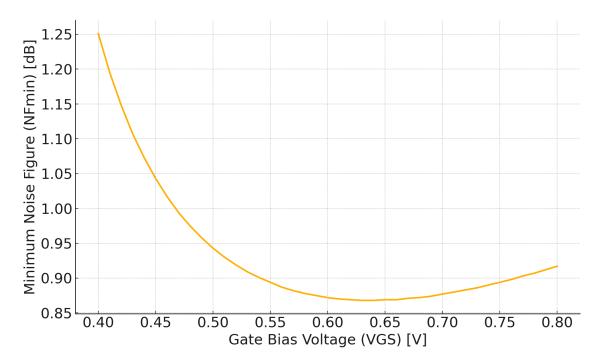

|    |      | 4.3.1. | Optimal Biasing                                            | 56 |

|    |      | 4.3.2. | Optimal Transistor Sizing                                  | 56 |

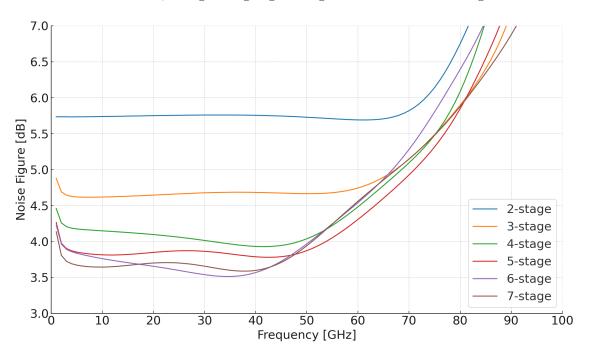

|    |      | 4.3.3. | Stage Number Optimization                                  | 57 |

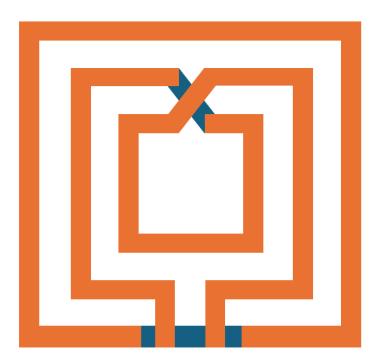

|    |      | 4.3.4. | Low-Quality Factor Inductor-Based Area Reduction Technique | 58 |

|    | 4.4. | Simula | ation Results                                              | 60 |

|    | 4.5. | Comp   | arison to Literature                                       | 65 |

| 5. | CO   | NCLU   | SION AND FUTURE WORK                                       | 67 |

|    | 5.1. | Summ   | nary of the Work                                           | 67 |

|    |      |        | e Work                                                     | 68 |

| БI | BI I | OCDA   | DUV                                                        | 60 |

## LIST OF TABLES

| Table 3.1. | 3-dB Bandwidth vs. Number of Stages                              | 38 |

|------------|------------------------------------------------------------------|----|

| Table 3.2. | Schematic inductor values                                        | 42 |

| Table 3.3. | Post-layout inductor values and area consumption                 | 42 |

| Table 3.4. | Comparison of State-of-the-Art DPA                               | 49 |

|            |                                                                  |    |

| Table 4.1. | Schematic inductor values of DLNA                                | 58 |

| Table 4.2. | Post-layout inductor values and area consumption of DLNA $\dots$ | 59 |

| Table 4.3. | Comparison of State-of-the-Art DLNA                              | 66 |

## LIST OF FIGURES

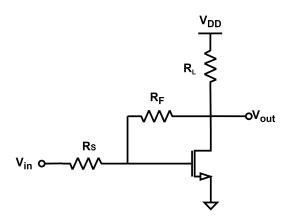

| Figure 1.1.  | Common-source amplifier with resistive feedback                      | 4  |

|--------------|----------------------------------------------------------------------|----|

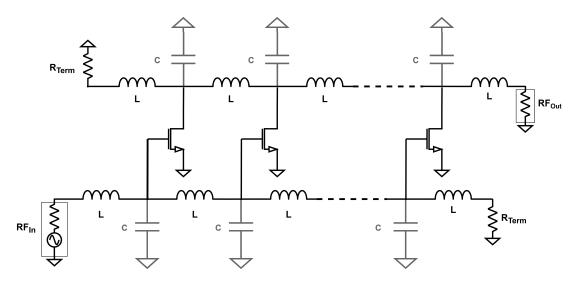

| Figure 1.2.  | Distributed amplifier in the form of LC ladders                      | 5  |

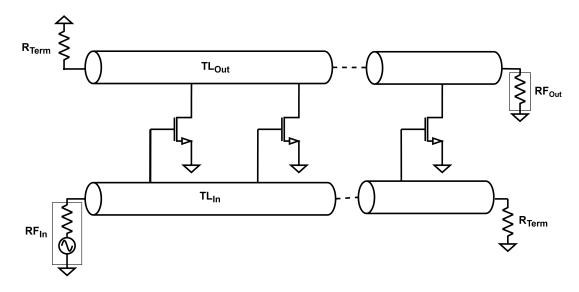

| Figure 2.1.  | Distributed amplifier with transmission line                         | 9  |

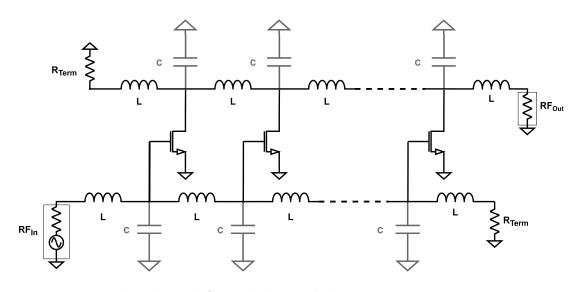

| Figure 2.2.  | Distributed amplifier with lumped elements                           | 9  |

| Figure 2.3.  | Output current after each gain-cell                                  | 11 |

| Figure 2.4.  | MESFET distributed amplifier model for noise analy-                  |    |

| sis.(Ai      | tchison, 1985)                                                       | 16 |

| Figure 2.5.  | MESFET small signal model for noise analysis.(Aitchison, 1985)       | 16 |

| Figure 2.6.  | Conventional distributed amplifier with gain cell as Gm              |    |

| (transc      | conductance)                                                         | 21 |

| Figure 2.7.  | Cascode distributed amplifier                                        | 22 |

| Figure 2.8.  | Cascode distributed amplifier with inductive peaking in circular. $$ | 23 |

| Figure 2.9.  | Effect of gate peaking in various technologies (Feng, Boon,          |    |

| Meng,        | Yi, Yang, Li & Luong, 2017)                                          | 24 |

| Figure 2.10. | Tapered DA                                                           | 25 |

| Figure 2.11. | Intra-stack coupling gain cell                                       | 26 |

| Figure 2.12. | Drain-gate line coupling                                             | 26 |

| Figure 2.13. | Conventional CPW transmission line (Yağmurlu & Tokgöz,               |    |

| 2024).       |                                                                      | 28 |

| Figure 2.14. | Slow-wave transmission line (SWTL) with floating slot-type           |    |

| metal        | structure (Yağmurlu & Tokgöz, 2024)                                  | 28 |

| Figure 3.1.  | Class-A amplifier voltage and current waveforms                      | 33 |

| Figure 3.2.  | $I_{ds}$ vs $v_{gs}$ graph of 65-nm CMOS                             | 34 |

| Figure 3.3.  | Small-signal model of cascode FET                                    | 34 |

| Figure 3.4.  | Small-signal model with interstage peaking using $L_p$               | 35 |

| Figure 3.5.  | Fully shunt-peaked model with both $L_p$ and $L_g$                   | 35 |

| Figure 3.6.  | Transconductance comparison of regular, interstage, and fully        |    |

| peakin       | g methods in cascode                                                 | 37 |

| Figure 3.7.  | Different number of stages gain vs frequency                         | 38 |

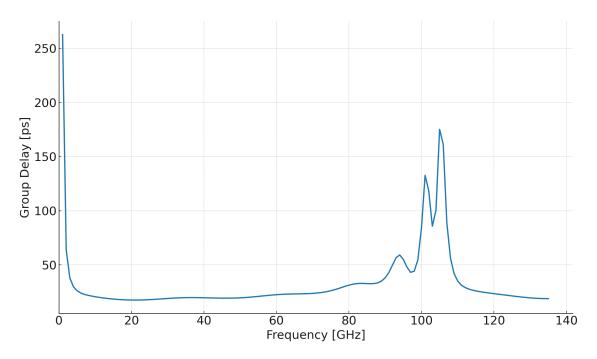

| Figure 3.8. Different number of stages delay vs frequency                             | 39 |

|---------------------------------------------------------------------------------------|----|

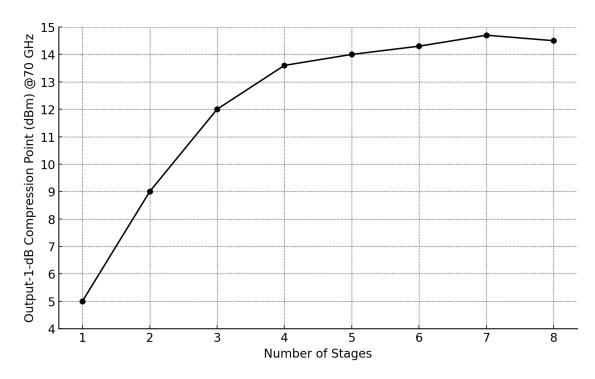

| Figure 3.9. Different number of stages $OP_{1dB}$ vs frequency                        | 40 |

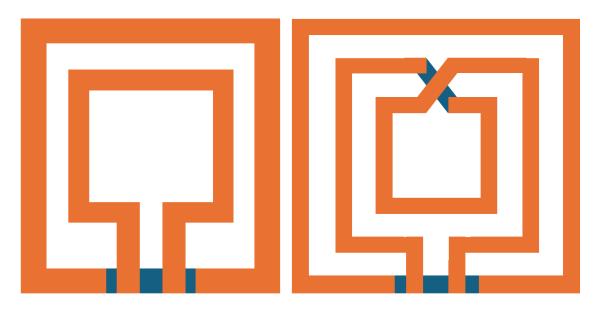

| Figure 3.11. One turn and two turn square inductor layouts                            | 41 |

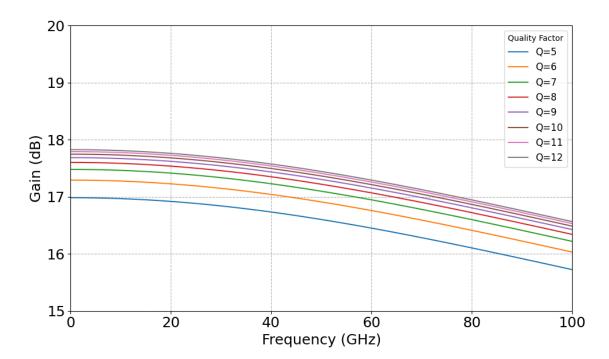

| Figure 3.10. Fully Shunt-Peaked Cascode $G_m(f)$ in different Q inductors             |    |

| vs frequency.                                                                         | 41 |

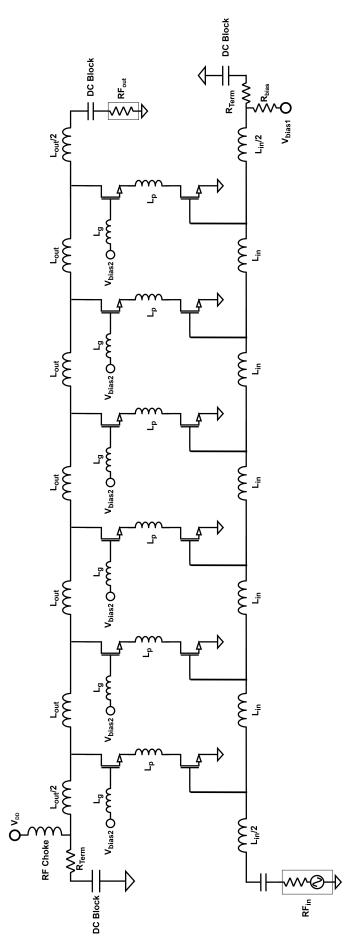

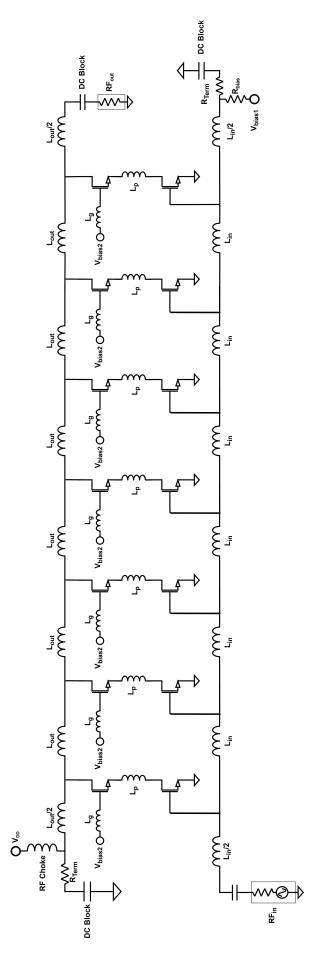

| Figure 3.12. Schematic of the six-stage DPA.                                          | 44 |

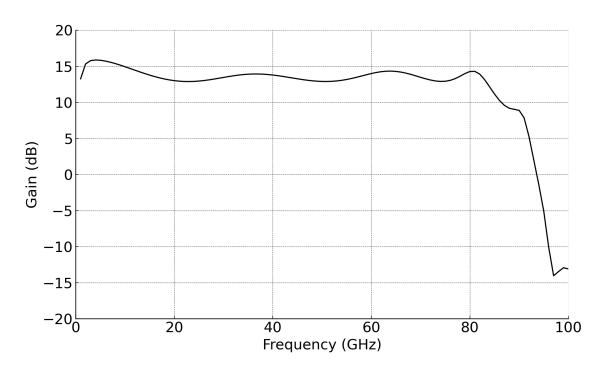

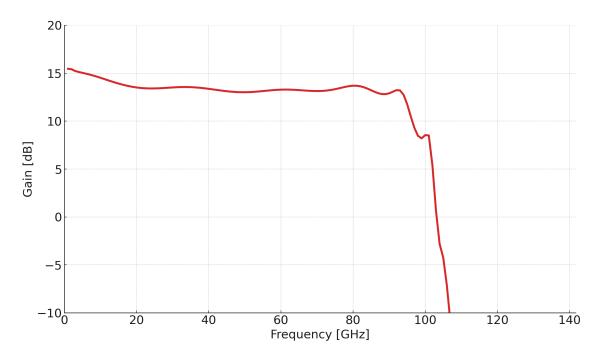

| Figure 3.13. Gain of the six-stage DPA across frequency                               | 45 |

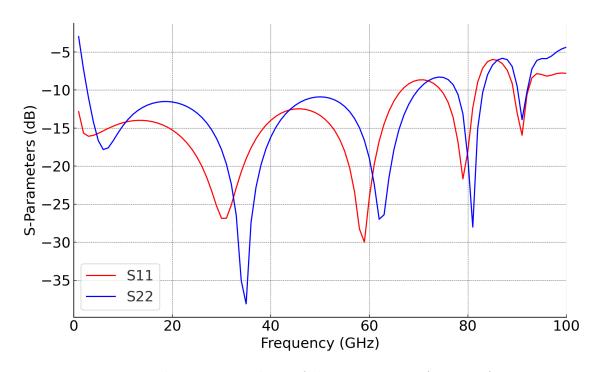

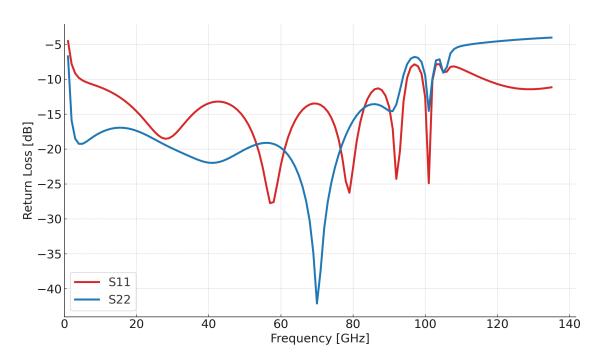

| Figure 3.14. Input and output matching of the six-stage DPA across fre-               |    |

| quency                                                                                | 45 |

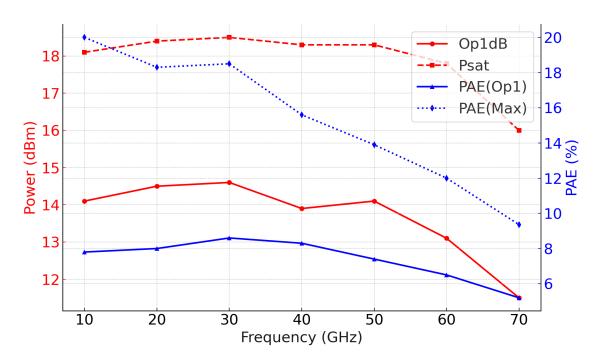

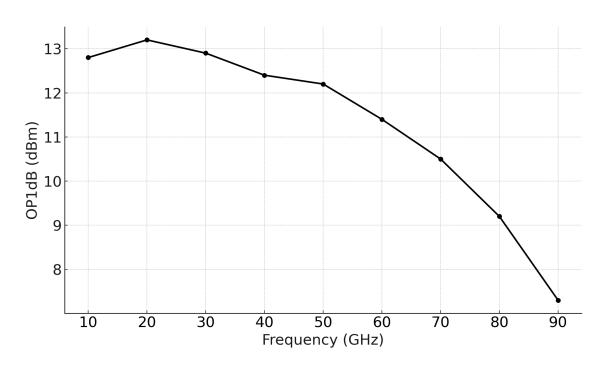

| Figure 3.15. $OP_{1dB}$ , $P_{sat}$ , PAE at $OP_{1dB}$ , and maximum PAE of the six- |    |

| stage DPA across frequency.                                                           | 46 |

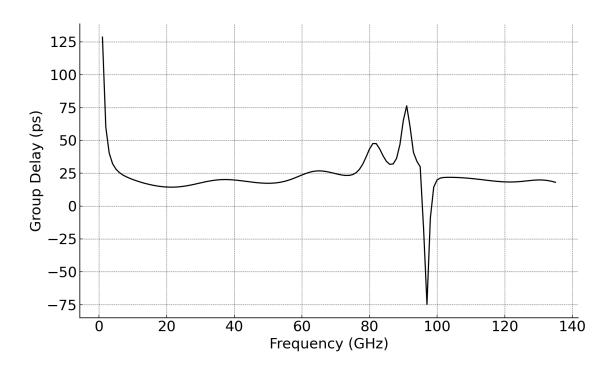

| Figure 3.16. Delay of the six-stage DPA across frequency                              | 46 |

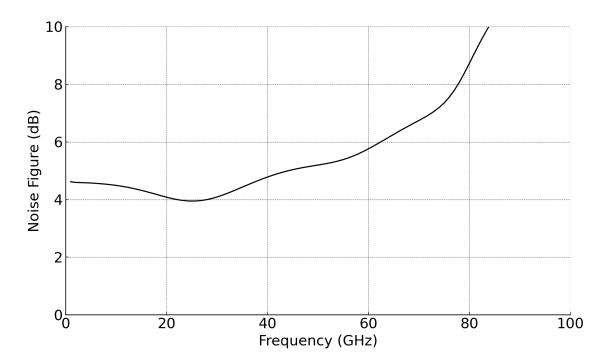

| Figure 3.17. NF of the six-stage DPA across frequency                                 | 47 |

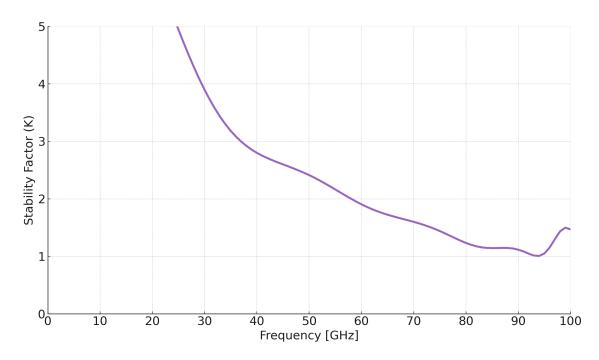

| Figure 3.18. Stability factor of the six-stage DPA across frequency                   | 47 |

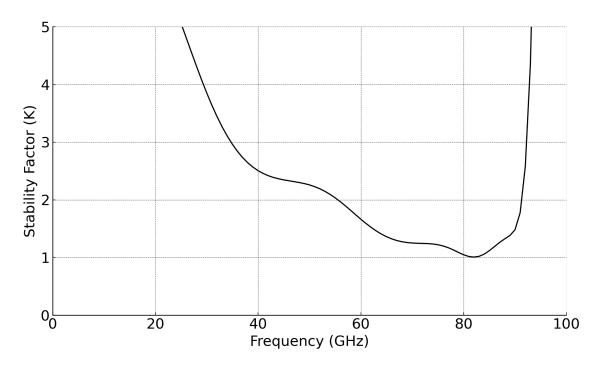

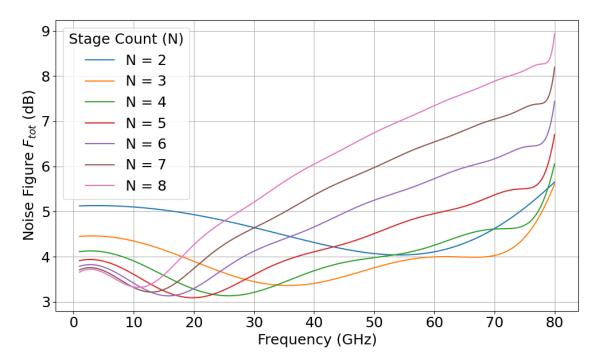

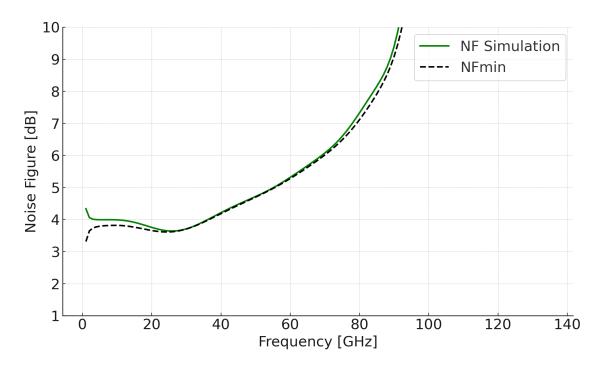

| Figure 4.1. Noise figure of different numbers of stages with Eq.4.1                   | 54 |

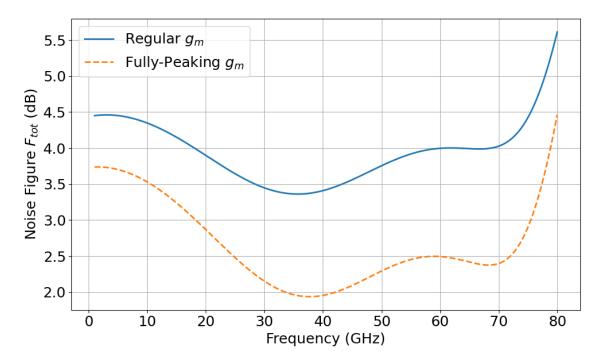

| Figure 4.2. Noise figure of a 3-stage DA comparing regular and fully shunt-           | 94 |

| peaked $G_m$ structures                                                               | 55 |

| Figure 4.3. $NF_{min}$ vs $V_{GS}$ of a cascode                                       | 56 |

| Figure 4.4. Gain vs frequency of stages between 2 to 7                                | 57 |

| Figure 4.5. NF vs frequency of stages between 2 and 7                                 | 58 |

| Figure 4.6. 2-turn square inductor layout                                             | 59 |

| Figure 4.7. Schematic of the seven-stage DLNA                                         | 60 |

| Figure 4.8. Gain of the seven-stage DLNA.                                             | 61 |

| Figure 4.9. Input and output matching of the seven-stage DLNA                         | 62 |

| Figure 4.10. $OP_{1dB}$ the seven-stage DLNA                                          | 62 |

| Figure 4.10. Of IdB the seven-stage DLVA                                              | 02 |

| seven-stage DLNA.                                                                     | 63 |

| Figure 4.12. Delay of the seven-stage DLNA.                                           | 64 |

| Figure 4.13. Stability factor of the seven-stage DLNA                                 | 64 |

| rigure 4.15. Stability factor of the seven-stage DLNA                                 | 04 |

## LIST OF ABBREVIATIONS

| ADS: Advanced Design System                   |

|-----------------------------------------------|

| ATL: Artificial Transmission Lines            |

| BiCMOS: Bipolar CMOS                          |

| CMOS: Complementary Metal–Oxide–Semiconductor |

| CPW: Coplanar Waveguide6                      |

| DA: Distributed Amplifier4                    |

| DLNA: Distributed Low Noise Amplifier         |

| DPA: Distributed Power Amplifier7             |

| FCC: Federal Communications Commission        |

| FBW: Fractional Bandwidth                     |

| GaAs: Gallium Arsenide                        |

| GaN: Gallium Nitride                          |

| GBP: Gain Bandwidth Product                   |

| $g_m$ : Transconductance                      |

| $G_m$ : Total Transconductance                |

| HBT: Heterojunction Bipolar Transistor        |

| IC: Integrated Circuit                        |

| InP: Indium Phosphide22                       |

| LNA: Low Noise Amplifier                      |

| MESFET: Metal-Semiconductor Field-Effect Transistor | 16   |

|-----------------------------------------------------|------|

| NF: Noise Figure                                    | 6    |

| $OP_{1dB}$ : Output 1-dB Compression Point          | 6    |

| PA: Power Amplifier                                 | 1    |

| PAE: Power-Added Efficiency                         | 43   |

| P <sub>sat</sub> : Saturated Output Power           | . 43 |

| Q: Quality Factor                                   | 10   |

| SiGe: Silicon-Germanium                             | 3    |

| SOI: Silicon-on-Insulator                           | 22   |

| SWTL: Slow-Wave Transmission Lines                  | .27  |

| UWB: Ultra Wideband                                 | 1    |

| Z <sub>0</sub> : Characteristic Impedance           | 10   |

#### 1. INTRODUCTION

#### 1.1 Need for Ultra-Wideband Amplifiers

The need for higher data transfer rates is driving continuous innovation in communication systems. According to the Shannon–Hartley theorem, channel capacity is governed by three parameters, which are bandwidth, signal power, and noise level. Especially in scenarios where the available power or noise figure is already near its practical limit, widening the bandwidth becomes the most direct and effective means of boosting capacity, as expressed in Eq. 1.1.

$$(1.1) C = B \log_2 \left( 1 + \frac{S}{N} \right)$$

High-frequency wireless technologies are now commonly used in millimeter-wave communication, automotive radar, and fiber-optic systems. These applications demand ultra-wideband (UWB) amplifiers that operate across tens of gigahertz while maintaining stable gain, either high output power or low noise, and minimal latency.

These parameters are controlled mainly by two important amplifiers, which are low-noise and power amplifiers (PA). On the receiver side, the low noise amplifier (LNA) amplifies weak incoming signals while minimizing added noise. This reduces the overall noise of the entire path, making the signal-to-noise ratio lower. On the transmit side, the power amplifier (PA) amplifies the amplified signal to a maximum reachable output power, which is controlled by the PA's Saturated Output Power Psat. PAs are used as the final stage before the antenna, while the form of the signal does not affect.

However, most of the PA and LNA designs often do not deliver UWB flat gain

and matching. This makes the traditional amplifier topologies not usable in these bandwidths. Moreover, as operating bandwidth increases, parasitic effects and gain-bandwidth limitations become more dominant, making conventional solutions insufficient for UWB applications. This makes the researchers search for possible solutions for UWB coverage.

#### 1.2 Ultra-Wideband Amplifiers and Topologies

#### 1.2.1 What is Ultra-Wideband Amplifier?

As the name implies, ultra-wideband (UWB) amplifiers are designed to operate in an extensive frequency range. According to the literature Yang & Giannakis (2004) and the Federal Communications Commission (FCC) Federal Communications Commission (2002) in the United States, a signal is classified as a UWB, if it satisfies one of the following criteria: greater than 500 to 1500 MHz of bandwidth or a fractional bandwidth (FBW) of greater than 20-25% which fractional bandwidth is calculated according to Eq.1.2.

(1.2)

$$FBW_{\%} = \left(\frac{2(f_H - f_L)}{f_H + f_L}\right) \times 100 \ge 25\%$$

In this thesis, the designed amplifiers are expected to work minimum in the range of 1 GHz to 71 GHz, resulting in a 70 GHz bandwidth. This large bandwidth results in an FBW of 194%. This FBW value exceeds the minimum requirement presented by the FCC and the literature for UWB systems. This much bandwidth also shows the design's goal of high-speed data transfer across a wide frequency range. Traditional amplifier topologies commonly fail to meet these requirements due to the limited FBW designs.

#### 1.2.2 Various Ultra-Wideband Amplifier Topologies

To solve the limitations that were presented previously, UWB amplifier designs must be used, and they are expected to be able to work in broadband or have higher FBW inherently. Among various topologies that have large bandwidth, the resistive-feedback amplifier, filter-match amplifier, and distributed amplifier emerge as an effective solution to these problems.

#### 1.2.2.1 Resistive-Feedback Amplifier

Resistive feedback is a method that is commonly used to extend bandwidth and better impedance matching over larger bandwidths. The topology consists of a resistor that connects a resistor to the input and output nodes, creating a feedback loop which is shown in Figure 1.1. In the literature, it is even suggested to put a degeneration resistor to even enhance gain flatness and linearity (Lee, 2003).

(1.3)

$$Z_{\text{in}} = \frac{R_F}{1 + g_m R_L}, \quad Z_{\text{out}} = \frac{R_F}{1 + g_m R_S}$$

In implementations of resistive-feedback input and output impedance can be calculated using Eq. 1.3. This enables only 4-parameter control for matching, resulting in simultaneous matching to  $50\Omega$  by selecting appropriate values for  $R_F$ ,  $R_L$ , and  $R_S$  based on the transistor's transconductance  $(g_m)$ .

In the literature, resistive feedback loops are used multiple times back-to-back to build a design without inductors that is LNA in Silicon-Germanium (SiGe). It has a 20 dB gain and 7 GHz bandwidth with a noise of 3 dB to 4 dB, while without the inductors, significantly reduced area (Lee & Cressler, 2005).

#### 1.2.2.2 Filter-Match Amplifier

The filter-match amplifier is one of the designs that can enable UWB amplification. It can use the input capacitance of a transistor or an external capacitor together with an inductor to create an LC band-pass filter (Ismail & Abidi, 2004). This allows the amplifier to have a wide impedance matching. However, the filters' inherent low-frequency blocking capability is not suitable for down to direct current (DC)

Figure 1.1 Common-source amplifier with resistive feedback.

applications.

In the literature, filter-match amplifiers are commonly found in 3 GHz to 10 GHz (Bevilacqua & Niknejad, 2004; Ismail & Abidi, 2004). Peaking inductors can be added to boost the effective bandwidth and help extend bandwidth beyond the unity gain frequency (Bevilacqua & Niknejad, 2004). Compared to resistive-feedback amplifiers, this topology is less area efficient due to the usage of an inductor in the band-pass filter. But, it has a comparable power consumption to the resistive-feedback amplifier. These techniques are shown in UWB LNAs using both ladder-type and shunt-feedback structures, each with different trade-offs between area and gain flatness (Bevilacqua & Niknejad, 2004; Ismail & Abidi, 2004).

In these conventional lumped amplifiers (filter-match and resistive-feedback amplifiers), the gain bandwidth product (GBP) is constrained by the parasitic capacitances of the active devices. This leads to the classical trade-off where increasing voltage gain  $A_v$  typically decreases the -3 dB bandwidth  $f_{-3dB}$ , since their product remains nearly constant, as expressed in Eq. 1.4:

#### 1.2.2.3 Distributed Amplifier

Distributed amplifier (DA) takes a completely different approach from the other UWB or broadband amplifier topologies. The main difference between it and the

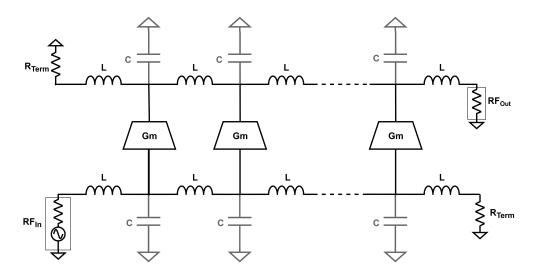

Figure 1.2 Distributed amplifier in the form of LC ladders.

other topologies is in distributed amplifiers instead of cascading transistors to increase the gain-bandwidth product, which places the transistors in parallel to each other. Then connects each transistor's gate and drain with inductors to form artificial transmission lines(ATLs). These LC ladders, as shown in Figure 1.2, allow the parasitic capacitance of transistors to be absorbed and allow the signal to propagate inside the created ATLs. Each stage produces an amplified signal, and these signals combine at the output which resulting in a higher gain. This parallel structure of a distributed amplifier helps to distribute gain across stages and enables wider bandwidths. Therefore, distributed amplifiers can surpass the gain-bandwidth limitation.

Normally, in a transistor, the gain-bandwidth is limited by the unity-gain. In a single transistor, if the width is doubled gain should be increased, but the bandwidth should drop due to higher output capacitance. However, in DAs, gain can be increased by adding more stages and without ht affecting the bandwidth, because the output capacitance of each stage is separated stage by stage. In DAs, trade is mainly between the delay to gain, which is inversely proportional to each other, because to increase gain, more stages need to be added, but this increases the number of stages delays to each other, but the frequency stays flat. The matching is controlled by terminating input and output lines with resistances that make matching automatic.

As every topology has drawbacks, distributed amplifiers have their drawbacks, too. First, half of the output power is lost to the output termination resistor. This also reduces the efficiency significantly. The area and power consumption are high due to the number of stages, increasing them by a 5 to 10 times increase in power consumption (Bevilacqua & Niknejad, 2004). The area is larger due to the use of lots of inductors, which cover most of the area. Noise figure is around 3 dB at low frequency due to the termination resistance at the input ATL. However, these

negative effects do not affect its usability due to its benefits.

#### 1.3 Motivation

In millimeter-wave communication links, multi-purpose wireless communication, ultra-wideband communication, fiber-optic systems ultra-wideband (UWB) amplifiers are required in both the transmit and receive chains to cover tens of gigahertz while maintaining minimal latency and distortion. Among the available UWB topologies, the distributed amplifier (DA) is particularly well suited for bandwidths up to 70 GHz. This is due to its ATL structure, which absorbs parasitic capacitances along the line, resulting in minimal impact on bandwidth. In addition, the integrated termination resistor enables the design to achieve broadband matching inherently.

The main drawback of the DA, however, is its large area consumption. Each added stage, along with its ATL section, significantly increases the layout size, often exceeding 0.5 mm<sup>2</sup> in 65-nm Complementary metal—oxide—semiconductor (CMOS). This becomes a major constraint in multi-amplifier systems where multiple circuits must share a single die, especially in research applications where silicon area is a limited and costly resource.

This thesis, therefore, focuses on realizing area-efficient DAs while maintaining state-of-the-art performance. In the PA path, the goal is to achieve a maximum gain of 15 dB and stable output power above 13 dBm across a minimum bandwidth of 70 GHz, all within the smallest possible area. In the LNA path, the target is to maintain a flat noise figure below 6 dB and a peak gain of 15 dB over at least the same bandwidth, again with aggressive area reduction. Across both paths, the area optimization is driven by reducing passive components' area usage, either in the form of more compact transmission lines or optimized inductor structures.

All circuits are realized in TSMC 65-nm bulk CMOS and are designed to outperform recent literature in noise figure (NF), total transconductance  $(G_m)$ , output 1-dB compression point $(OP_{1dB})$ , and expected layout footprint. The ensuing chapters detail the underlying theory, the proposed area-reduction techniques, and the experimental validation of these claims.

#### 1.4 Thesis Organization

The thesis organization follows:

The remainder of this thesis is organized as follows:

- Chapter 2 provides a comprehensive background on distributed amplifiers. It begins by explaining their operational principles and then discusses key performance limitations, such as gain-delay trade-offs, noise behavior, and distortion mechanisms. Various distributed amplifier (DA) topologies are reviewed, including cascode, inductive peaking, tapered, and feedback-based designs. The chapter concludes by introducing area reduction methods, focusing on slow-wave transmission lines, inductor different shapes and stacked inductor strategies.

- Chapter 3 presents the design and analysis of the proposed distributed power amplifier (DPA). Design considerations and theoretical formulations are detailed, including Class-A operation and  $G_m$  peaking. The proposed design methodology is described, followed by the simulation results at the schematic level and the EM simulated inductor schematic. The performance is then benchmarked against state-of-the-art designs in the literature.

- Chapter 4 focuses on the development of the distributed low noise amplifier (DLNA). Design aspects specific to low-noise performance are discussed, supported by theoretical noise figure calculations and transconductance optimization. The chapter also details the applied area reduction techniques and includes both schematic and layout-level simulations. A comparative evaluation with prior work concludes the chapter.

- Chapter 5 summarizes the contributions of the thesis. It highlights the key achievements, discusses limitations, and proposes directions for future research in ultra-wideband amplifier design.

#### 2. BACKGROUND

#### 2.1 Overview of Distributed Amplifiers

The topology of distributed amplification dates back to Percival's patent in 1936 (Percival, 1937), but it was perfected and published in the scientific community by Ginzton in 1948 (Ginzton, Hewlett, Jasberg & Noe, 1948). This approach was considered a solution for achieving wide-band amplification with vacuum tube technology, which is the most common amplifier technology. Since then, distributed amplifiers (DAs) have become a fundamental wideband amplifier architecture because they can surpass the intrinsic gain-bandwidth limitation of individual transistors. During the past decades, advances in IC interconnects, passive components, and transistor technologies have enabled compact, fully integrated ultra-wideband amplifiers operating well into the sub-terahertz range.

This chapter begins by introducing the operational principles of the distributed amplifier, focusing on the theoretical basis of its design. It then presents the conventional DA architecture, followed by an analysis of performance limitations and trade-offs. Next, the chapter surveys several DA topologies and highlights their respective advantages and limitations. Finally, this chapter concludes with a detailed examination of area reduction techniques for reducing areas occupied by the passive devices.

#### 2.1.1 Operation Principles

Figure 2.1 Distributed amplifier with transmission line.

Figure 2.2 Distributed amplifier with lumped elements.

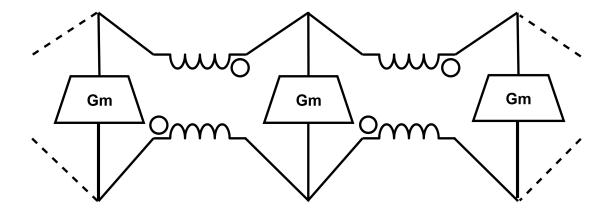

In distributed amplifiers, transconductive stages (gain cells) are arranged in parallel. These stages are made up of transistors, and before integrated circuits (IC), vacuum tubes were used as amplifiers. These stages are interconnected to each other either by ATLs or inductors at their input and output lines, shown in Figure 2.2 and Figure 2.1. In this topology, the input signal propagates along the gate line. The input wave then reaches each gain-cell gate after a fixed delay introduced by the preceding line section. Each delay section lies between adjacent gain cells, and the gate line is terminated by a resistor at its far end.

As the input signal moves along the gate lines, it sequentially activates the gain cells one by one. In the same sequential order, each activated gain cell creates an output current into the drain line. Equal per-section delays keep all drain currents in phase, so they combine coherently at the output..

Meanwhile, backward propagating signals are also generated, as depicted in Figure 2.3. Half of the signal propagates toward the output, while the other half moves in the reverse direction. As shown in Figures 2.2 and 2.1, a termination resistor at the drain line absorbs the backward-traveling wave and eliminates reflections or unwanted feedback.

Because the output signals from each gain cell add linearly, the total voltage gain scales approximately with the number of active stages. The fundamental gain expression of an ideal distributed amplifier is given in Eq. 2.1.

(2.1)

$$A_v(w) = \frac{1}{2} N g_m(w) Z_0$$

(Razavi, 2002)

Eq. 2.1 assumes the gain expression for an ideal, lossless distributed amplifier in which each gain stage contributes equally to the output signal. The transconductance of each gain stage is denoted by  $g_m$ , the characteristic impedance ( $Z_0$ ) of the ATLs, and the number of gain cells by N. The formula makes the assumptions that there are no losses in the active devices or ATLs, and that the propagation delay between the gate and drain lines is exactly equal. Under such conditions, the voltage contribution from each gain cell arrives in phase and adds coherently at the output, resulting in a total gain that scales linearly with N.

However, because real transmission lines have conductor and dielectric losses, Eq. 2.1 overestimates gain in practical designs. In actual designs, it is impossible to create lossless elements due to parasitic losses, resistances, and dielectric losses, and limited quality factor (Q) that all degrade the signal while propagating.

Figure 2.3 Output current after each gain-cell.

Two main implementation strategies are commonly used: transmission-line-based and lumped-element-based distributed amplifiers. Among these, transmission-line-based designs are more prevalent in DA applications, as they allow wider response and better DC behavior. Transmission lines are basically periodic LC sections that approximate the behavior of a continuous flow.

In transmission-line implementations, the attenuation constant  $\alpha$ quantifies the exponential decay of signal amplitude per unit length caused by conductor and dielectric losses. As input and output signals propagate through the gate and drain lines, they experience signal degradation. This signal degradation is significantly increasing with the frequency f and propagation distance  $l_u$ . The resulting voltage gain of a distributed amplifier with lossy transmission lines is given by the expression in Eq. 2.2, which incorporates these loss mechanisms by including  $\alpha$ , n, and  $l_u$  to quantify the cumulative attenuation effect across all stages.

$$(2.2) A_v(w) \approx \left(1 - \frac{\alpha(w)nl_u}{2}\right) \cdot \frac{ng_m(w)Z_0}{2} (Razavi, 2002)$$

A power gain approximation for transmission-line-based DAs was first presented in 1982 (Ayasli, Mozzi, Vorhaus, Reynolds & Pucel, 1982). By applying the same parameters as defined in Eq. 2.2, this approximation captures the non-linear effect of signal loss along the gate line. It provides an estimated value for practical power

gain and shows that, unlike voltage gain, the power gain does not increase linearly with stage number. Instead, it reflects the attenuation impact more accurately, especially at higher frequencies or when more stages are added.

$$(2.3) \hspace{1cm} G \approx \frac{g_m^2 n^2 Z_0^2}{4} \left( 1 - \frac{\alpha_g l_g n}{2} + \frac{\alpha_g^2 l_g^2 n^2}{6} \right)^2 \hspace{0.5cm} (Ayasliet \ al., \ 1982)$$

Depending on the frequency range that the design is intended to work in, the transmission lines might be too long, and the length increase is not area efficient. As discussed previously, the main problem of DA is area consumption, and designs do not want a large area with the combination of transmission lines, high attenuation at low frequencies compared to an inductor. Inductors become a feasible solution below 100 GHz. As a result, designers can adopt lumped-element equivalents of transmission lines using inductors and parasitic capacitors for wave propagation. In this method due to per node capacitance is controlled by the parasitic capacitances of the transistor and inductor. The drain and gate line inductors need to use different inductance values to optimize delay to increase gain, in which literature examples use different inductance values for gate and drain lines(Tarar, Qayyum, Ali & Negra, 2024). As a result, the combination can behave like ATLs that replicate the behavior of transmission lines by segmenting them into cascaded LC sections, which can be seen in Figure 2.2. The shaded areas in the figure represent the aggregated parasitic components.

In lumped DA design, a significant portion of the shunt capacitance arises from the transistor gate-source capacitance  $C_{gs}$ , which is inherent to each gain cell. Similarly, the inductance L may be realized using compact integrated inductors. Thus, the total per-section capacitance and inductance are defined by both passive devices (inductors or TLs) and the active device parasitic.

The characteristic impedance of the gate line  $Z_g$ , which determines signal matching and power division, can be expressed in Eq. 2.4.

(2.4)

$$Z_g = \sqrt{\frac{L_g}{C_g + \frac{nC_{gs}}{l_g}}} \quad (Razavi, 2002)$$

Here,  $L_g$  is the series gate inductance per section of transmission line or inductor,  $C_g$  is the added lumped capacitance from either transmission line or inductor,  $C_{gs}$  is the intrinsic gate-source capacitance of the transistor which related to its size,

and  $l_g$  is the physical length of the gate delay section. This equation reflects how the characteristic impedance of the gate line is influenced not only by the designed passive values but also by transistor parasitics.

The values of L and C used in gain expressions are similarly derived based on transmission line principles. The per-section values are selected to meet the desired  $Z_0$  and time delay  $t_d$ , following the classic relations in Eq. 2.5.

(2.5)

$$Z_0 = \sqrt{\frac{L}{C}}, \quad t_d = \sqrt{LC}$$

Solving these equations simultaneously allows the designer to extract appropriate values for L and C for each delay section:

$$(2.6) L = t_d Z_0, \quad C = \frac{t_d}{Z_0}$$

Once extracted, these values can be adjusted, ensuring that the ATL maintains both the desired impedance and the appropriate propagation delay per section. Ultimately, the interaction between the capacitances of the active device and the passive layout choices dictates the true behavior of the lumped transmission structure. Also, Eq.2.6 shows an important perspective to increase the  $Z_0$  which is linked to the  $t_d$ , L needed to increase this creates a relationship of delay to gain which will be talked about in later chapters.

Although this approach enables compact implementation, it introduces non-negligible loss mechanisms due to finite inductor quality factor  $Q_L$ . Each inductor adds resistive loss, which causes signal degradation at every stage. The Q is defined as Eq. 2.7, where R is the series resistance of the inductor:

$$(2.7) Q_L(\omega) = \frac{\omega L}{R}$$

Unlike TL-based models, which treat loss as a continuous parameter  $\alpha$ , lumpedelement lines incur discrete stage-by-stage losses. This cannot be modeled with a global line loss. Instead, the gain reduction compounds at each stage as a result of this resistive loading. The correct gain expression is shown in Eq. 2.8:

(2.8)

$$A_v(\omega) \approx \frac{ng_m(\omega)Z_0}{2} \cdot \left(\frac{Q_L}{\sqrt{Q_L^2 + 1}}\right)^n$$

This expression captures how the signal weakens in stages as a function of  $Q_L$ . For example, even with  $Q_L = 10$ , total gain drops by more than 5% for 10 stages. This effect gets worse as n increases. Therefore, choosing an appropriate  $Q_L$  is not critical as values between 8 and 15 are typically enough to keep gain degradation minimal while still enabling compact inductor designs.

Finally, a critical factor in achieving effective signal transfer and broadband performance in distributed amplifiers is impedance matching. Both the gate and drain lines must be terminated with resistive loads matched to the line's  $Z_0$ . These terminations prevent the reflection of backward-propagating signals, which would otherwise interfere destructively with forward signals and introduce frequency-dependent standing waves. Proper impedance matching ensures clean summation of output signals, wideband frequency response, and stable operation without external tuning networks, a fundamental advantage of distributed amplifier topologies.

#### 2.2 Performance Limitations and Trade-Offs

#### 2.2.1 Number of Stages vs. Delay and Gain

Many gain cells are used in a distributed amplifier. Each cell gives a small voltage step,  $A_{\text{cell}}$ , that is less than what one LC-matched stage can give. The total gain goes up with the number of stages, N, because the drain currents add in phase.

$$(2.9) A_v(N) = N A_{\text{cell}}$$

Every gate—drain section adds the same electrical delay,  $\tau$ . The longest signal path—starting at the first cell—therefore extends by roughly  $N\tau$ .

(2.10)

$$au_{\rm total} \approx N \, au$$

For a single cell, the upper 3-dB point is set by its RC pole.

(2.11)

$$BW_{cell} \approx \frac{1}{2\pi RC_{eff}}$$

In a full DA, the real bandwidth limit comes from the ATL, because the gate and drain parasitics are spread along the line instead of being lumped at one node. With inductance L' and capacitance C' per unit length, line length l, and extra shunt term  $C_{\text{in,out}}$ , the cut-off is Eq.2.12

(2.12)

$$f_{\text{cutoff}} = \frac{1}{\pi \sqrt{L'l(C'l + C_{\text{in,out}})}}$$

Gain and delay rise together, so their ratio is independent of stage count.

(2.13)

$$\frac{A_v(N)}{\tau_{\text{total}}} = \frac{A_{\text{cell}}}{\tau}$$

More stages, therefore, give higher gain and longer delay, while usable bandwidth stays almost the same, so long as the transistor  $f_T$  is comfortably above the line cut-off.

(2.14) Gain

$$\uparrow$$

, Delay  $\uparrow$ , Bandwidth  $\approx$  constant

#### 2.2.2 Noise

In distributed amplifiers, noise sources are typically grouped into two categories, which are transistor noise and thermal noise generated by passive components such

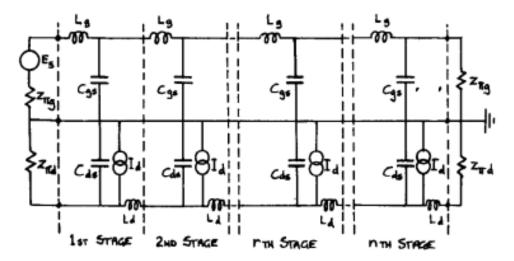

Figure 2.4 MESFET distributed amplifier model for noise analysis. (Aitchison, 1985)

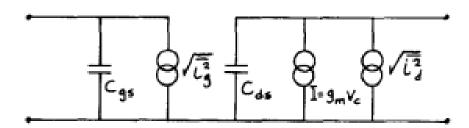

Figure 2.5 MESFET small signal model for noise analysis. (Aitchison, 1985)

as termination resistors. Transistors contribute drain noise, gate-induced noise, flicker noise, and, in some cases, popcorn noise, which is more common in junction-based devices (Lee, 2003).

In 1985, Aitchison calculated the intrinsic noise of metal—semiconductor field-effect transistor(MESFET) based distributed amplifiers, and he defined four noise sources for it, which can be seen in Fig. 2.4 and 2.5. These are gate-source impedance noise, gate load termination resistance, drain load resistance, and internal noises from transistors. Also, in calculations of lossless transmission lines or passives, it is assumed that perfect matching and per-section delay on gate and drain lines  $(\beta_g = \beta_d = \beta)$  can be used to find reverse and forward power gain calculations.

The forward and reverse available power gains under ideal matching are defined, respectively, as:

(2.15)

$$G_f = \frac{n^2 g_m^2 Z_{\pi g} Z_{\pi d}}{4} \quad (Aitchison, 1985)$$

(2.16)

$$G_r = \frac{g_m^2 Z_{\pi d} Z_{\pi g}}{4} \left(\frac{\sin n\beta}{\sin \beta}\right)^2 \quad (Aitchison, 1985)$$

Unlike lumped amplifiers, the repeating structure of distributed amplifiers allows noise from one transistor to propagate both forward and backward through the transmission line network. As a result, accurate noise analysis must include forward and reverse gain, as shown in Eq. 2.15 and Eq. 2.16.

The total noise factor was derived by summing the available noise powers from four main sources, which are source resistance, input termination resistor, drain termination resistor, and gate/drain noise. The final expression of Aitchison's for noise factor F is given by Eq.2.17.

$$(2.17) F = 1 + \left(\frac{\sin N\beta}{N\sin\beta}\right)^2 + \frac{4}{N^2 g_m^2 Z_{\pi g} Z_{\pi d}} + \frac{Z_{\pi g} \omega^2 C_{gs}^2 R}{Ng_m} \sum_{r=1}^N f(r,\beta) + \frac{4P}{Ng_m Z_{\pi g}}$$

The phase shift per section  $\beta$  and the cutoff frequency  $\omega_c$  of the LC ladder are defined as:

$$(2.18) \beta = 2\sin^{-1}\left(\frac{\omega}{\omega_c}\right)$$

$$(2.19) \omega_c^2 = \frac{4}{LC}$$

The characteristic impedances of the drain ladder and gate ladder are  $Z_{\pi d}$  and  $Z_{\pi g}$ , respectively, in Eq. 2.17. The gate-source capacitance is denoted by  $C_{gs}$ , the gate resistance by R, and the drain noise factor by P. Each gain cell's positional noise contribution is taken into account by the function  $f(r,\beta)$ , which has the following definition:

$$(2.20) f(r,\beta) = ((N-r+1)^2 + \frac{\sin(r-1)\beta}{\sin\beta})^2 + \frac{2(N-r+1)\sin(r-1)\beta\cos(r\beta)}{\sin\beta}$$

Each term in Eq. 2.17 represents a different noise source in the distributed amplifier. The first one is the basic thermal noise from the source, which is always there, no matter what kind of amplifier you're using. The second term comes from the gate termination resistor, and it follows a sinusoidal shape, and it's important at low frequencies but fades out as frequency increases. The third one is the noise from the drain termination on the left-hand side, but since it does not get amplified, it is usually very small. The fourth term is from gate-induced noise in the transistors, and this one becomes more significant at high frequencies. The last term is the noise coming from the drain side of the transistors, and it's scaled by a factor P depending on the device.

However, the Aitchison model has key flaws. He assumed that the noise power spectral density is simply the squared magnitude of the Fourier transform of the noise current, which is not valid for random processes. This leads to inaccurate results, especially at high frequencies. He also ignores the partial correlation between gate-induced and channel noise.

Heydari fixes both issues. He calculates the autocorrelation of the output noise and then applies the Fourier transform to get the correct power spectral density. His model includes all major noise sources, including gate and drain termination noise, gate-induced noise (with correlation), channel noise, and flicker noise. It also handles forward and backward noise propagation more rigorously (Heydari, 2007).

The total noise factor he derives is the following:

$$F_{\rm tot} = 1 + F_{\rm flicker} + \frac{1}{(Ng_m Z_T)^2} + \left(\frac{\sin N\beta}{N\sin\beta}\right)^2$$

$$(2.21) + \frac{\gamma}{Ng_m Z_T} \left(1 + \frac{2N^2 + 1}{3} \left|\frac{\kappa_c}{c}\right|^2 \left[(\omega \tau_{GS})^2 + 2N\kappa_c(\omega \tau_{GS})\right]\right) (Heydari, 2007)$$

Compared to Eq. 2.17, this expression is more accurate and includes real CMOS effects like correlated noise and flicker. It's also validated by measurements, making it more reliable for design.

#### 2.2.3 Linearity

Linearity is a critical performance criterion in distributed amplifiers (DAs), especially for ultra-wideband systems where signal distortion directly impacts system fidelity. Among various nonlinearity metrics, third-order intermodulation distortion (IM3) is particularly important due to its proximity to the desired signal band in two-tone tests. In DAs, the dominant source of non-linearity is the higher-order behavior of the transistor transconductance, particularly the third-order coefficient  $g_{m3}$ .

Unlike cascaded amplifier topologies, where additional stages tend to degrade linearity at constant output power, distributed amplifiers benefit from improved linearity as the number of stages increases. This improvement stems from the coherent summation of fundamental tones across stages, while the intermodulation components add incoherently. As a result, the carrier-to-intermodulation power ratio (C/IM3) increases significantly with stage count, making DAs inherently more linear under large-signal conditions. This behavior is quantitatively described by the following expression derived in (Aitchison & Mbabele, 2001):

(2.22)

$$\frac{C}{\text{IM3}} = \left(\frac{g_{m1}^3}{3k^2g_{m3}}\right)^2 n^4 e^{-2n\alpha_d}$$

Here,  $g_{m1}$  and  $g_{m3}$  are the first- and third-order transconductance coefficients, k is a constant determined by bias and input amplitude, n is the number of stages, and  $\alpha_d$  denotes the drain line attenuation in nepers per section. As seen in Eq. 2.23, the linearity improves with  $n^4$ , but is counteracted by the exponential decay introduced by line losses. However, simulations on the paper proved that the number of stages improves significantly the linearity. In five stage one compared to the one staged distributed amplifier improvement is 25 dB which a significant linearity improvement.

Linearity is a key requirement for distributed amplifiers (DAs), especially in ultrawideband designs where intermodulation products fall inside the signal band and cannot be filtered. The dominant nonlinearity in DAs stems from the device transconductance, with the cubic term  $g_{m3}$  driving IM3 in two-tone tests. Unlike cascaded topologies—where adding stages typically hurts linearity at a fixed output level—DAs improve with stage count because fundamentals add coherently while IM3 terms add incoherently. As a result, the carrier-to-IM3 ratio rises sharply with n; for example, in literature reports roughly a 25 dB improvement going from a single-stage to a five-stage DA (Aitchison & Mbabele, 2001). This behavior is captured by the expression derived in 2.23

(2.23)

$$\frac{C}{\text{IM3}} = \left(\frac{g_{m1}^3}{3k^2g_{m3}}\right)^2 n^4 e^{-2n\alpha_d}, (Aitchison \& Mbabele, 2001)$$

where  $g_{m1}$  and  $g_{m3}$  are the first- and third-order transconductance coefficients, k is a scaling constant set by bias and input amplitude, n is the number of stages, and  $\alpha_d$  is the drain-line attenuation per section (nepers). As seen in Eq. 2.23, linearity improves with  $n^4$  but is penalized by the exponential loss term  $e^{-2n\alpha_d}$  however the effect of loss term do not match the improvement of stages.

#### 2.3 Distributed Amplifier Topologies

In this part of the chapter, distributed amplifier topologies will be discussed, along with their pros and cons.

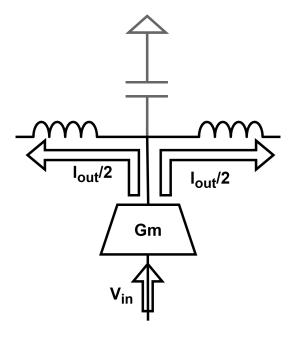

#### 2.3.1 Conventional Distributed Amplifier

Distributed amplifiers, as covered in the previous section, allow constructive signal propagation across multiple parallel gain paths, thereby overcoming the gain-bandwidth product limitation of individual transistors. Figure 2.6 depicts a typical conventional distributed amplifier; the number of parallel cells can change based on the desired performance. Each  $G_m$  cell in a conventional architecture has only one active stage, usually a common-source transistor. These  $G_m$  cells are connected by transmission lines or inductors, which, when combined with the  $G_m$  cell's inherent parasitic capacitances, create ATLs. Broadband operation is made possible by these ATLs, which facilitate synchronized wave propagation along the gate and drain networks. Examples of this conventional or common source DA on Gallium Nitride (GaN) (Hu, Zhang & Ma, 2022) and bulk CMOS (Tsai, Wang, Kuan & Chang, 2005) technologies can be found in the literature.

The ideal voltage gain of a conventional DA, with the assumption of lossless ATL and matched termination, can be seen in Eq. 2.24.

Figure 2.6 Conventional distributed amplifier with gain cell as Gm (transconductance).

(2.24)

$$A_v(w) = \frac{1}{2} NG_m(w) Z_0$$

(Razavi, 2002)

N is the number of gain stages,  $Z_0$  is the characteristic impedance, and  $G_m(\omega)$  is each cell's effective transconductance. Because of the traveling-wave nature of the signal, only half of its power reaches the load, which results in the  $\frac{1}{2}$  factor.

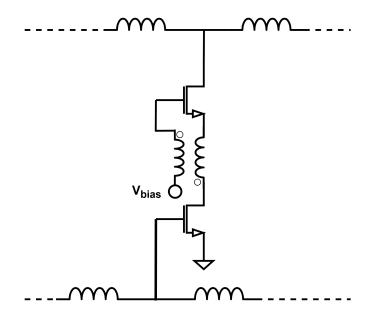

#### 2.3.2 Cascode Distributed Amplifiers

Cascode distributed amplifier is the most widely used architecture in  $G_m$  cell design (El-Chaar, Vincent, Arnould, de Souza, Bourdel & Podevin, 2022). It uses stacked transistors in each  $G_m$  cell to improve gain and high-frequency stability. By replacing a single common-source stage with a common-source stage stacked with a common-gate transistor. It can be seen in Fig. 2.7. This structure can suppress the Miller effect (Fang, Levy & Buckwalter, 2016), increase output resistance (Fang et al., 2016; Wu, Kao & Chu, 2022), enhance gain (El-Aassar & Rebeiz, 2019a), and improve reverse isolation (El-Chaar et al., 2022), making it more suitable for distributed amplifier implementations.

In the literature, this method has been applied to nearly all popular integrated circuit (IC) technologies. Depending on the process, multi-stack configurations can also be used. These include double-stacked (Arbabian & Niknejad, 2009), triple-

Figure 2.7 Cascode distributed amplifier.

stacked (Feng et al., 2017; Testa, Belfiore, Paulo, Carta & Ellinger, 2015), and even quadruple-stacked designs (El-Aassar & Rebeiz, 2019a,2). Cascode DAs have been demonstrated across various technologies, including bulk CMOS (Arbabian & Niknejad, 2009; Feng et al., 2017; Jahanian & Heydari, 2012), silicon-on-insulator (SOI) CMOS (El-Aassar & Rebeiz, 2019b,2), Indium Phosphide (InP) heterojunction bipolar transistor (HBT) (Nguyen, Cui, Nguyen, Stameroff & Pham, 2023), SiGe Bipolar CMOS(BiCMOS) (Testa et al., 2015), and Gallium arsenide (GaAs) (Hu, Ma, Xie, Liu & Feng, 2024).

However, cascode structures introduce increased power consumption, voltage headroom requirements, and layout complexity, especially in low-voltage technologies.

#### 2.3.3 Inductive Peaking Techniques

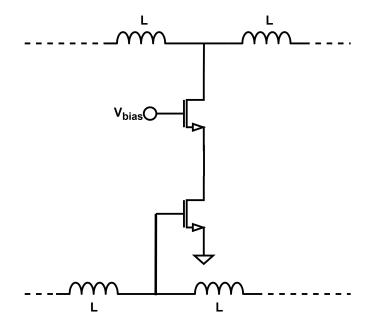

In the literature, there are two types of inductive peaking techniques, which are interstage inductive peaking and gate inductive peaking. The interstage method is most commonly used among the peaking methods. It is used in cascode topologies between common-source and common-gate transistors. This methodology focuses on the isolation of internal capacitance in that node and affects the response of  $G_m$  cells by increasing its effect at higher frequencies where transconductance usually drops. Heydari et al. (Heydari & Safiallah, 2023) showed that a simple interstage

Figure 2.8 Cascode distributed amplifier with inductive peaking in circular.

inductor can increase the bandwidth of a cascode stage by several gigahertz. Even in multiple stacked cascode amplifiers, the increased number of inter-stage peaking has an increasing effect on the  $G_m$  (Testa et al., 2015).

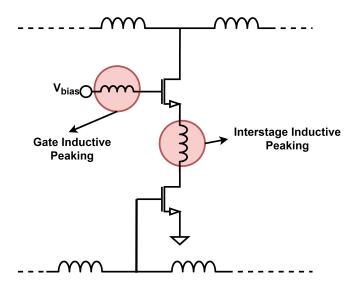

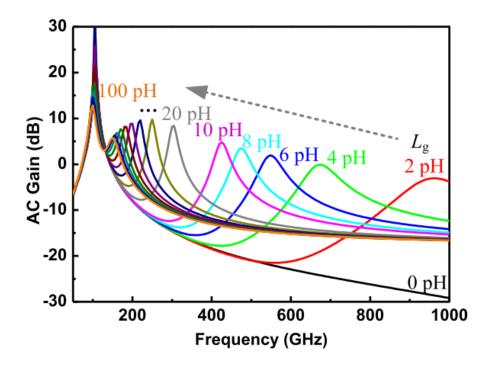

Gate inductive peaking is another way to do transconductance peaking in higher frequencies. In this method, an inductor is placed in the gate of the common gate transistor in Fig. 2.8. As previously discussed, the main problem of the transconductance drop is the capacitances, and this gate inductor can be able to pull the second gm peaking that is in the sub-terahertz region, which can be seen in Fig. 2.9. This way, bandwidth is increased significantly (Feng et al., 2017)

However, increased transconductance from the inductive peaking may result in instability (Kim, 2019). Therefore, the designs should be checked for perfect stability. Also, a major problem arises with peaking, which is the increased area usage from the inductors.

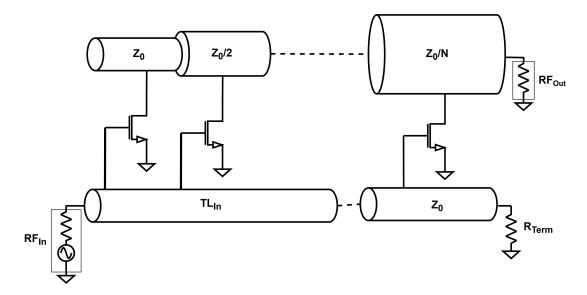

### 2.3.4 Tapered Structures

In a distributed amplifier, half of the drain current from every  $G_m$  cell flows into the drain termination, reducing the available output power by approximately 3 dB. This will significantly reduce the overall efficiency, especially in highly efficient designs. However, that termination resistor simplifies the design by improving stability and eliminating reflections.

Figure 2.9 Effect of gate peaking in various technologies (Feng et al., 2017).

If the design is transmission line-based, this lost current can be saved using tapering the drain transmission line. Instead of using a uniform  $Z_0$  transmission line, tapered structures gradually reduce the impedance stage by stage toward the output. When properly designed, this allows the reverse wave from each cell to be canceled by the left-going wave of the next cell (Ginzton et al., 1948). A commonly used tapering strategy scales the impedance of each drain section inversely with its position, as shown in Eq. 2.25. The schematic design of tapering can be seen in 2.10.

$$(2.25) Z_k = \frac{Z_0}{k}$$

This method is implemented in a cascaded CMOS distributed amplifier using tapered interstage lines. Their results show a gain improvement of more than 6 dB compared to flat-line designs. As the tapering factor increases, gain and efficiency also improve. This method also increases bandwidth with an increase in the tapering coefficient of the design (Tarar et al., 2024).

Tapering helps eliminate the power reduction in internal terminations, but it requires careful design steps due to different transmission lines needed to design, layout parasitics, and loading. The advantageous parts of tapering are only achieved when these factors are well-optimized.

Figure 2.10 Tapered DA

### 2.3.5 Feedback-based distribute amplifiers

In distributed amplifiers, signal loss at higher frequencies is one of the main limitations that reduces gain. Since extending bandwidth is a key goal, many studies focus on compensating for this loss. Common approaches are to either increase the effective transconductance or boost the signal directly through feedback. This has led to two main feedback techniques: intra-stack coupling and ATL coupling.

The first method, intra-stack coupling, is shown in Fig. 2.11. In this structure, the gate peaking inductor and the interstage inductor within the cascode  $G_m$  cell are coupled. This coupling method helps recover the power of the lost signal due to parasitic capacitance at the cascode node and effectively boosts the transconductance  $G_m$  at higher frequencies (El-Aassar & Rebeiz, 2020a; Lee, Park, Choi, Liu & Wang, 2023). This boosting is done by changing the common gate amplifier to work as a common source amplifier and adding a boost to the design. However, since this is a form of positive feedback, it can reduce the stability of the system, so the design must be carefully checked for stability parameters.

The second feedback method, shown in Fig. 2.12, couples the ATLs, inductor or transmission line based, to the gate and drain. This technique focuses on loss along the gate line at higher frequencies. As the signal propagates in the gate line, it weakens due to lossy behavior in the ATL at the higher frequencies. By introducing coupling between the gate and drain lines, this method aims to reinforce the input signal that moves on the gate line and improve gain in the later stages by increasing the signal from the train line of the amplifier (Hsiao, Su & Hsu, 2013; Lee et al.,

Figure 2.11 Intra-stack coupling gain cell

Figure 2.12 Drain-gate line coupling

2023).

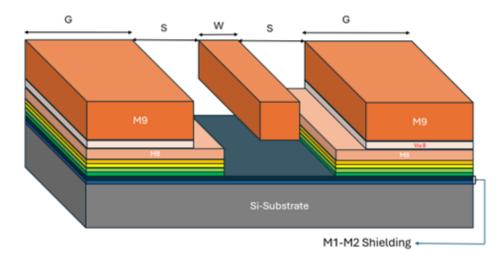

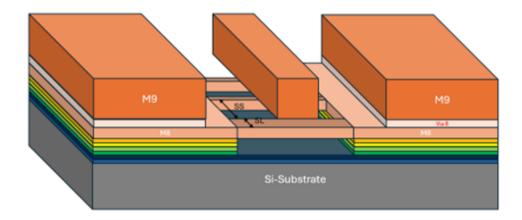

## 2.4 Area Reduction Techniques

Distributed amplifier for UWB applications presents a major problem, which is the on-chip passive components, especially inductors and transmission lines. They are the major area consumers in our chip area. Since distributed amplifier topology inherently relies on multiple stages of lumped inductors or transmission lines to create ATLs, reduction techniques for these passives are essential for efficient area

consumption. In this section, we will be introducing key passive area reduction methods, which are slow-wave transmission lines and different shaped, lower Q, irregular layout, and stacked inductors.

#### 2.4.1 Slow-Wave Transmission Lines

Slow-wave transmission lines (SWTL) are used to reduce the physical length of ATLs by increasing the propagation constant  $\beta$ , allowing a more compact design for distributed amplifiers. This is done by increasing the effective dielectric constant  $\varepsilon_{\text{eff}}$  by adding capacitive loaded structures, such as floating slot-type metals placed beneath the signal line which basically act like bumbs and slows down wave velocity and reduce the wave length.

The phase velocity  $v_p$  and effective dielectric constant  $\varepsilon_{\text{eff}}$  are related as shown in Eq. 2.26. For quasi-TEM transmission lines,  $\varepsilon_{\text{eff}}$  can also be derived from the inductance and capacitance per unit length as given in Eq. 2.27. These equations show that by increasing capacitance directly, the wave velocity can be reduced.

$$(2.26) v_p = \frac{c}{\sqrt{\varepsilon_{\text{eff}}}}$$

(2.27)

$$\varepsilon_{\text{eff}} = \frac{L'C'}{\mu_0 \varepsilon_0}$$

Figure 2.13 shows a conventional coplanar waveguide (CPW) transmission line. While it offers simplicity, it occupies a relatively large footprint for a given electrical length due to its limited  $\varepsilon_{\rm eff}$ . In contrast, the slow-wave transmission line structure shown in Fig. 2.14 incorporates patterned slot-type floating metals to enhance the capacitive effect and compress the line length.

To evaluate the effectiveness of the proposed structure, in paper four, SWTL variants were designed by adjusting the slot length and spacing while keeping the CPW width and gap constant (Yağmurlu & Tokgöz, 2024). Compared to a conventional CPW, the best-performing slow-wave structure exhibited approximately twice the effective dielectric constant and significantly higher propagation constant, which resulted in nearly 30% reduction in physical length. Although the loss slightly increased, the

Figure 2.13 Conventional CPW transmission line (Yağmurlu & Tokgöz, 2024).

Figure 2.14 Slow-wave transmission line (SWTL) with floating slot-type metal structure (Yağmurlu & Tokgöz, 2024).

compactness and improved phase delay make the SWTL a more efficient option for mmWave distributed amplifier designs (Yağmurlu & Tokgöz, 2024).

## 2.4.2 Inductor Design Strategies

On-chip spiral inductors are another key area in RF integrated design. Therefore, there are lots of design strategies that aim to maximize inductance per area or otherwise reduce the inductor size. As previously discussed in CMOS DAs, it is common to use a lumped inductor for high inductance needed ATL designs, or it can be used as a peaking inductor. This widespread use led the researchers to look for minimization methods and which is crucial for designs. In this part of the thesis, we are going to review some approaches for inductors, shapes of inductors, accepting lower Q in-

ductors for size benefits, employing irregular layout, and stacking inductors. Each of the methodology provide an area of saving but with an impact on performance.

## 2.4.2.1 Different Shapes

The geometry of an on-chip spiral inductor influences performance and area. In the literature most commonly used shapes are square, octagonal, and circular spirals. The general rule of thumb is that if a spiral inductor is more symmetric and has a round shape, it has higher Q, while more cornered designs provide higher inductance per area.

A square spiral utilizes nearly 100% of its bounding box, while an octagonal spiral typically covers about 82–83%, and a circular spiral only about 79% (Chen & Liou, 2004). Although circular spirals offer the lowest series resistance due to the lowest distance between ports and the highest Q, they leave considerably unused area than standard rectangular layouts. While square spirals maximize inductance density, but suffer from increased resistance due to sharp corners and longer metal paths. Octagonal spirals are easier to implement than true circles, consume slightly less area than circular spirals, and only marginally compromise on Q-factor (Chen & Hsu, 2022). Also, it is important to note that in IC design, most of the technologies only offer 45 degree angle lines and 90 degree lines for drawing, which makes circular impossible to design while making an octagon, all of which are closest to a circle get their advantage.

#### 2.4.2.2 Stacked Inductors

Stacked inductors are spiral inductors built across multiple metal layers to save area. Instead of the usual single layered inductor design, in this method parallel multiple inductors across different layers and connects to each other. In designs, usually the area below the inductors is unused, therefor stacking inductors in this way, the bottom of the inductors can be used. However, this stacking comes with the disadvantage of increased resistance due to increased line length. Thus, stacked inductors typically have a lower Q with compact designs.

In the literature, examples of stacked inductors can be seen using a 180-nm CMOS

process with four to six layer stacking. It can be seen from the results that when the stacking number increases, the inductance increases significantly. However, it reduces the Q (Yin, Xie, Kang, Shi, Mao & Sun, 2008). This is expected due to increased line length, as a result, resistivity increases worst metalizations are used, which are thinner than the top metals. Also, self-resonant frequency must be considered in design, since stacking leads to a decrease in results. (Yin et al., 2008).

#### 3. DISTRIBUTED POWER AMPLIFIER

Distributed power amplifier (DPA) simultaneously deliver wide bandwidth and high output power, and their stage count scales with the required performance. In this work, a DPA is designed as the final stage of a transmitter. The focus is on achieving wideband gain and wideband high output power, with a compact layout using area reduction methods. The design steps, performance targets, and key trade-offs are presented in this chapter.

## 3.1 Design Considerations of the Power Amplifier

DAs are common in ultra-wideband applications, as previously discussed. Most of the DAs are not optimized for high output power and efficiency, which makes them unsuitable for power applications. In the literature, DPAs have been implemented using various technologies, including bulk CMOS (Kim, 2019; Tarar et al., 2024), SOI CMOS (Celik & Reynaert, 2021; El-Aassar & Rebeiz, 2019a,1,2,2), and SiGe BiCMOS (Fang et al., 2016). In this design, the DPA is intended to serve as the output stage of a transmitter. Unlike regular DAs, their designs mostly focused on producing higher output power. To achieve it, most of the time output is not matched to  $50 \Omega$ , but to a load optimized for maximum power transfer.

Area reduction is a key goal of this thesis. Therefore, to achieve this, vertically stacked and shape-optimized inductors are used to minimize layout size, accepting a lower Q as a trade-off. This enables a more compact design.

Gain cells are biased in Class-A to ensure high linearity and sufficient gain, which is the most common practice in DPAs. Input matching and unconditional stability are maintained across the entire 70 GHz bandwidth.

Recent works based on bulk CMOS, SOI CMOS, and SiGe technologies report out-

put power levels around 14 dBm and average gains of approximately 15 dB. It is worth noting that CMOS SOI-based designs benefit from higher supply voltages (e.g., 4.4 V), which contribute to improved output power and gain. In some cases, cascaded stages are also used to achieve higher gain. This work aims to exceed those performance metrics while maintaining a compact and wideband DPA architecture.

# 3.2 Methodology and Theoretical Calculations

## 3.2.1 Class-A Power Amplifier

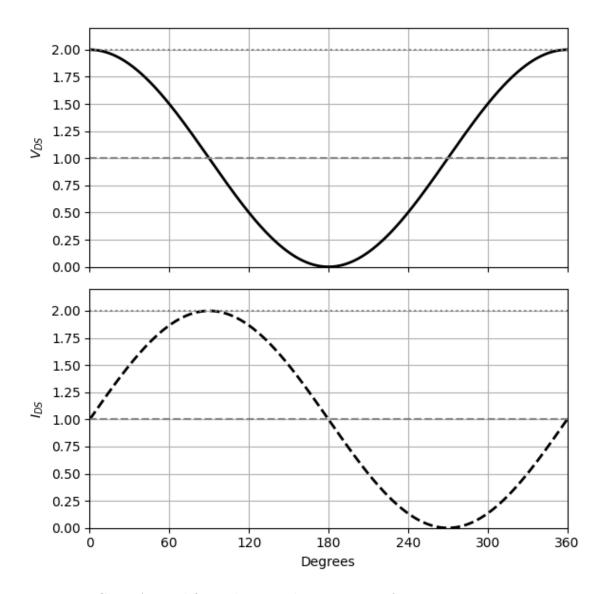

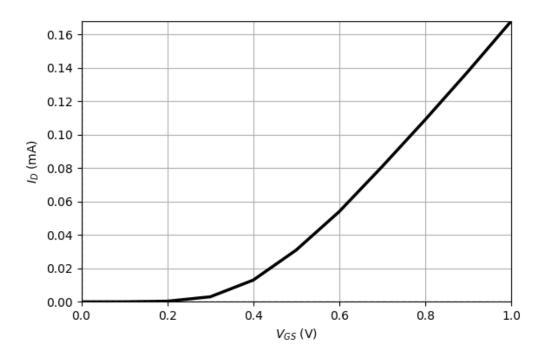

The DPA is biased in Class-A to lock in linear gain over the entire band. Figure 3.1 confirms that  $V_{DS}$  and  $I_{DS}$  swing from 0 to  $2V_{DC}$  and 0 to  $2I_{DC}$ , occupying the full 360° conduction angle. Guided by the  $I_D-V_{GS}$  curve of the **TSMC 65-nm CMOS** process (Fig. 3.2), the gate bias is set above 0.5 V, keeping the device in saturation so distortion stays minimal while high-frequency gain remains usable. Class-A's ideal drain efficiency peaks at 50 % (Lee, 2003); although practical figures are lower, the wide linear region it delivers is indispensable for ultra-wideband DPAs.

# 3.2.2 $G_m$ Peaking

Ultra-wideband DAs suffer from gain reduction at higher frequencies due to the roll-off in the transistor's transconductance,  $g_m$ . This degradation becomes significant when parasitic capacitances dominate the frequency response. To solve this problem, peaking techniques such as interstage inductive peaking and gate inductive peaking have been proposed and widely adopted in DAs. These techniques operate by introducing inductors to resonate with the parasitic capacitances, thereby flattening or boosting the frequency response. To quantitatively evaluate their effect, the frequency-dependent  $G_m(s)$  of various cascode topologies is analyzed in the next paragraphs.

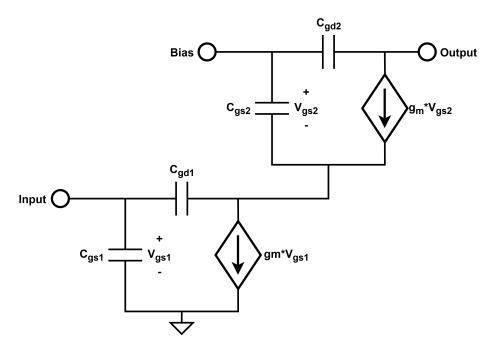

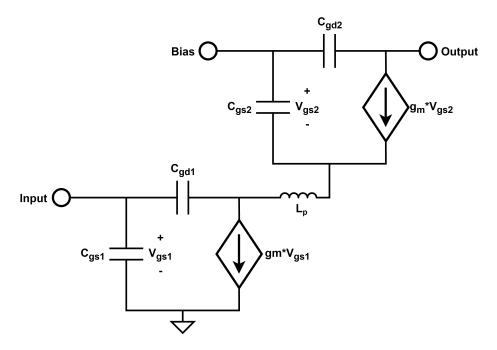

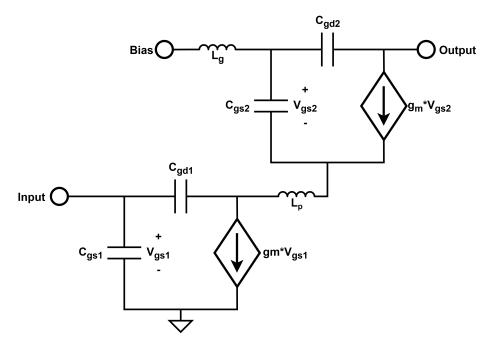

To begin the analysis, small-signal equivalent circuits are drawn for three different

Figure 3.1 Class-A amplifier voltage and current waveforms.

cases: the conventional cascode amplifier, the interstage peaked cascode, and the fully shunt peaked cascode, which has both gate and interstage inductors. These models are illustrated in Fig. 3.3, Fig. 3.4, and Fig. 3.5, respectively. In Fig. 3.3, the standard cascode topology is shown. Fig. 3.4 introduces the interstage inductor  $L_p$ , placed between the common-source and common-gate transistors. Finally, Fig. 3.5 presents the proposed fully shunt peaked structure, in which the gate inductor  $L_g$  is added at the input of the upper transistor to further enhance high-frequency performance.

Figure 3.2  $I_{ds}$  vs  $v_{gs}$  graph of 65-nm CMOS.

Figure 3.3 Small-signal model of cascode FET.

Figure 3.4 Small-signal model with interstage peaking using  $L_p$ .

Figure 3.5 Fully shunt-peaked model with both  $L_p$  and  $L_g$ .

The corresponding analytical expressions for the transconductance  $G_m(s) = \frac{I_{\text{out}}}{V_{\text{in}}}$  are derived for each configuration by applying small-signal analysis. All sources except the input are shorted, and the output is treated as a virtual AC ground. The expression for the conventional cascode is given in Eq. 3.1, where the roll-off is clearly dominated by the parasitic capacitances.

(3.1)

$$G_{m,\text{reg}}(s) = \frac{g_m^2 + g_m s C_{gd1}}{g_m + s C_{gd1} + s C_{gs2}}$$

For the interstage-peaked case with  $L_p$ , the enhancement is introduced by modifying the denominator through the addition of an inductive term:

(3.2)

$$G_{m,\text{int}}(s) = \frac{g_m \left(g_m + sC_{gd1}\right)}{g_m + sC_{gs2} + sC_{gd1} \left(1 + sL_p(g_m + sC_{gs2})\right)}$$

In the fully shunt-peaked case, shown in Eq. 3.3, both  $L_p$  and  $L_g$  are incorporated. The peaking effect is resulted by resonating the  $C_{gd2}$ . As seen in the equation, the inductors  $L_g$  and  $L_p$  are positioned to form resonance with parasitic capacitances such as  $C_{gd2}$ ,  $C_{gs2}$ , and  $C_{gd1}$ , enhancing transconductance by compensating the capacitive roll-off.:

$$G_{m,\mathrm{full}}(s) = \frac{g_m \left( \frac{s^2 L_g C_{gs2}}{1 + s^2 L_g (C_{gd2} + C_{gs2})} - 1 \right) (g_m + s C_{gd1}) s L_p}{1 + \left( C_{gd1} - \frac{1}{s L_p} \right) \left[ 1 + \left( \frac{s^2 L_g C_{gs2}}{1 + s^2 L_g (C_{gd2} + C_{gs2})} - 1 \right) s L_p (g_m + s C_{gs2}) \right] s L_p}$$

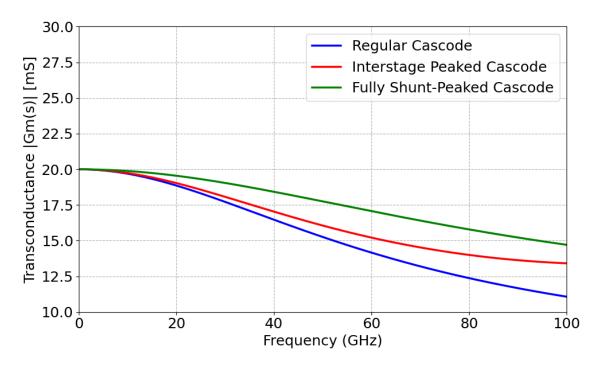

To validate the analytical results, these expressions were evaluated using Python. Fig. 3.6 presents the computed transconductance magnitudes over frequency for all three configurations.

As expected, the regular cascode configuration shows an early decline in  $G_m$  due to the absence of peaking. The interstage-peaked version demonstrates a moderate extension of bandwidth, with slower decay in transconductance, with the exception of an increase after 100 GHz. The fully shunt-peaked version exhibits the best high-frequency performance, maintaining a higher  $G_m$  up to approximately 70 GHz. These results confirm that inter-stage peaking compensates for parasitic loss and extends bandwidth. This is achieved by establishing resonance conditions that boost the response in desired frequency bands, resulting in effective peaking behavior as seen in the plotted  $G_m$ . However, this peaking method results with reduction of stability in higher frequencies due to the upper transistor is shorted by the peaking methods which makes it behave like common source amplifier.

Figure 3.6 Transconductance comparison of regular, interstage, and fully peaking methods in cascode.

### 3.3 Proposed Design Procedures

In this section, we will discuss DAs design procedures, which can be divided into two parts: stage number optimization and passive (inductor) optimizations for area reduction.

## 3.3.1 Stage Number and Cascading Strategy

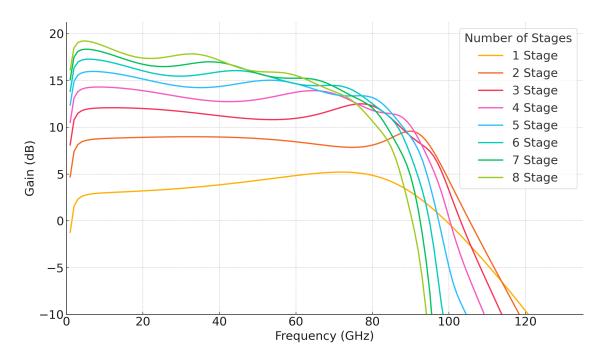

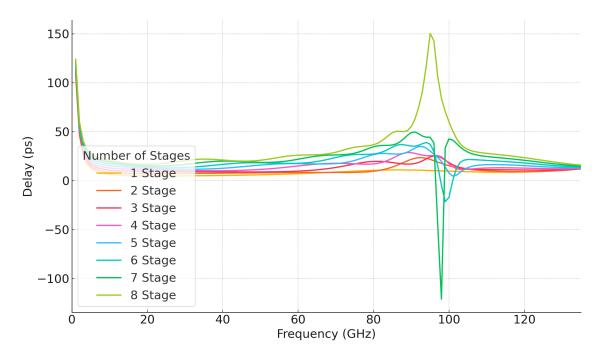

As previously discussed in the background, the number of stages is the most significant factor that needs to be considered in DA design. It was explained that an increased number of stages results in higher gain up to an optimal point and also increases output power. However, it comes with the trade-off of increased area and increased power consumption. Therefore, while designing DAs, the number of stages should be chosen optimally in the specifications' needs.

To determine the optimal number of stages, comparison graphs for different stage numbers needed to be analyzed. For this purpose, using Advanced Design System (ADS), DAs based on 65-nm CMOS were implemented to achieve their optimum