# DESIGN AND REALIZATION OF A HIGH-SPEED 12-BIT PIPELINED ANALOG / DIGITAL CONVERTER IP BLOCK

## by ZEYNEP TOPRAK

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabancı University

Spring 2001

## © Zeynep TOPRAK 2001

All Rigths Reserved

## DESIGN AND REALIZATION OF A HIGH-SPEED 12-BIT PIPELINED ANALOG / DIGITAL CONVERTER IP BLOCK

### APPROVED BY:

Assoc. Prof. Dr. Yusuf LEBLEBİCİ

(Thesis Supervisor)

Turns Chiles

Asistant Prof. Dr. Yaşar GÜRBÜZ

Assoc. Prof. Dr. Naci İNCİ

M. Szihi

Asistant Prof. Dr. İbrahim TEKİN

20HH

DATE OF APPROVAL:

1 4 Eylül 2001

To my parents,

my sister

and

to my Doc.

### ACKNOWLEDGEMENTS

I would like to thank the following persons and organisations who contributed to my thesis.

First, I would like to thank my supervisor Yusuf Leblebici for his excellent support, assistance and knowledge. I was truly lucky to have the opportunity to work with a supervisor like him.

I am grateful to Alcatel Teletas for funding my graduate studies at Sabancı University. As part of an industry-university collaborate agreement I would like to thank Alcatel Microelectronics (AME) group for supporting my thesis as a commercial project.

My special thanks go to Aslı Arslan Eşme and Geert Evens for their technical advice and support, besides their intensive interest in my work.

I would like to thank also the current members of microelectronics group in Alcatel Teletas, for technical suggestions as well as great collegial working atmosphere.

Last, but by no means the least, I am grateful to my family for their patience and encouragement during my education. Finally, I am most indebted to Engin whose love; understanding and patience made it possible for me to be successfull at the end.

## DESIGN AND REALIZATION OF A HIGH-SPEED 12-BIT PIPELINED ANALOG / DIGITAL CONVERTER IP BLOCK

#### ABSTRACT

This thesis presents the design, verification, system integration and the physical realization of a monolithic high-speed analog-digital converter (ADC) with 12-bit accuracy. The architecture of the ADC has been realized as a pipelined structure consisting of four pipeline stages, each of which is capable of processing the incoming analog signal with 4-bit accuracy. A bit-overlapping technique has been employed for digital error correction between the pipeline stages so that the influence of possible errors that occur during analog signal processing can be minimized. The entire circuit architecture is built with a modular approach, consisting of identical blocks organized into an easily expandable pipeline chain.

All analog as well as digital sub-blocks of the ADC architecture presented in this work operate on a single clock signal (and its inverse), which significantly simplifies the design while ensuring a more robust performance. Other important features of this ADC include small area, single power supply, low power consumption, capability to operate at very high sampling clock rates, and the ability to handle a wide range of input signal amplitudes. The analog processing modules were designed using single-ended signals and the single-ended building blocks (as opposed to differential signals and building blocks) for simplicity. The ADC architecture was realized using a conventional 0.18 micron digital CMOS technology (Foundry: UMC), which ensures a lower overall cost and better portability for the design.

The ADC architecture presented in this work is capable of operating at sampling frequencies of up to 200 MHz, and still can achieve the nominal bit-resolution that was

intended for 12-bit accuracy. The entire circuit is designed with single 1.8 V power supply. The maximum range of the input signal amplitude that the ADC can handle is 1.6 Vpp, with 1.8 V supply voltage. The input signal range as well as the operating points of critical components can be adjusted externally using dedicated control pins. The overall power consumption is estimated as 67.5 mW at 200 MHz sampling rate. Each 4-bit pipeline stage consists of a 4-bit flash A/D converter, a fully capacitive multiplying DAC (MDAC) and the corresponding digital encoding circuitry. The overall silicon area of the ADC is approximately 0.25 mm<sup>2</sup>.

The ADC architecture presented in this thesis is intended as a state-of-the-art data converter for very high-speed applications such as digital video transmission or high bandwidth wireless communication needs. It can be used either as a stand-alone single-chip unit, or as an embedded IP block that can be integrated with other modules on chip.

### ÖZET

Bu tez, 12-bit doğrulukla çalışan bir monolitik yüksek hızlı analog-sayısal dönüştürücünün (ADC) tasarımı, sınanması, sistem düzeyinde tümleştirilmesi ve fiziksel tasarımının gerçekleştirilmesi aşamalarından oluşmuştur. ADC'nin mimarisi, herbiri gelen analog işareti 4-bit doğrulukla işleyebilen dört kademeden oluşan bir veri yolu yapısı olarak gerçekleştirilmiştir. Analog işaret işlenmesi sırasında meydana gelebilecek olası hataların etkisini en aza indirebilmek amacı ile veri yolu kademeleri arasındaki sayısal hataları düzeltmek için bir bit-çakıştırma tekniği kullanılmıştır. Devrenin tüm mimarisi, benzer blokların kolayca genişletilebilir bir veriyolu zinciri biçiminde dizilmesinden oluşan, modüler bir yaklaşımla şekillendirilmiştir.

Bu çalışma kapsamında ele alınan ADC mimarisinin tüm analog ve sayısal altblokları, tasarımı belirgin biçimde basitleştirmek ve aynı zamanda blokların daha güvenli olarak çalışmalarını sağlamak amacıyla, tek saat işareti (ve tersi) ile işlem yapabilecek şekilde tasarlanmıştır. Bu ADC'nün diğer önemli özellikleri arasında küçük kırmık alanı, tek güç kaynağı kullanılması, düşük güç gereksinimi, çok yüksek örnekleme hızlarında ve geniş bir giriş işareti genliği alanı içinde çalışabilme kabiliyeti sayılabilir. Çalışma kolaylığı nedeniyle, analog işlem modülleri, diferansiyel işaret ve yapısal bloklar yerine, tek uçlu işaretler ve tek sonlu yapısal bloklar kullanılarak tasarlanmıştır. Bu tezde sunulan ADC mimarisi, daha düşük toplam maliyet ve tasarıma daha iyi taşınabilirlik sağlamak amacıyla, endüstride yaygın olarak kullanılan 0.18 mikron sayısal CMOS teknolojisi (Foundry: UMC) kullanılarak gerçekleştirilmiştir. Tasarlanan dönüştürücü devresi, 200 MHz örnekleme frekansına kadar doğru çalışabilme ve bu yüksek örnekleme hızında hedeflenmiş olan 12-bit çözünürlüğü elde edebilme özelliklerine sahiptir. Devrenin tamamı bir tek 1.8 V güç kaynağı ile beslenebilecek şekilde tasarlanmıştır. ADC'nin 1.8 V besleme gerilimi ile işleyebileceği en yüksek giriş işareti genliği (tepeden tepeye) 1.6 Vpp'dir. Giriş işareti genliği ve bununla birlikte kritik modüllerin çalışma noktaları, denetleme girişleri yardımıyla dışarıdan ayarlanabilir. 200 MHz örnekleme hızında, toplam güç tüketimi 67.5 mW olarak öngörülmektedir. Her 4-bitlik veri yolu kademesi, bir adet 4-bit flash A/D dönüştürücü, bir adet tamamen kapasitif çarpıcı DAC (MDAC) ve bunlarla birlikte çalışacak sayısal çözümleyici devrelerden oluşmaktadır. ADC'nin toplam silikon alanı yaklaşık 0.25 mm²'dir.

Bu tez çalışmasında tasarlanan ADC mimarisi, sayısal görüntü iletimi veya yüksek bant genişliğine sahip telsiz haberleşme gereksinimleri gibi çok yüksek hız gerektiren uygulamalarda kullanılmak amacıyla tasarlanmıştır. Bu dönüştürücü, tek başına bir kırmık olarak veya daha büyük bir kırmık üzerine başka modüllerle birleştirilebilecek bir IP (intellectual property) bloğu olarak kullanılabilir.

### TABLE OF CONTENTS

| 1 | ····Intro | duction                                         | 1  |

|---|-----------|-------------------------------------------------|----|

|   | 1.1       | Serial A/D Converters                           | 4  |

|   | 1.2       | Successive Approximation A/D Converters         | 7  |

|   | 1.3       | Parallel A/D Converters                         | 11 |

| 2 | Perfo     | rmance Measures of Analog-to-Digital Converters | 16 |

|   | 2.1       | Quantization Error                              | 16 |

|   | 2.2       | Quantization Noise                              | 17 |

|   | 2.3       | Dynamic Range                                   | 18 |

|   | 2.4       | Resolution                                      | 19 |

|   | 2.5       | Effective Number of Bits (ENOB)                 | 19 |

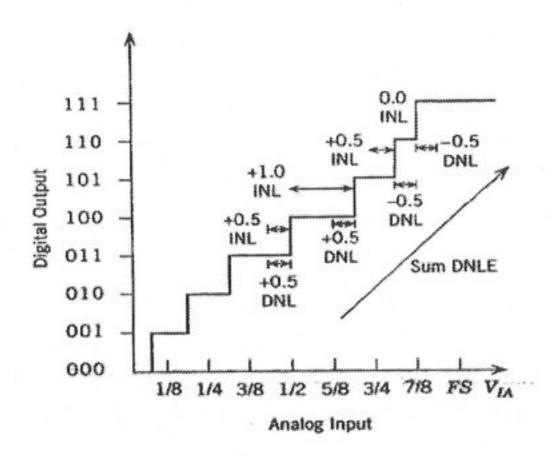

|   | 2.6       | Differential Nonlinearity (DNL)                 | 19 |

|   | 2.7       | Integral Nonlinearity (INL)                     | 20 |

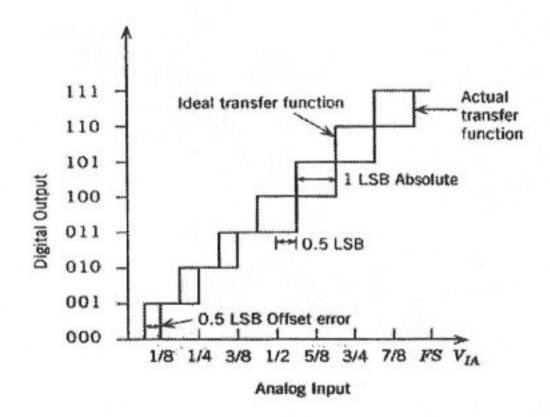

|   | 2.8       | Absolute Accuracy                               | 22 |

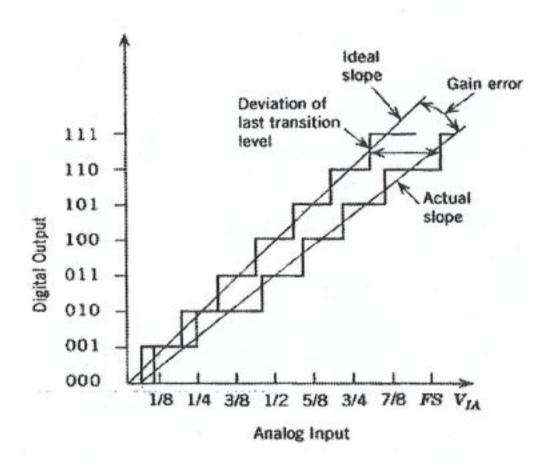

|   | 2.9       | Gain Error                                      | 23 |

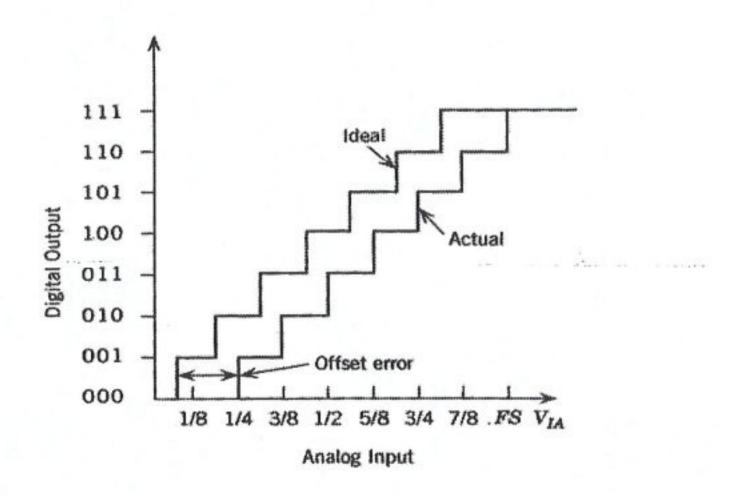

|   | 2.10      | Offset Error                                    | 24 |

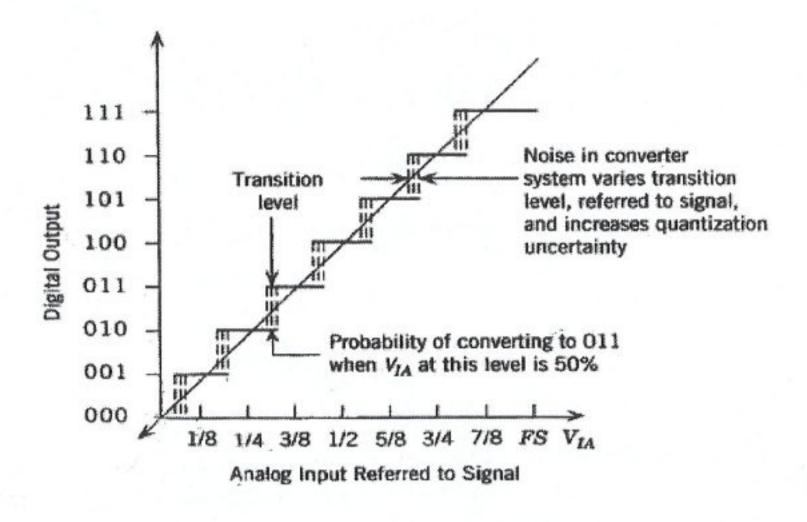

|   | 2.11      | Transition Level                                | 24 |

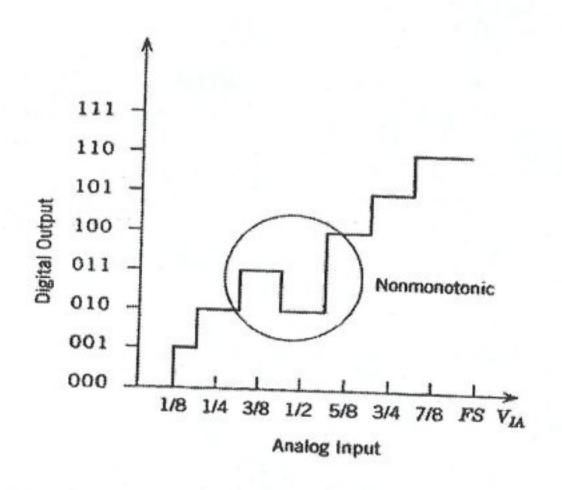

|   | 2.12      | Monotonicity                                    | 26 |

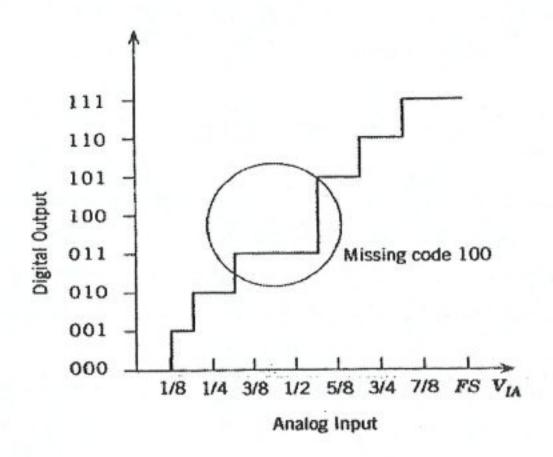

|   | 2.13      | Missing Code                                    | 26 |

|   | 2.14      | Differential Phase and Gain                     | 27 |

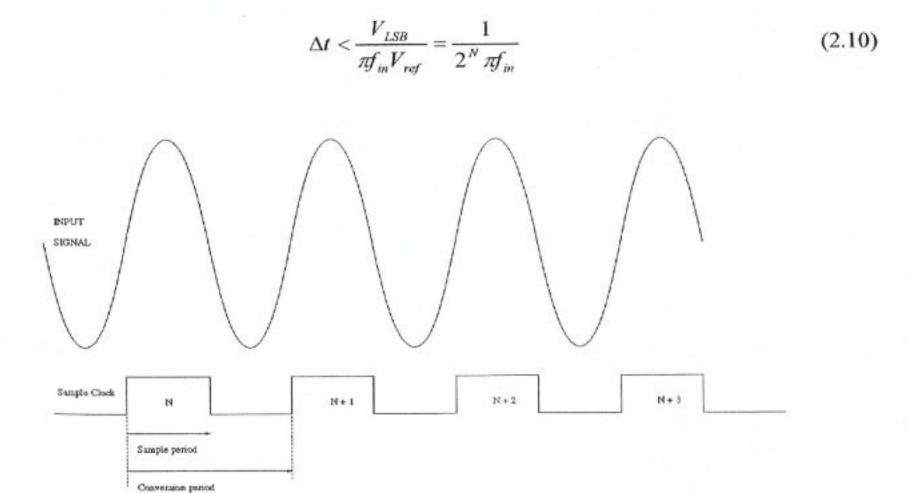

|   | 2.15      | Conversion Time and Sampling Rate               | 27 |

|   | 2.16      | Sampling-Time Uncertainty                       | 28 |

|   | 2.17      | Input Bandwidth                                 | 29 |

| 3 | Pipel | ned Analog-to-Digital Converters 30                            |       |  |

|---|-------|----------------------------------------------------------------|-------|--|

|   | 3.1   | Pipelined Operation                                            |       |  |

|   | 3.2   | Circuit Implementation of a Pipeline Stage41                   |       |  |

|   | 3.3   | Matlab Simulation Results                                      |       |  |

| 4 | Arch  | tecture Components: Voltage Comparator Design 51               |       |  |

|   | 4.1   | Pipelined ADC Architecture Overview                            |       |  |

|   | 4.2   | Voltage Comparators: Basic Concepts                            |       |  |

|   |       | 4.2.1 Model of a voltage comparator                            |       |  |

|   |       | 4.2.2 Examples of CMOS comparator circuits                     |       |  |

|   | 4.3   | Examples of State-of-Art Voltage Comparators                   |       |  |

|   | 4.4   | Proposed Voltage Comparator Architecture                       |       |  |

|   |       | 4.4.1 Basic comparator circuit                                 |       |  |

|   |       | 4.4.2 Full complementary voltage comparator                    |       |  |

|   |       | 4.4.3 Improved full complementary voltage comparator 79        |       |  |

|   |       | 4.4.4 Low power version of the complementary comparator 93     | 10.20 |  |

| 5 | Arch  | tecture Components: High-Speed Op-amp Design 95                | ,     |  |

|   | 5.1   | Introduction of Basic Concepts95                               |       |  |

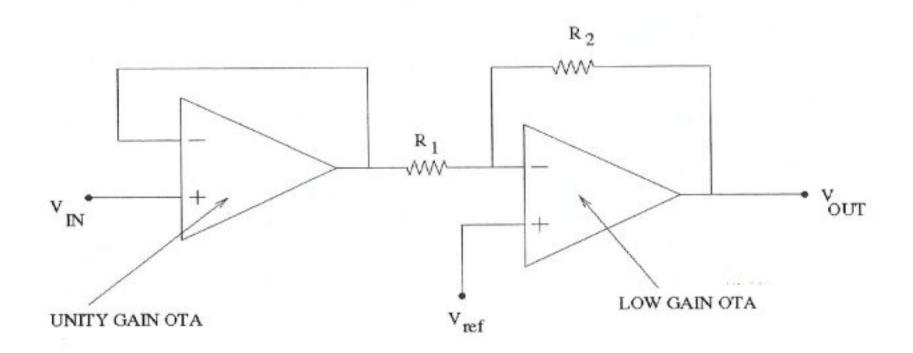

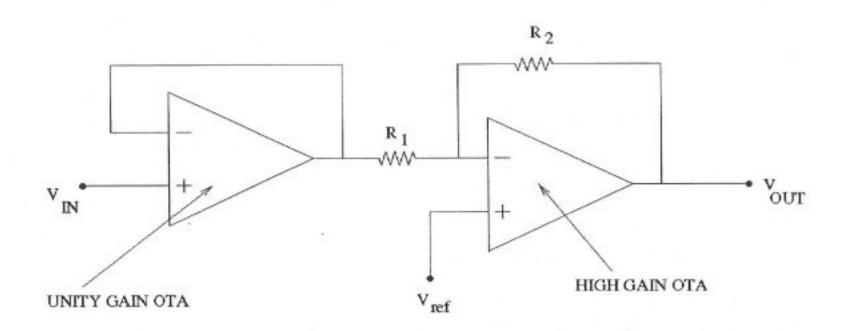

|   | 5.2   | OTA Based Op-amp Design Flow                                   |       |  |

|   | 5.3   | Inverter-Based Output Stage Frequency Analysis                 | 8     |  |

|   | 5.4   | OTA Based High-Gain Op-amp Design 110                          |       |  |

|   | 5.5   | OTA Based Low-Gain Op-amp Design                               | 0     |  |

|   | 5.6   | OTA Based Op-amp Designed for Unity Gain Configuration 12      | 6     |  |

| 6 | Desi  | n of ADC/MDAC Pipeline Stages                                  | 6     |  |

|   | 6.1   | Design of the 4-Bit Flash A/D Converter                        | 8     |  |

|   | 6.2   | Digital-to-Analog Converter Design                             | 4     |  |

|   |       | 6.2.1 Current weighting D/A converter using ladder networks 14 | 5     |  |

|   |       | 6.2.2 Self-calibrating D/A converters                          | 6     |  |

|   |       | 6.2.3 Voltage and charge-scaling D/A converters                | 6     |  |

|   | 6.3   | Error Correction with Bit-Overlapping                          | 9     |  |

| 7   | Desig    | n of Digital Buildi                         | ng Blocks                        | 163 |

|-----|----------|---------------------------------------------|----------------------------------|-----|

|     | 7.1      | Full Adder Design                           | n                                | 163 |

|     |          | 7.1.1 Single-b                              | it adders                        | 164 |

|     |          | 7.1.2 Bit-para                              | llel adder                       | 167 |

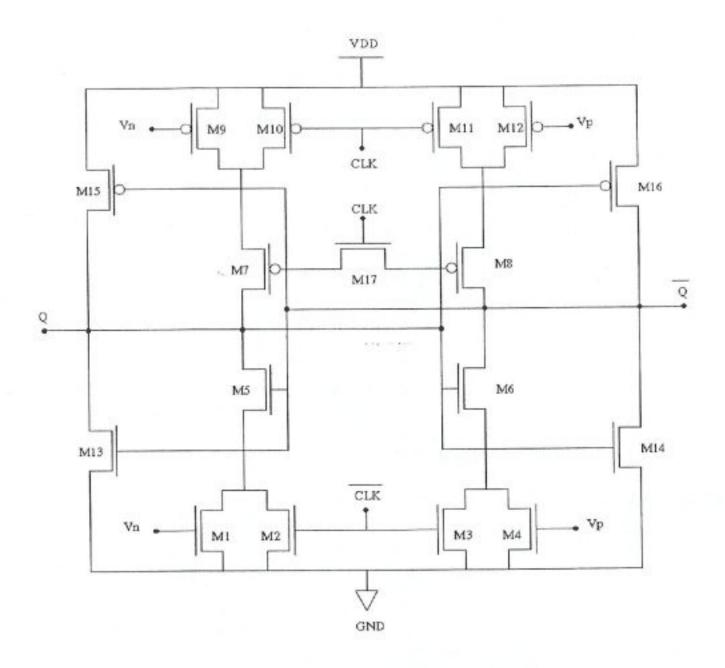

|     | 7.2      | D-type Flip-Flop                            | (DFF) Design                     | 169 |

|     | 7.3      | Exclusive OR Ga                             | te Design                        | 173 |

| 8   | Тор-     | Top-Level Construction of the Pipelined ADC |                                  | 177 |

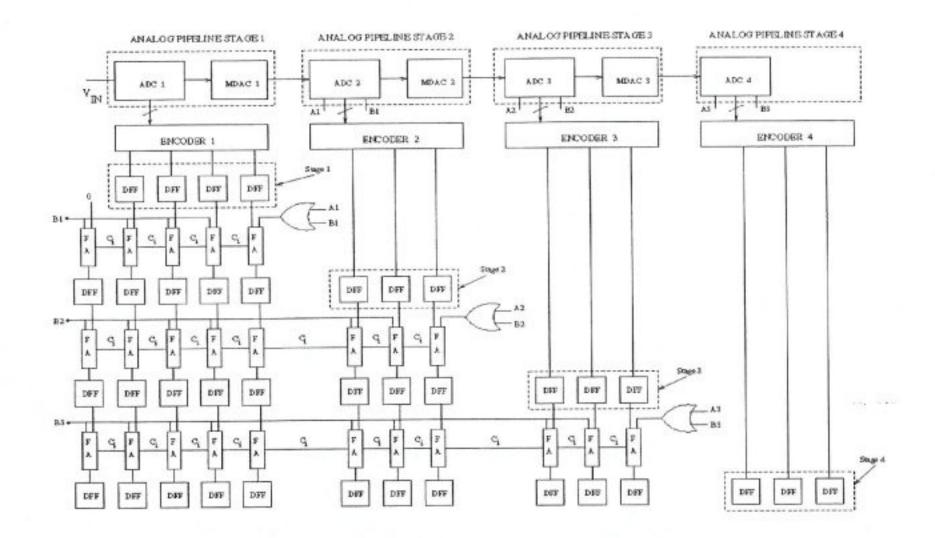

|     | 8.1      | Overall Structure                           | of the Pipeline                  | 177 |

|     | 8.2      | Timing Considera                            | ations                           | 179 |

|     | 8.3      | General Floor-Pla                           | anning and Layout Considerations | 181 |

| 9   | Con      | lusions                                     |                                  | 186 |

| A   | Lite     | ature Survey on A                           | nalog-to-Digital Converters      | 189 |

| В   | Con      | plete Circuit Sche                          | matics and Mask Layouts          | 201 |

| Bib | liograpl | у                                           |                                  | 214 |

## LIST OF FIGURES

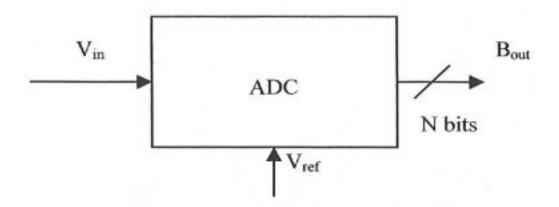

| 1.1  | Black box representation of an A/D converter                                |

|------|-----------------------------------------------------------------------------|

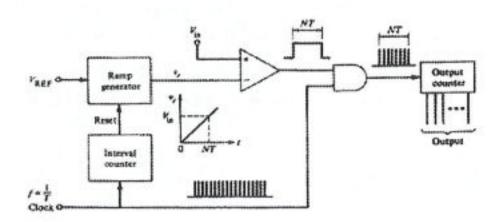

| 1.2  | Block diagram of single slope serial A/D converter 4                        |

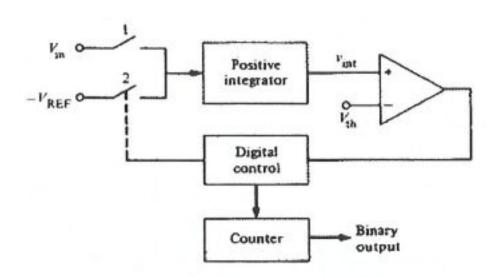

| 1.3  | Block diagram of a dual-slope A/D converter 5                               |

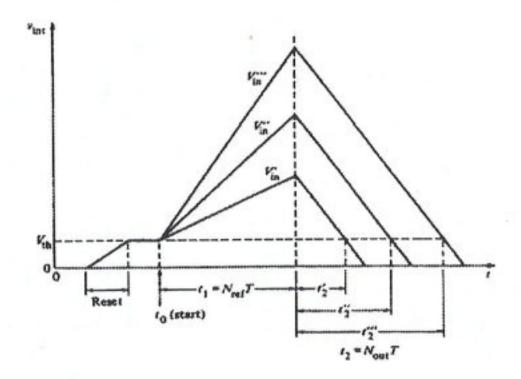

| 1.4  | Waveforms of the dual-slope A/D converter in Figure 1.3 6                   |

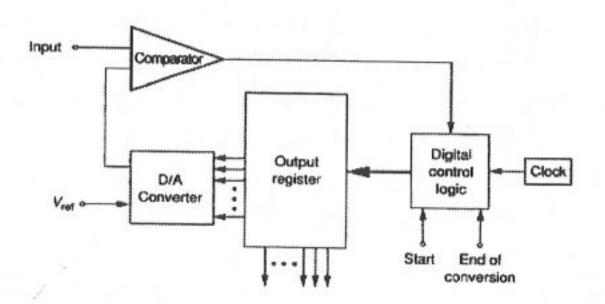

| 1.5  | Example of successive approximation A/D converter                           |

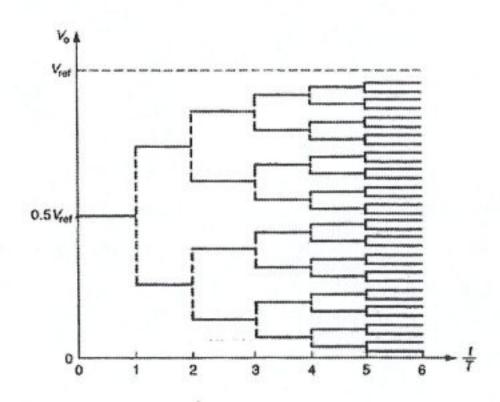

| 1.6  | The successive approximation process 8                                      |

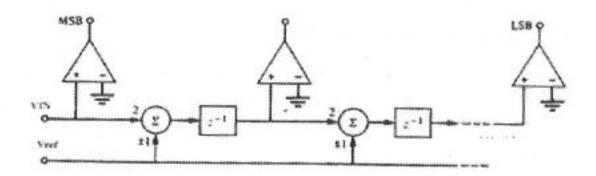

| 1.7  | Pipeline implementation of the algorithmic A/D converter                    |

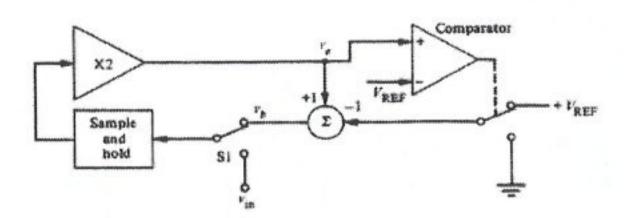

| 1.8  | Implementation of the iterative, algorithmic A/D converter                  |

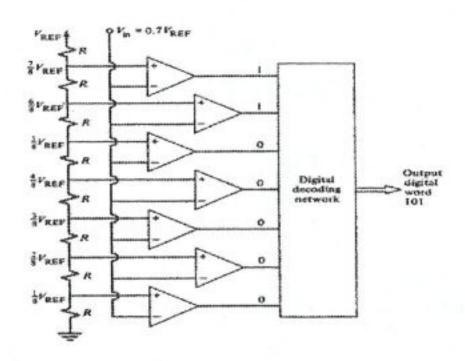

| 1.9  | A 3-bit, parallel (flash) A/D converter                                     |

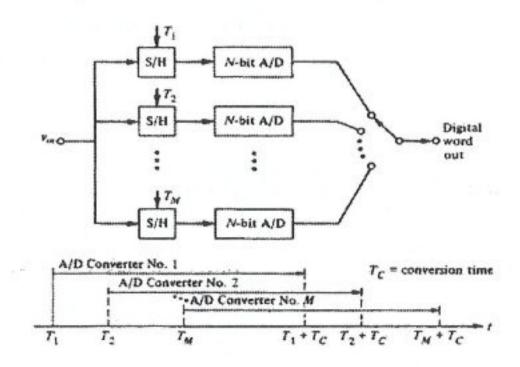

| 1.10 | A time-interleaved A/D converter array                                      |

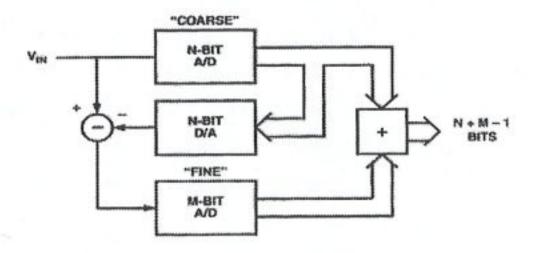

| 1.11 | Block representation of two-step flash A/D converter architecture           |

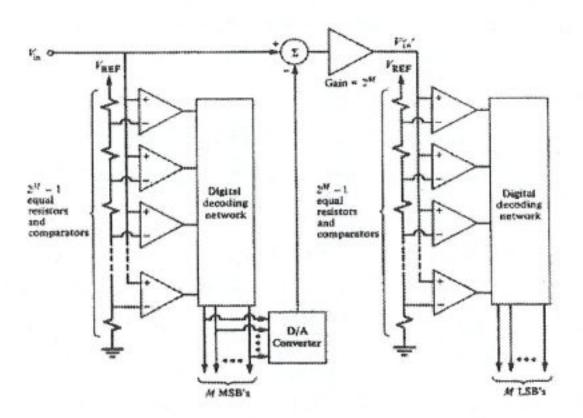

| 1.12 | Two-stages pipelined A/D converter configuration                            |

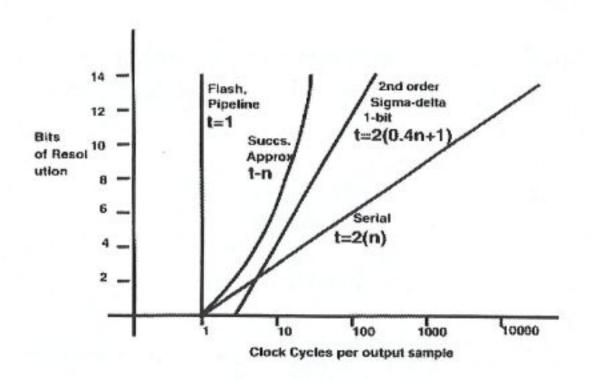

| 1.13 | Qualitative comparison of ADC techniques                                    |

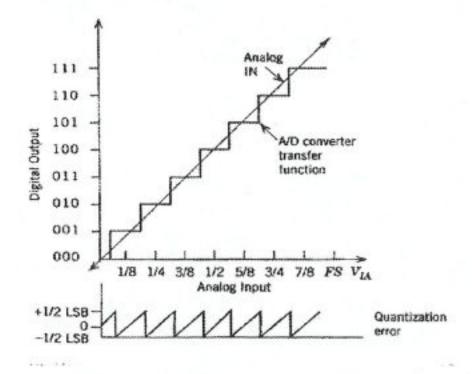

| 2.1  | Input-output characteristics of an ideal 3-bit A/D converter and its        |

|      | quantization error                                                          |

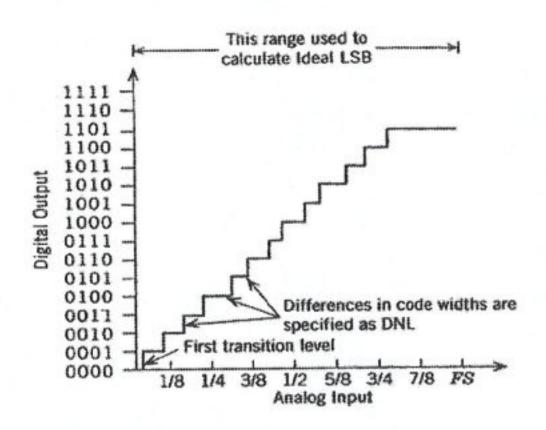

| 2.2  | Illustration of DNL                                                         |

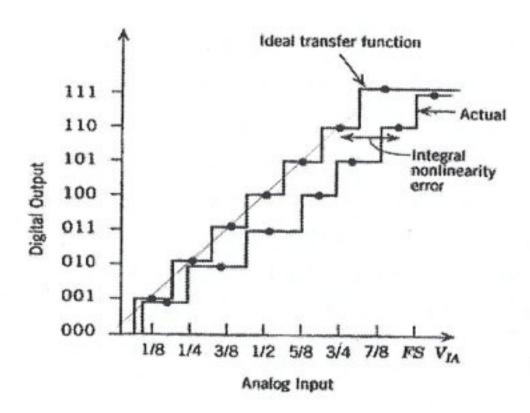

| 2.3  | Illustration of INL for a 3-bit A/D converter                               |

| 2.4  | Relation of DNL and INL                                                     |

| 2.5  | Absolute accuracy is the summation of other error sources                   |

| 2.6  | Illustration of gain error                                                  |

| 2.7  | Illustration of offset error                                                |

| 2.8  | Illustration of transition level                                            |

| 2.9  | A nonmonotonic ADC transfer function                                        |

| 2.10 | An ADC transfer function with a missing code (100)                          |

| 2.11 | Illustration of sample period and conversion time                           |

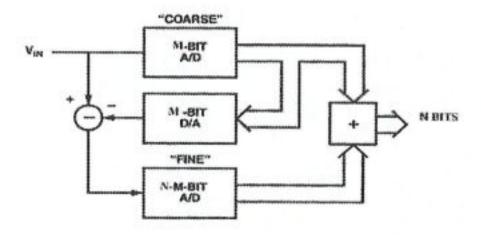

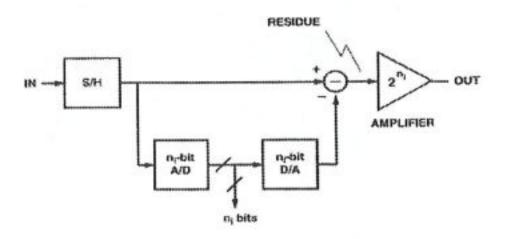

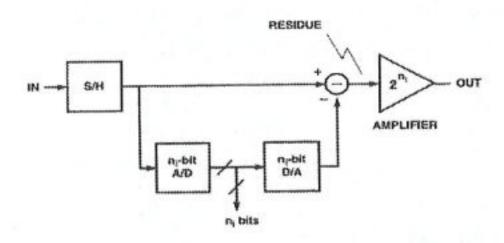

| 3.1  | Typical two-step A/D converter architecture                                 |

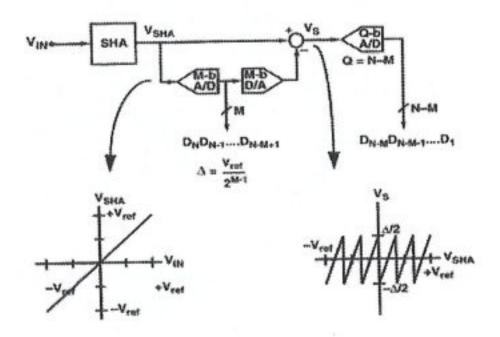

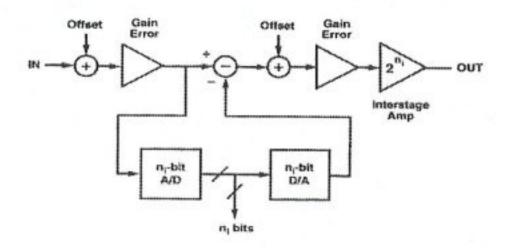

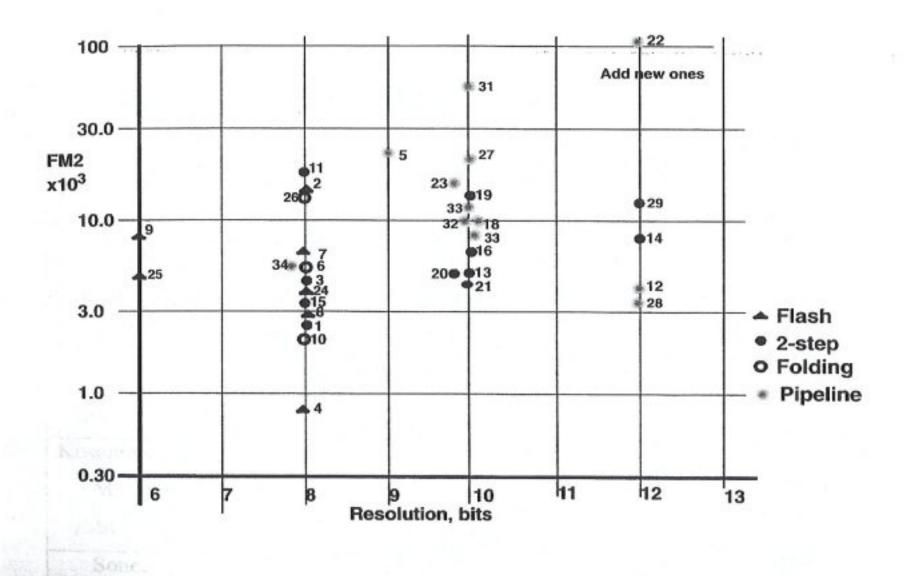

| 3.2  | Multi-step A/D converter figure of performance illustration                 |

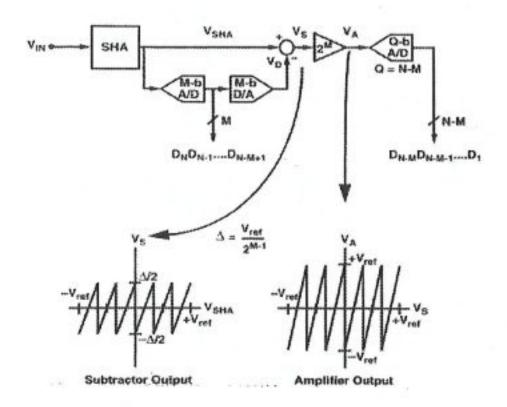

| 3.3  | Multi-step A/D converter's figure of performance illustration with internal |

|      | amplification                                                               |

|      |                                                                             |

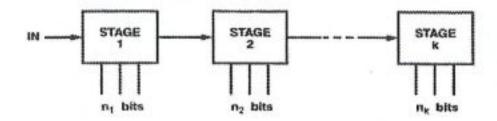

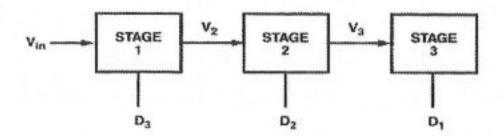

| 3.4  | A simple pipelined A/D converter architecture33                               |

|------|-------------------------------------------------------------------------------|

| 3.5  | Implementation of i <sup>th</sup> stage of a pipelined converter              |

| 3.6  | A pipelined A/D converter architecture model with offset and gain error       |

|      | for both the S/H amplifier and the residue amplifier35                        |

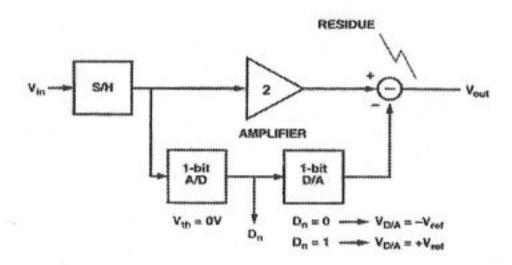

| 3.7  | A 3-bit (1-bit per stage) pipelined A/D converter35                           |

| 3.8  | Implementation of each stage of Figure 3.735                                  |

| 3.9  | The transfer function of the 1-bit stage shown in Figure 3.8                  |

| 3.10 | Transfer function of 3-bit pipelined A/D converter                            |

| 3.11 | Detailed transfer function characteristics                                    |

| 3.12 | Comparison of speed figure of merit, between Flash, 2-Step and                |

|      | Pipelined ADCs                                                                |

| 3.13 | Comparison of power figure of merit, between Flash, 2-Step and                |

|      | Pipelined ADCs39                                                              |

| 3.14 | Implementation of i <sup>th</sup> stage of a pipelined converter              |

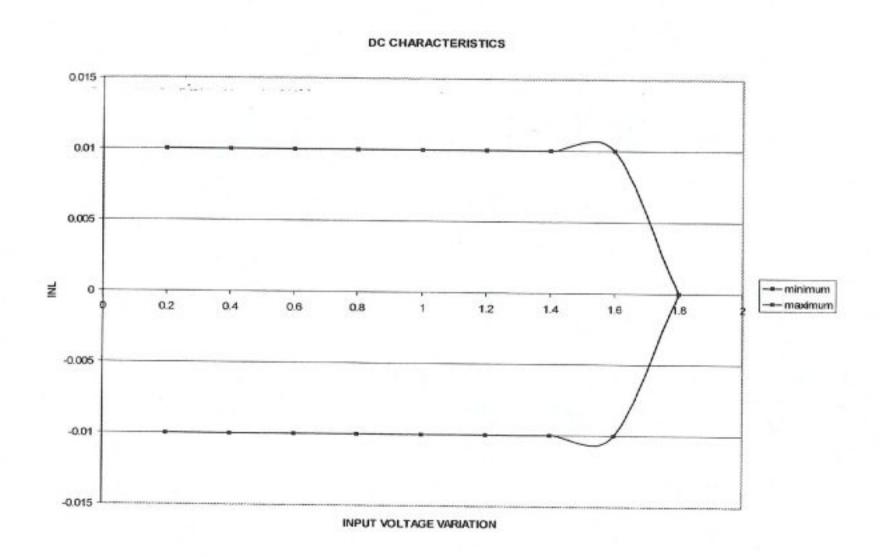

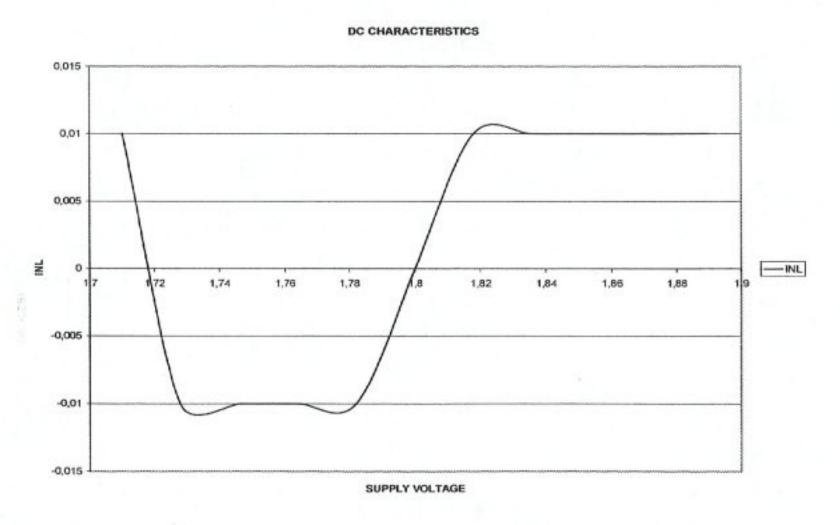

| 3.15 | INL envelope obtained for different input voltage ranges                      |

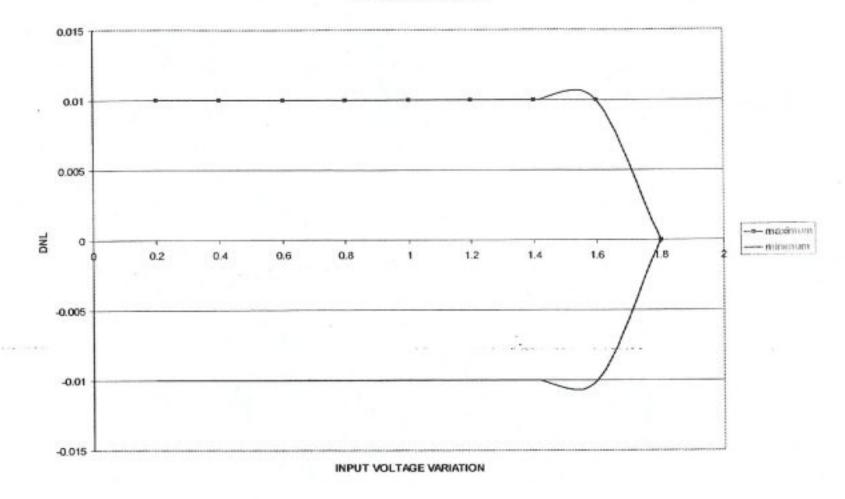

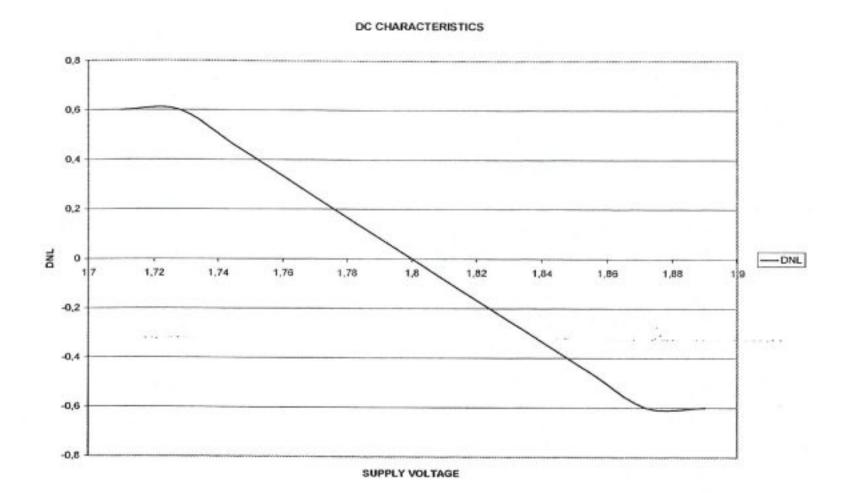

| 3.16 | DNL envelope obtained for different input voltage ranges                      |

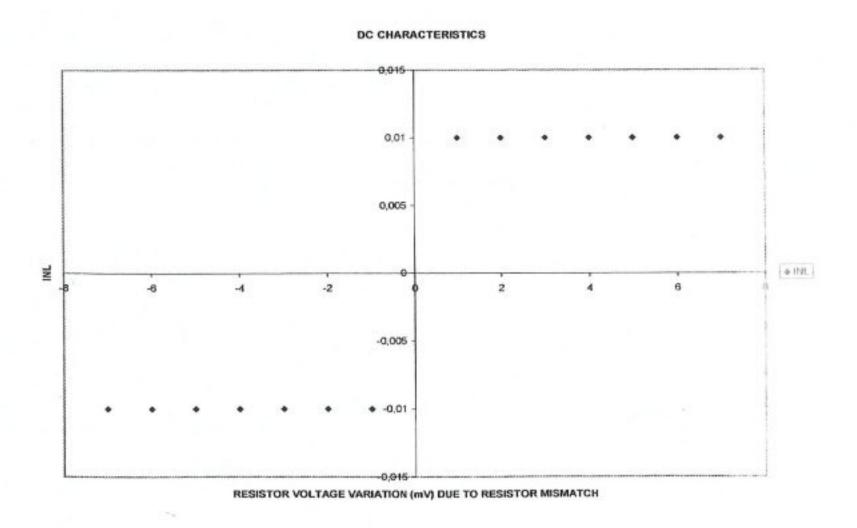

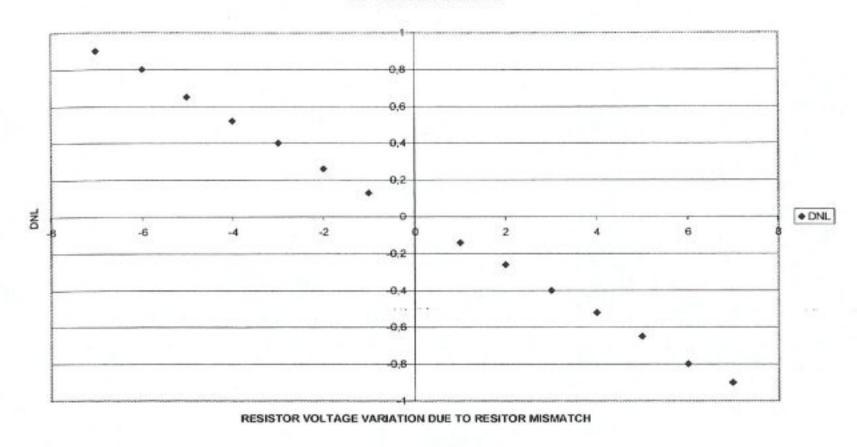

| 3.17 | INL envelope obtained for different resistor voltage variations               |

| 3.18 | DNL envelope obtained for different resistor voltage variations               |

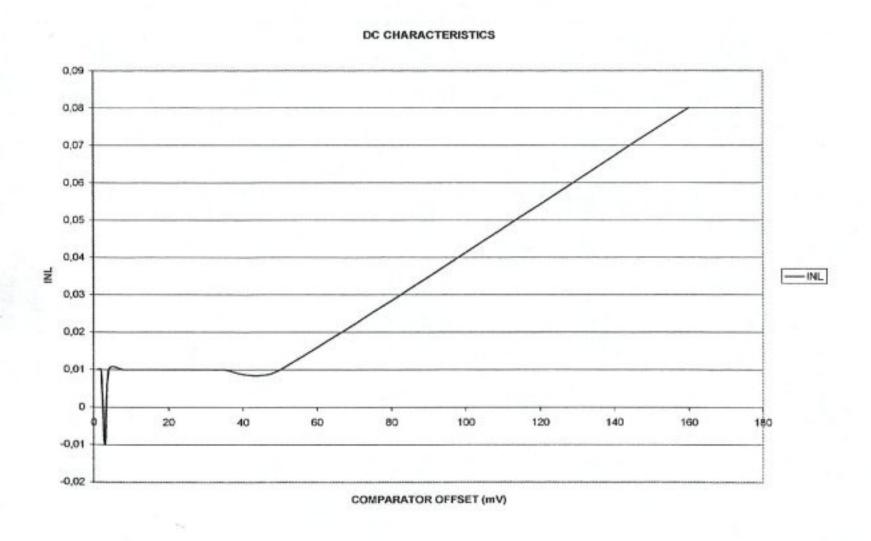

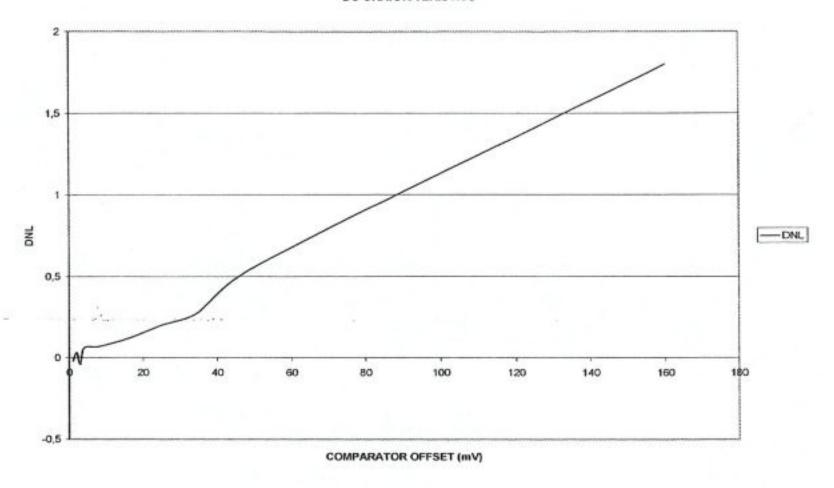

| 3.19 | INL envelope obtained for different comparator offsets                        |

| 3.20 | DNL envelope obtained for different comparator offsets                        |

| 3.21 | INL envelope obtained for different supply voltage variations                 |

| 3.22 | DNL envelope obtained for different supply voltage variations                 |

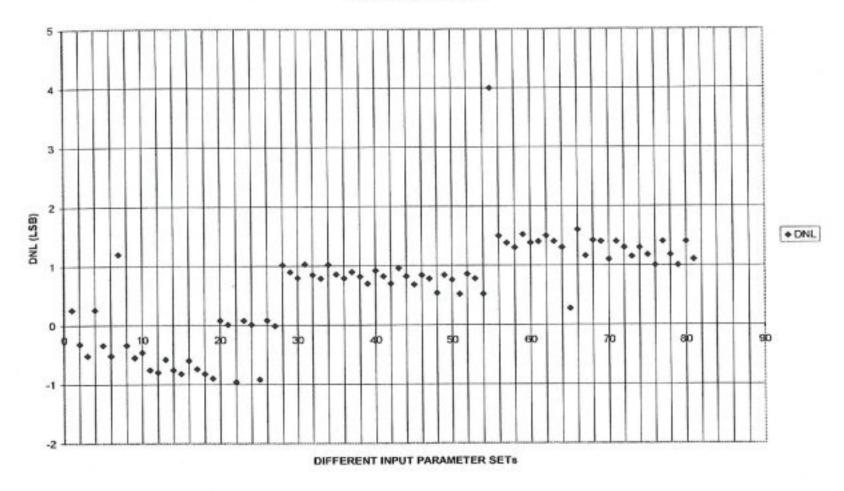

| 3.23 | INL envelope obtained for combined parameter set simulations                  |

| 3.24 | DNL envelope obtained for combined parameter set simulations 50               |

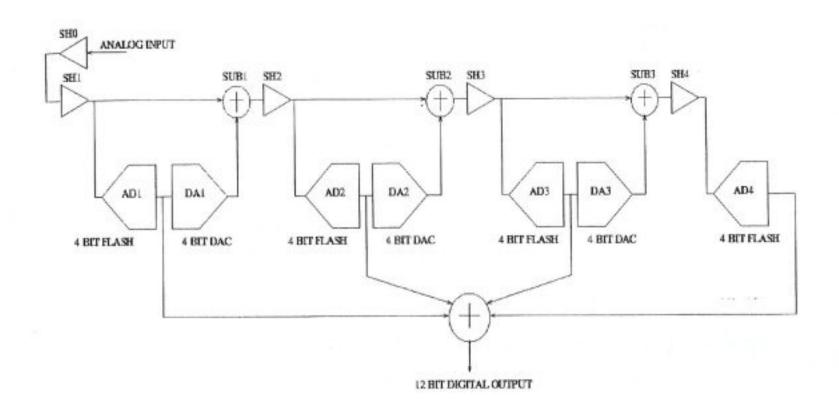

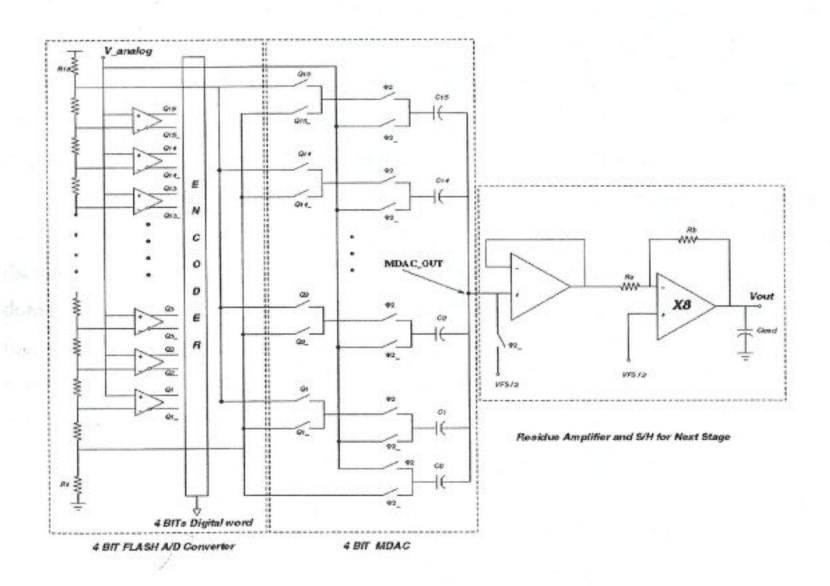

| 4.1  | Simplified block diagram of the proposed A/D converter architecture 52        |

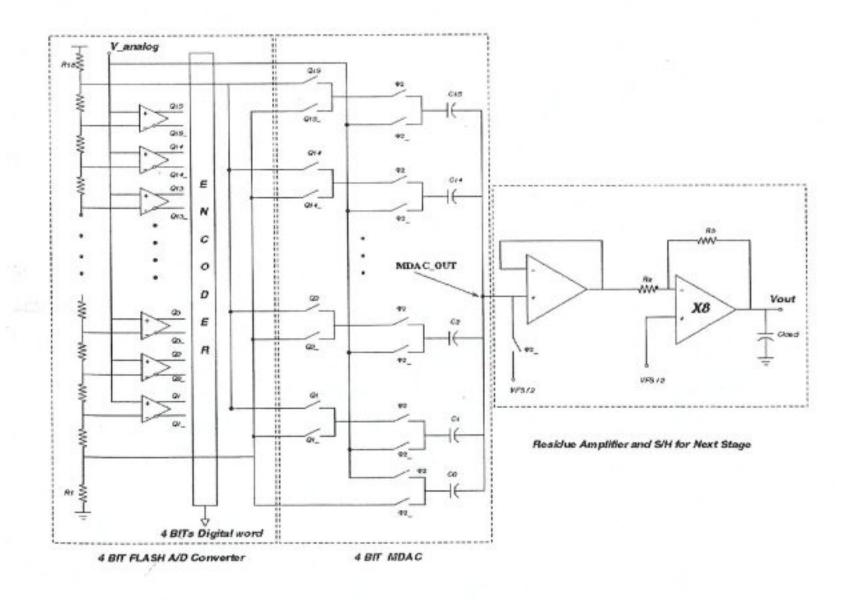

| 4.2  | Detailed circuit architecture for one of the four proposed pipeline stages 52 |

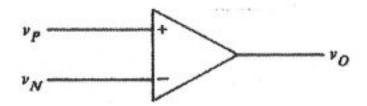

| 4.3  | Circuit symbol for a comparator54                                             |

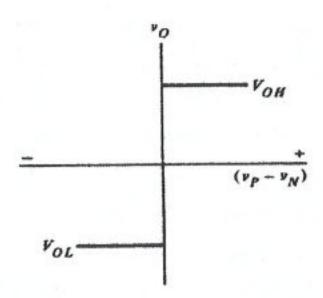

| 4.4  | Zero-order transfer curve of a comparator                                     |

| 4.5  | Zero-order model for a comparator55                                           |

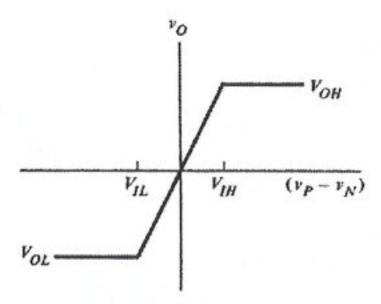

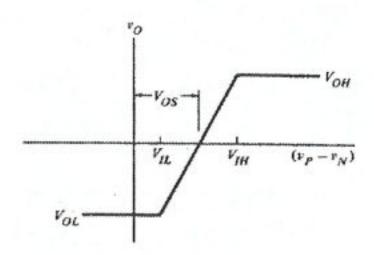

| 4.6  | First-order transfer curve of a comparator                                    |

| 4.7  | First-order model of comparator                                               |

| 4.8  | First-order transfer curve of a comparator including offset                   |

| 4.9  | First-order model of a comparator including offset. The ± sign of the         |

|      | offset voltage accounts for the fact that Vos is unknown in polarity 57       |

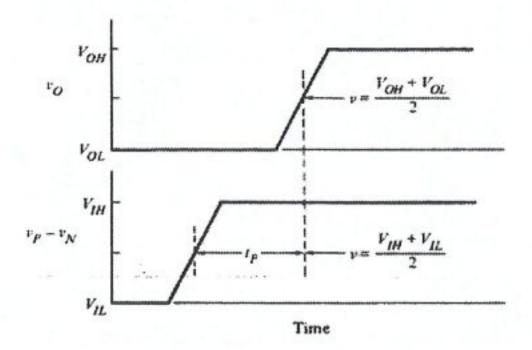

| 4.10 | Time domain response of a non-inverting first-order comparator 58                |

|------|----------------------------------------------------------------------------------|

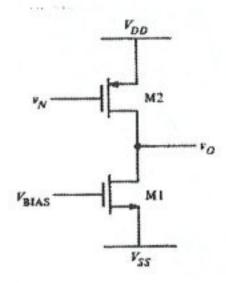

| 4.11 | Current-sink inverter functioning as a comparator 59                             |

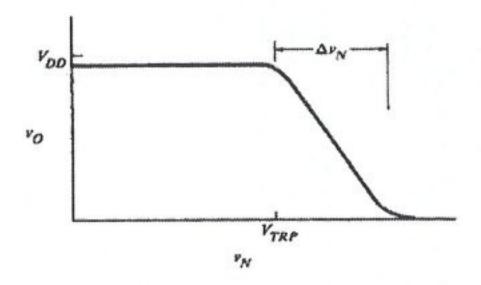

| 4.12 | DC transfer curve of simple comparator59                                         |

| 4.13 | Differential voltage comparator schematic                                        |

| 4.14 | DC transfer curve of a differential voltage comparator                           |

| 4.15 | Two-stage voltage comparator61                                                   |

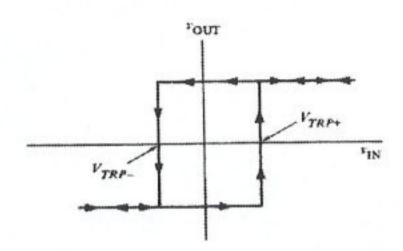

| 4.16 | Comparator hysteresis curve                                                      |

| 4.17 | Comparator with hysteresis applied to the input differential stage only 63       |

| 4.18 | (a) Comparator response to a noisy input (b) Comparator response to              |

|      | noisy input when hysteresis is added63                                           |

| 4.19 | (a) Circuit implementation of an auto-zeroed comparator (b) Comparator           |

|      | during φ <sub>1</sub> auto-sero state (c) Comparator during φ <sub>2</sub> state |

| 4.20 | A two-stage comparator that has a preamplifier and a positive-feedback           |

|      | track-and-latch state                                                            |

| 4.21 | A two-stage comparator 66                                                        |

| 4.22 | A two-stage comparator with capacitive coupling to eliminate input-offset        |

|      | voltage and clock-feedthrough errors along with positive-feedback for fast       |

|      | operation                                                                        |

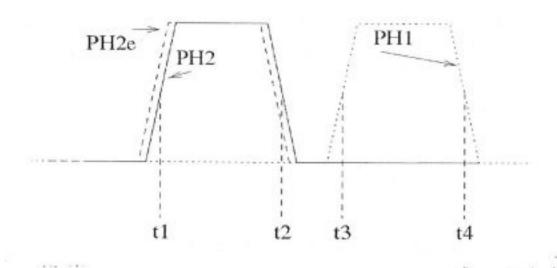

| 4.23 | The clock waveforms required by the comparator in Figure 4.22                    |

| 4.24 | A fully differential comparator with two nonoverlapping clocks by                |

|      | Lewis and Hurst                                                                  |

| 4.25 | A comparator by Razavi an Wooley69                                               |

| 4.26 | A fully differential, high-speed voltage comparator 70                           |

| 4.27 | Timing information for the comparator given in Figure 4.26                       |

| 4.28 | Regeneration process small signal equivalent                                     |

| 4.29 | Basic voltage comparator schematic                                               |

| 4.30 | Output waveforms of basic voltage comparator circuit                             |

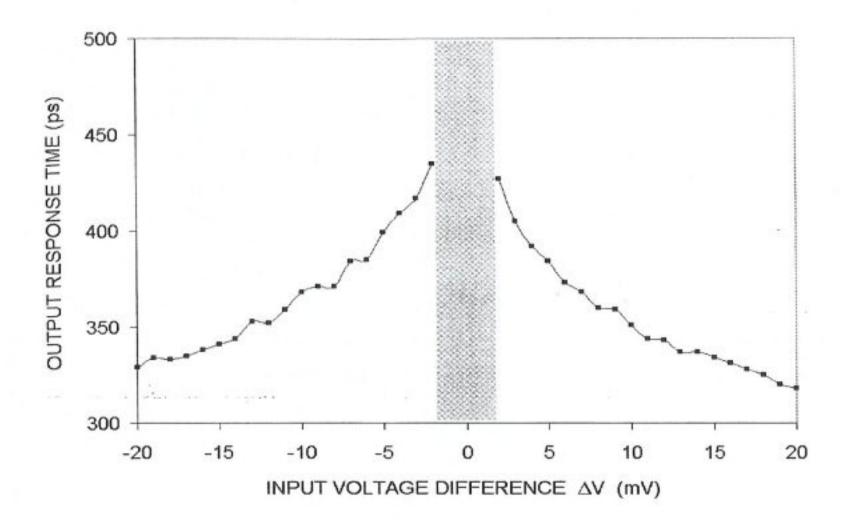

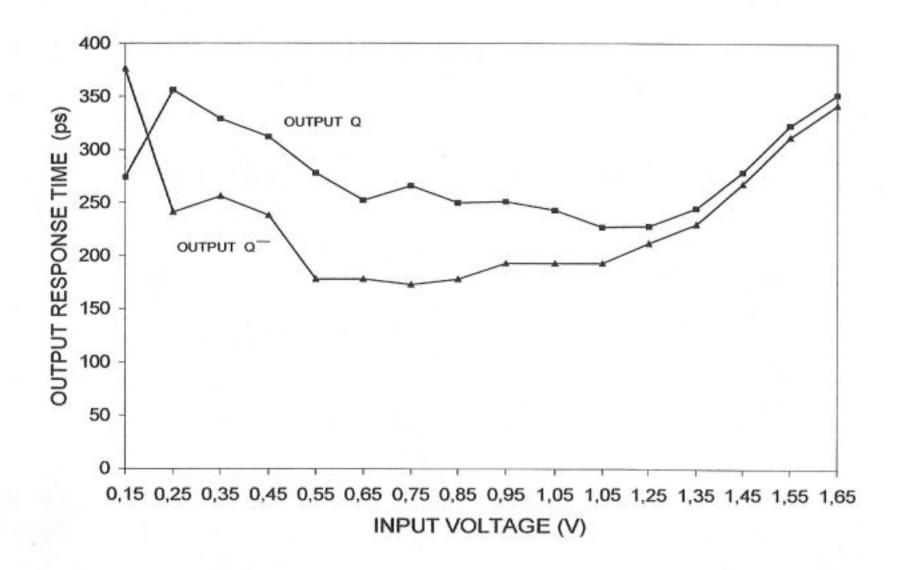

| 4.31 | Response time v.s input voltage difference                                       |

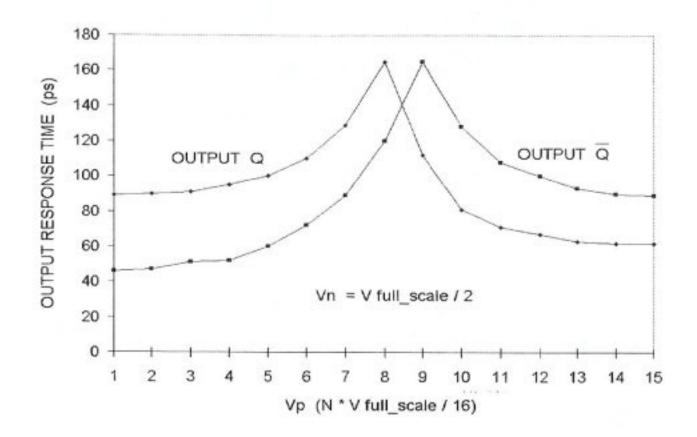

| 4.32 | Response time variation along the entire input dynamic range for basic           |

|      | voltage comparator (V <sub>full-scale</sub> = 1.8V)                              |

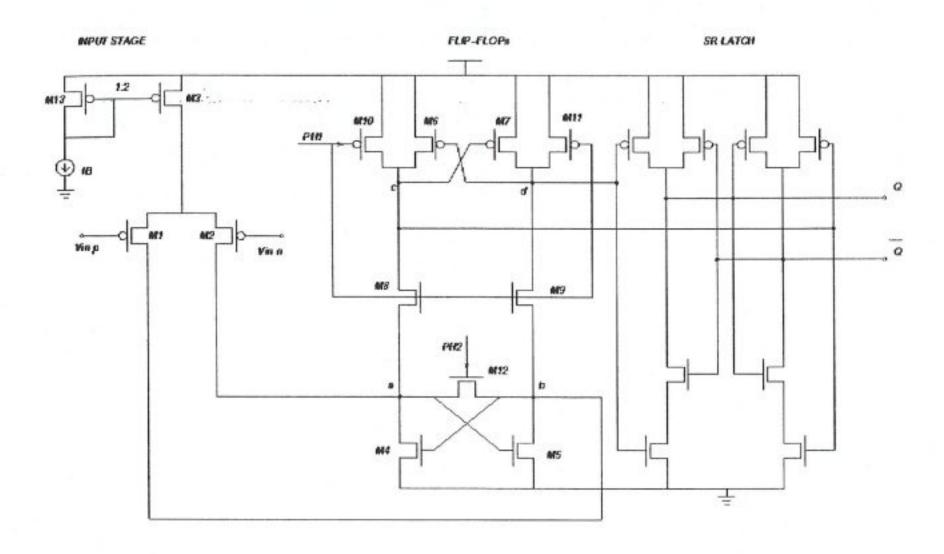

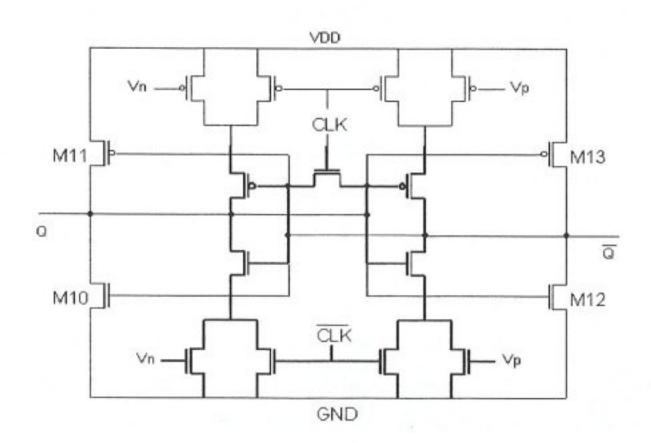

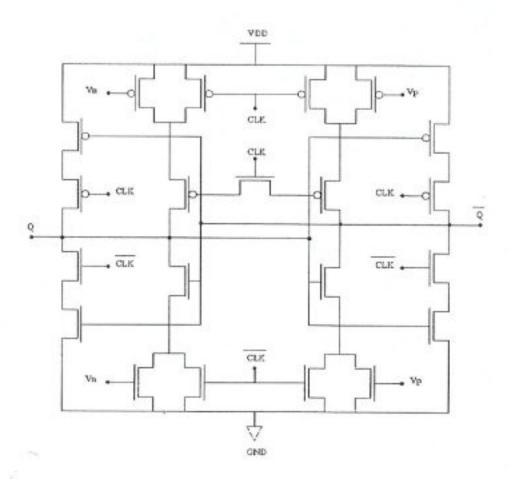

| 4.33 | Fully-complementary voltage comparator circuit diagram                           |

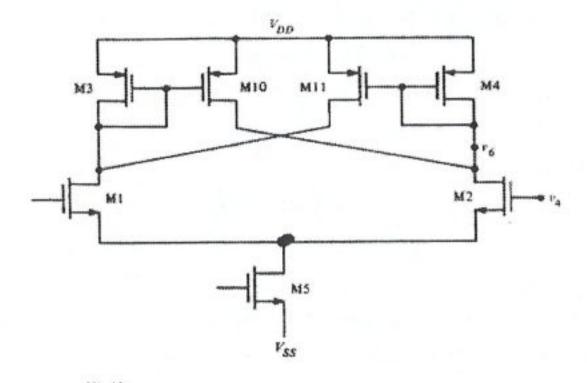

| 4.34 | Improved full complementary voltage comparator circuit                           |

| 4.35 | Response time of improved full complementary comparator with respect             |

|      | to input voltage difference                                                      |

| 4.36 | Response times of the improved full complementary voltage comparator,               |

|------|-------------------------------------------------------------------------------------|

|      | obtained for the entire input range81                                               |

| 4.37 | Response times obtained for different input voltage differences                     |

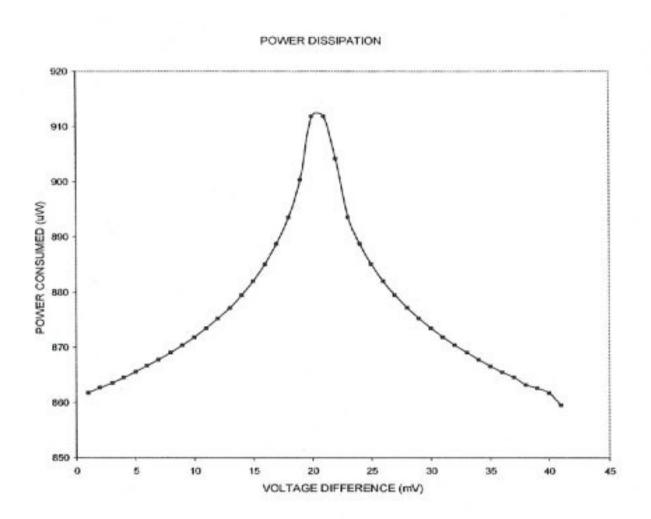

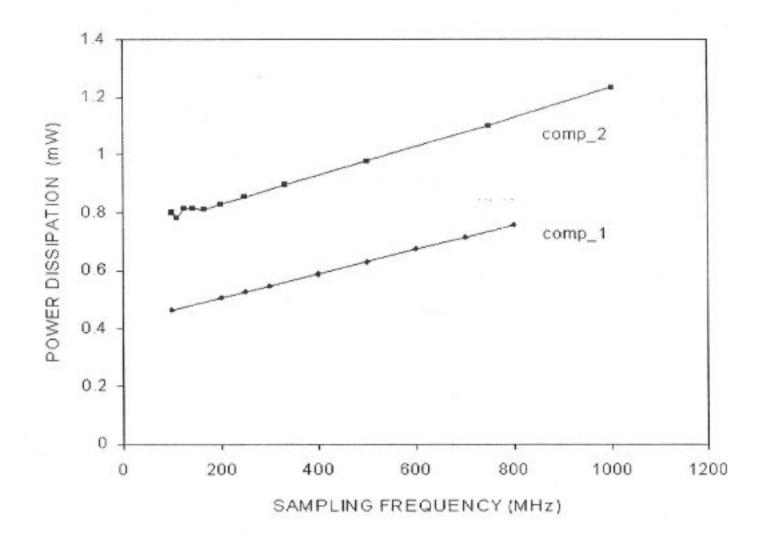

| 4.38 | Power consumption for different input voltage differences                           |

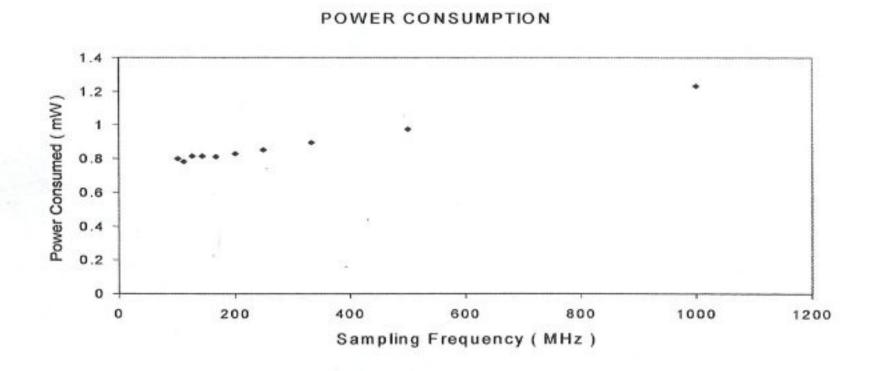

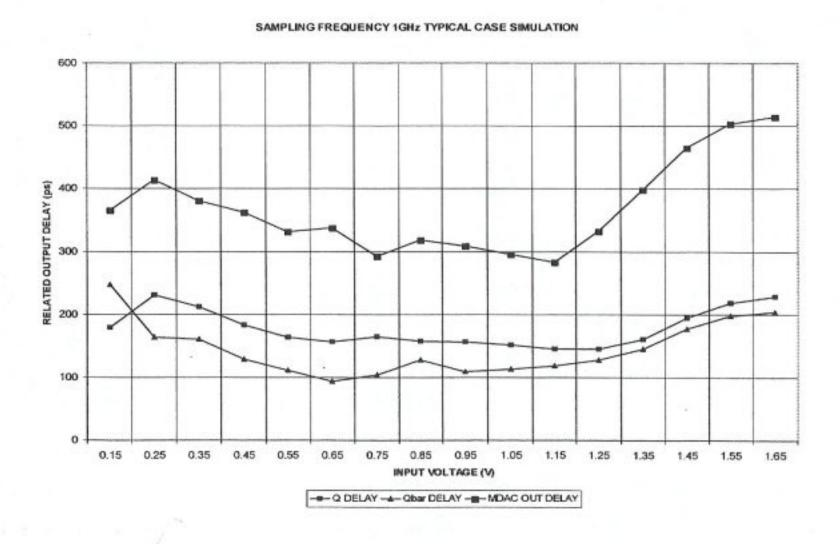

| 4.39 | Power consumption for different sampling frequencies 82                             |

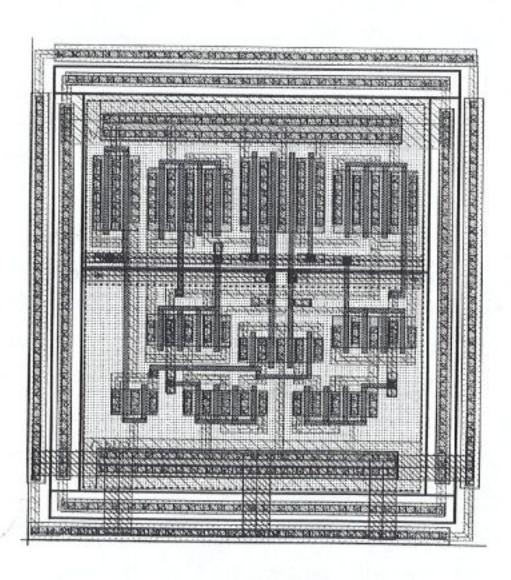

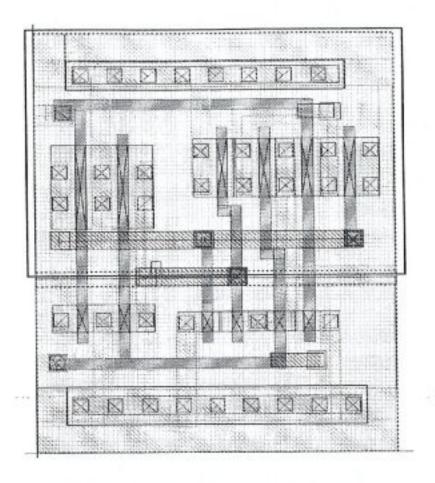

| 4.40 | Layout of the improved complementary-in voltage comparator 83                       |

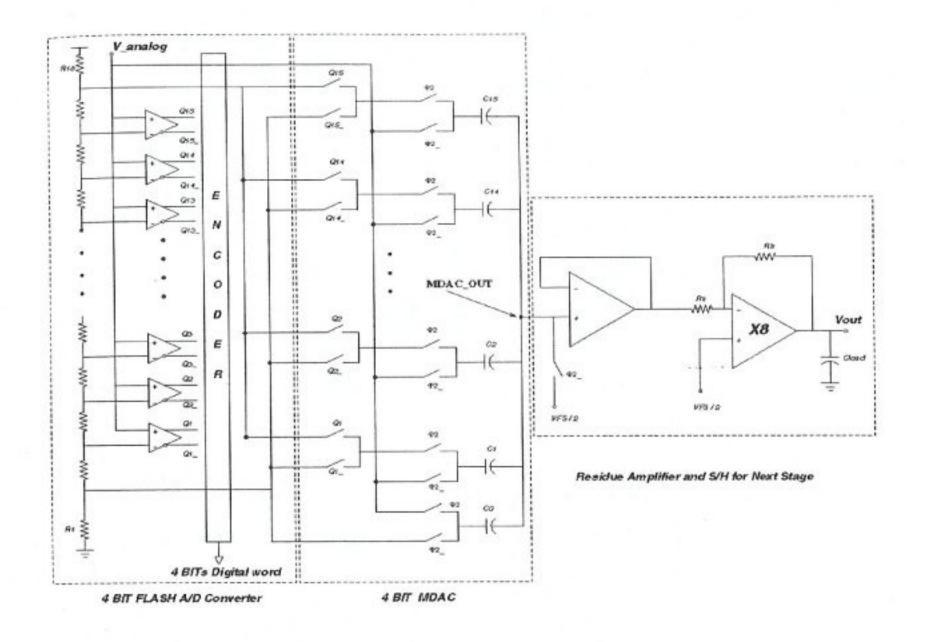

| 4.41 | Four bits ADC/MDAC schematic used in improved full complementary                    |

|      | voltage comparator verification 84                                                  |

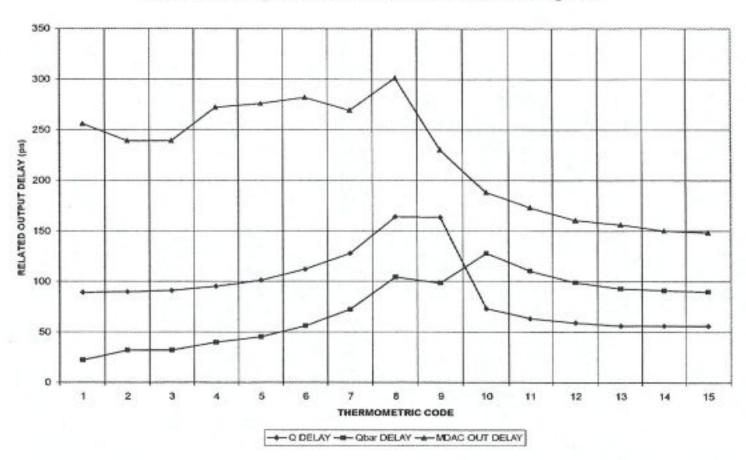

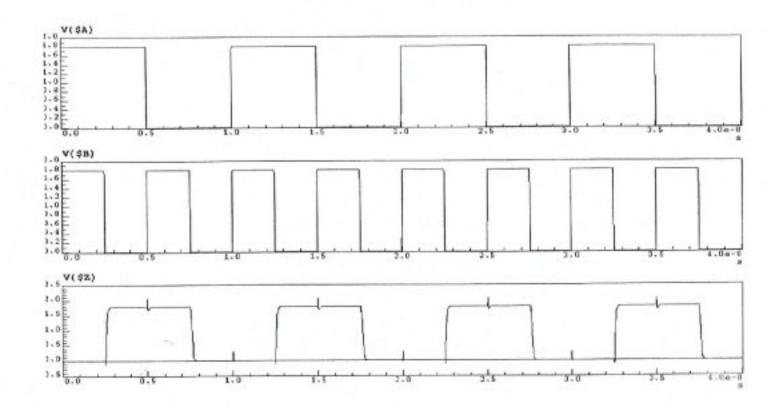

| 4.42 | Response times for Q, $\overline{Q}$ and MDAC output voltage in ideal conditions 85 |

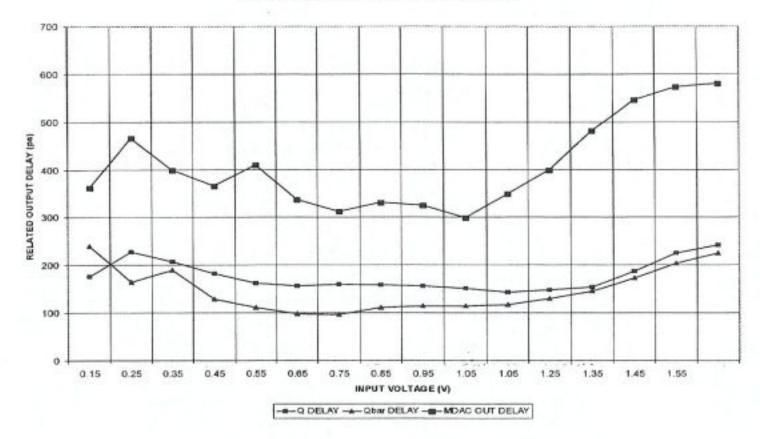

| 4.43 | Response times obtained for input voltage at LSB level, typical corner              |

|      | and nMOS input stage transistor with mismatch                                       |

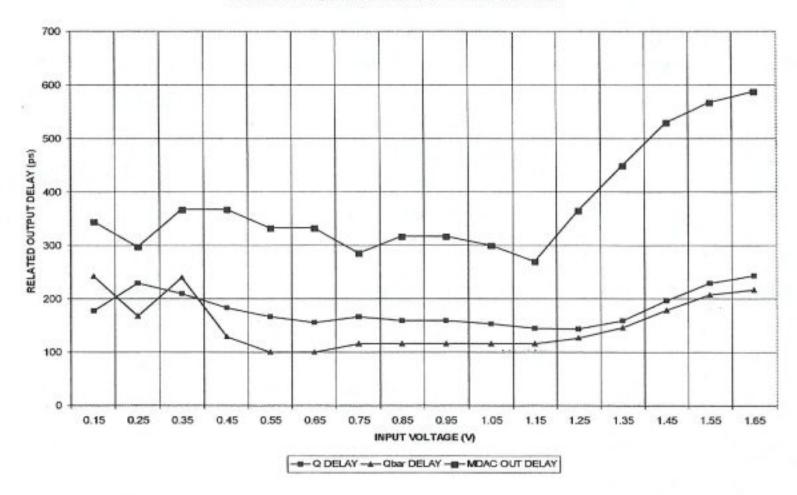

| 4.44 | Response times obtained for input voltage at LSB level, typical corner              |

|      | and pMOS input stage transistor with mismatch 86                                    |

| 4.45 | Response times obtained for input voltage at Vfull_scale/2 level, typical           |

|      | corner and nMOS input stage transistor with mismatch 86                             |

| 4.46 | Response times obtained for input voltage at V <sub>full_scale</sub> level, typical |

|      | corner and pMOS input stage transistor with mismatch 87                             |

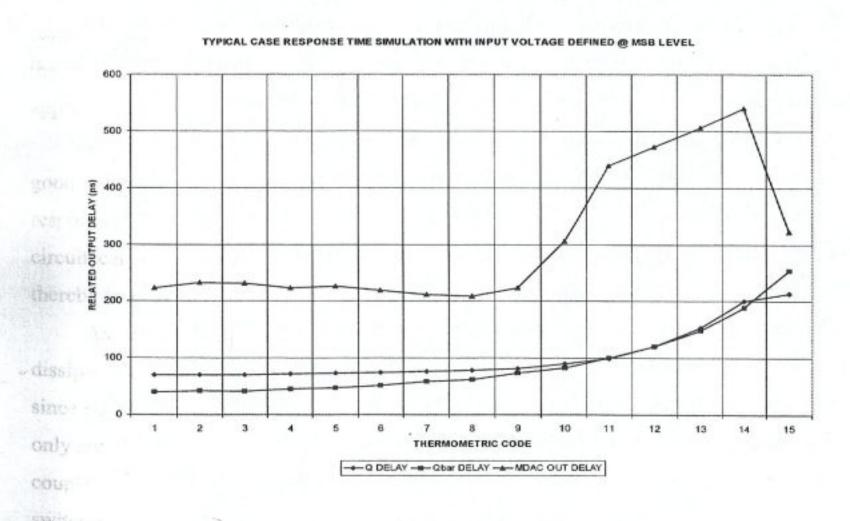

| 4.47 | Response times obtained for input voltage at MSB level, typical corner              |

|      | and nMOS input stage transistor with mismatch 87                                    |

| 4.48 | Response times obtained for, typical corner simulations for 500 MHz                 |

|      | clock frequency                                                                     |

| 4.49 | Response times obtained for typical corner simulations for 750 MHz                  |

|      | clock frequency                                                                     |

| 4.50 | Response times obtained for typical corner simulations for 1 GHz clock              |

|      | frequency                                                                           |

| 4.51 | Worst-case response time v.s input voltage in a simulated 4-bit ADC 90              |

| 4.52 | Avarage power dissipation of the comparator circuits vs. sampling                   |

|      | frequency91                                                                         |

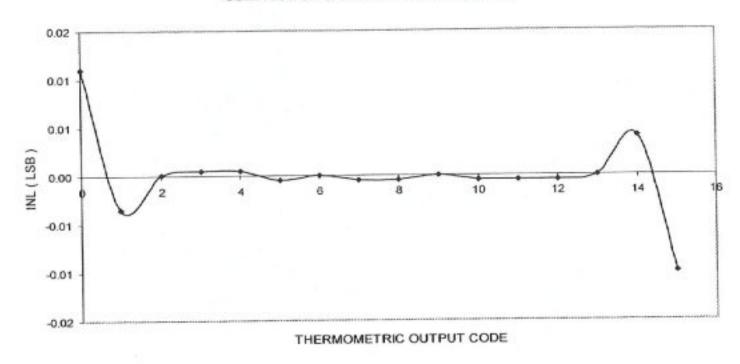

| 4.53 | Integral non-linearity obtained with improved full complementary                    |

|      | comparator for typical simulation corner92                                          |

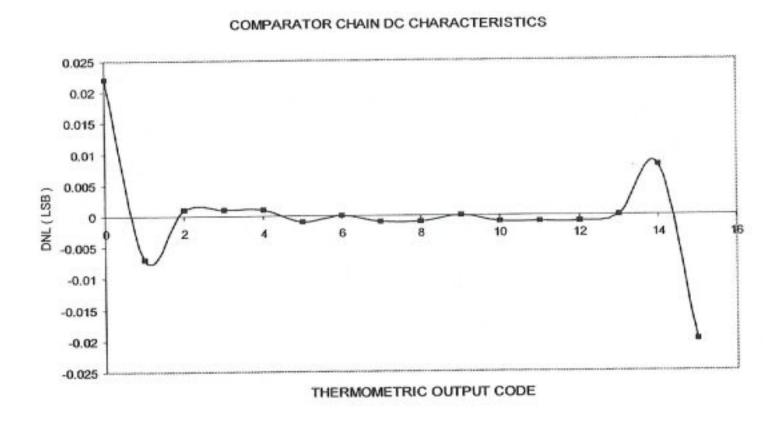

| 4.54 | Differential non-linearity obtained with improved full complementary                |

|      | comparator for typical simulation corner92                                          |

| 4.55 | Comparator circuit with latched output stage during reset mode              |

|------|-----------------------------------------------------------------------------|

|      | (Low power comparator version)93                                            |

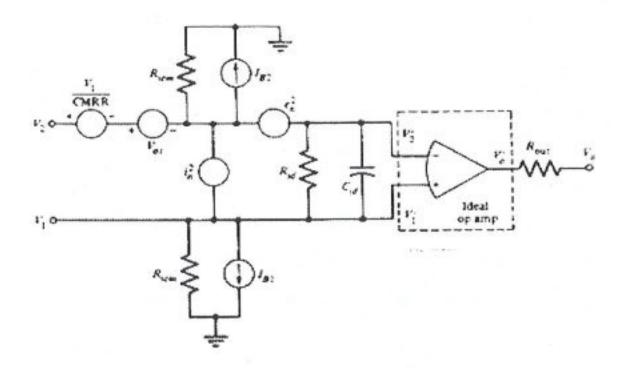

| 5.1  |                                                                             |

|      | illustrating some possible errors96                                         |

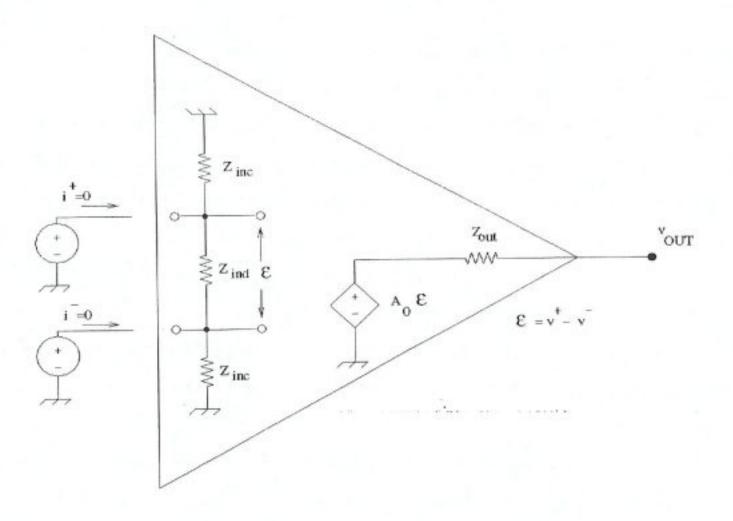

| 5.2  | Behavioral model for ideal differential input, single-ended output          |

|      | op-amp                                                                      |

| 5.3  | A model for an ideal op-amp showing some of the nonideal                    |

|      | characteristics99                                                           |

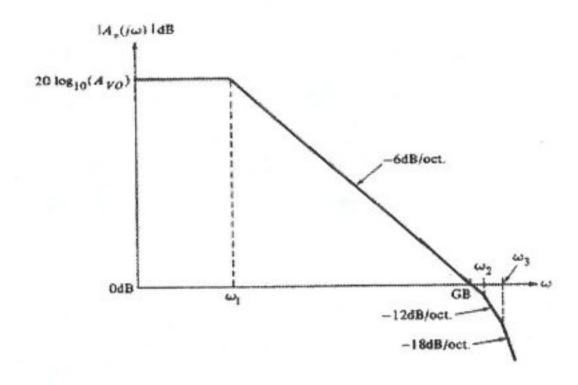

| 5.4  | Typical frequency response for an op-amp 100                                |

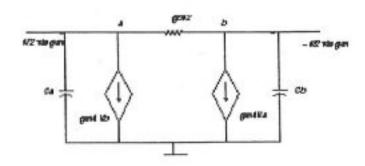

| 5.5  | The differential OTA symbol and ideal model 103                             |

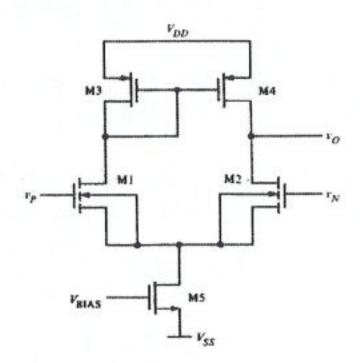

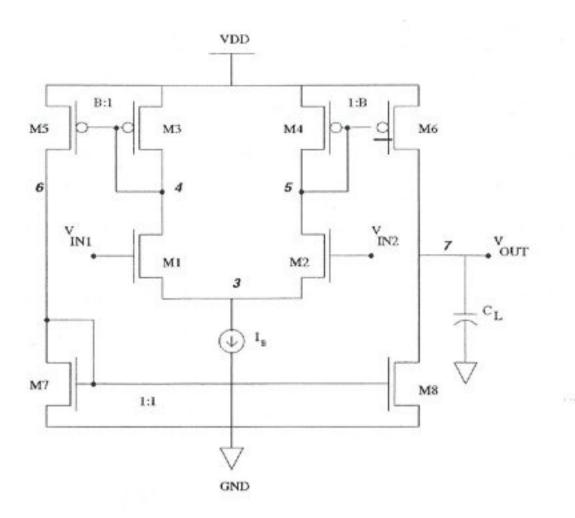

| 5.6  | Symmetrical CMOS OTA schematic                                              |

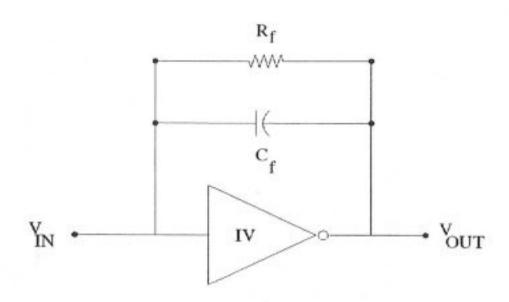

| 5.7  | Inverter-based output stage schematic 108                                   |

| 5.8  | Simplified small signal equivalent of the inverter 109                      |

| 5.9  | Equivalent circuit of Figure 5.8                                            |

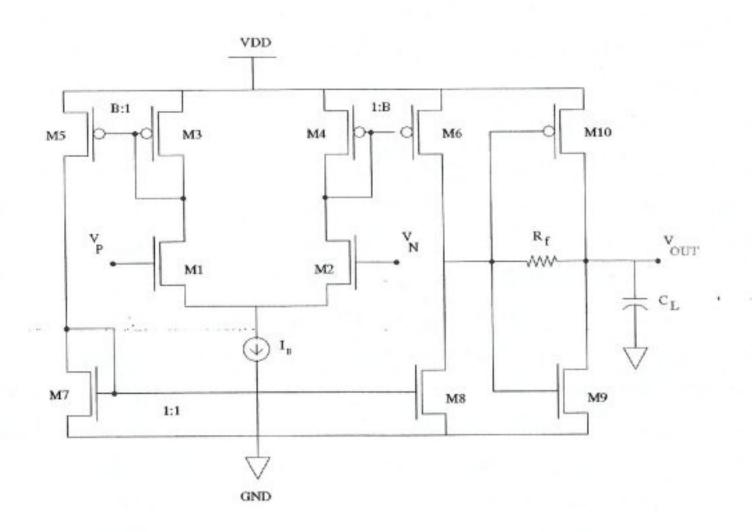

| 5.10 | High open loop-gain OTA based op-amp schematic                              |

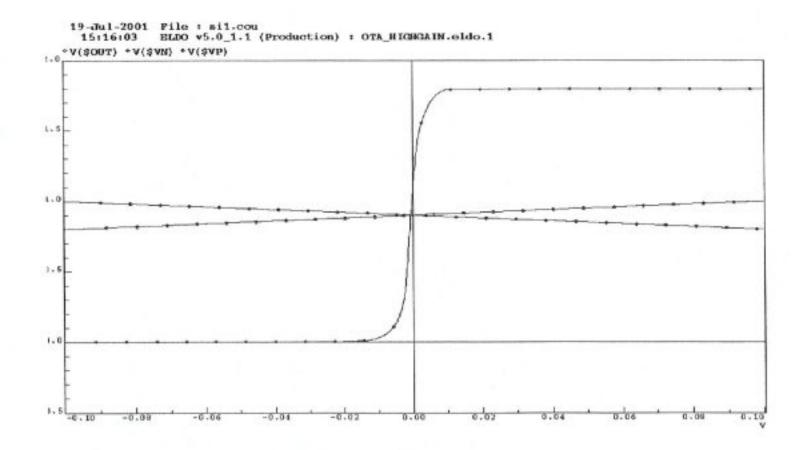

| 5.11 | DC characteristics of high open loop-gain OTA based op-amp 113              |

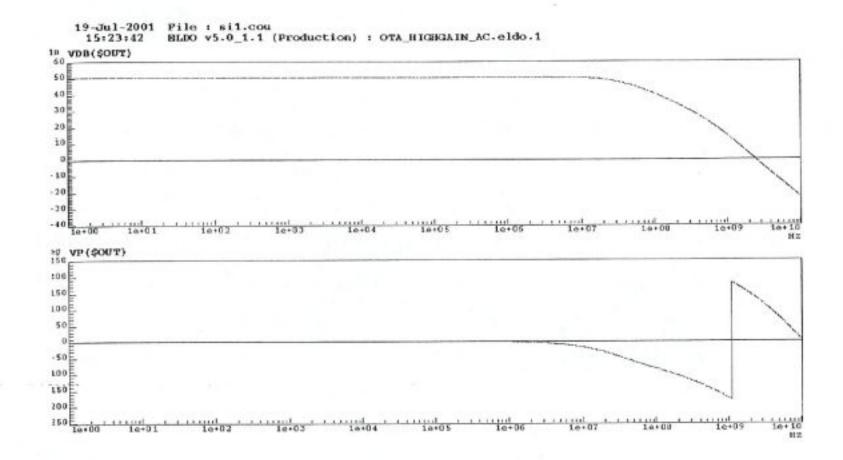

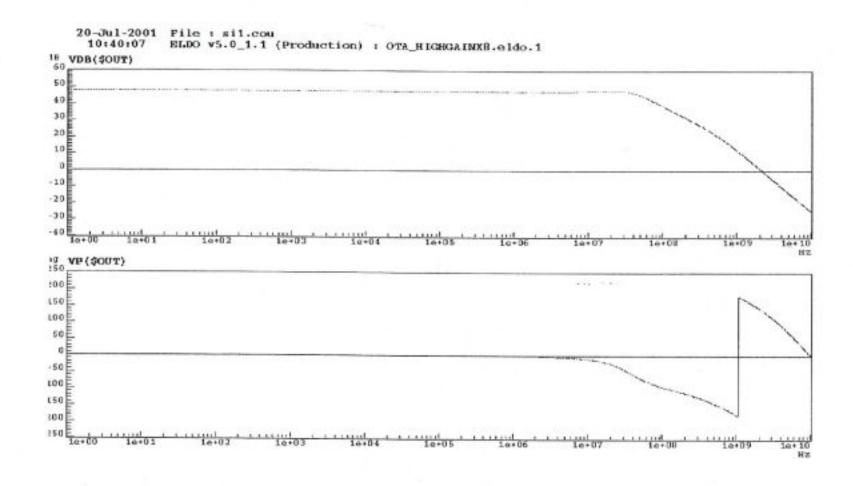

| 5.12 | Open loop AC characteristics of high open loop-gain OTA based               |

|      | op-amp                                                                      |

| 5.13 | Closed loop AC characteristics of high open loop-gain OTA based             |

|      | op-amp                                                                      |

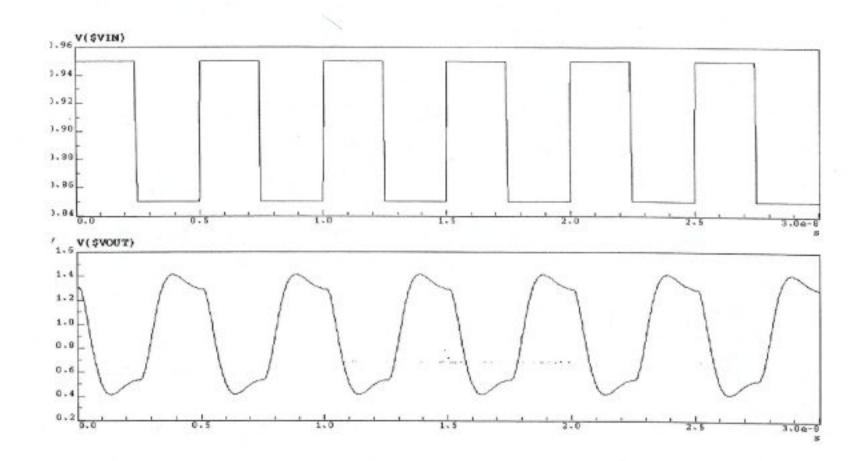

| 5.14 | Transient characteristics of high open loop-gain OTA used in X16 feedback   |

|      | gain for residue amplifier for a 200 MHz 100 mV <sub>pp</sub> input pulse   |

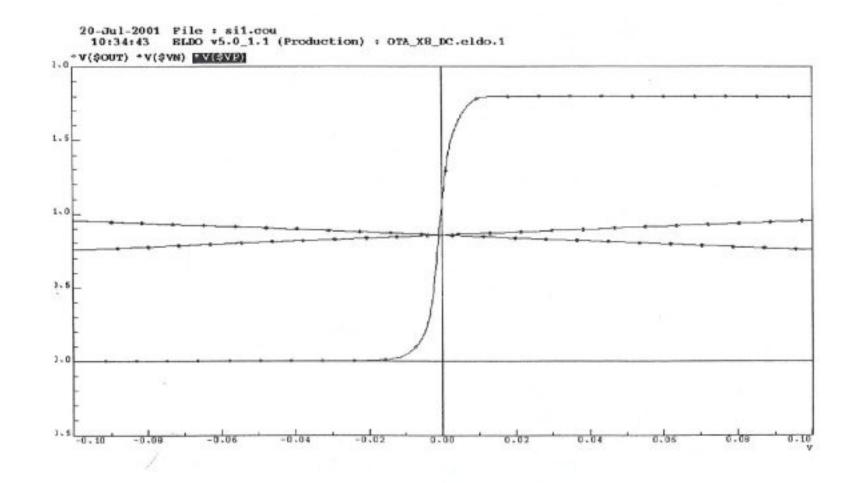

| 5.15 | DC characteristics of X8 OTA based op-amp                                   |

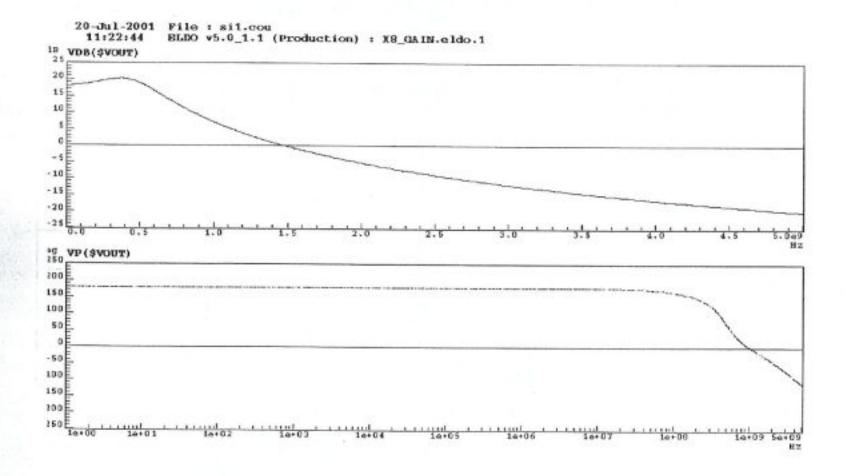

| 5.16 | Open loop AC characteristics of X8 OTA based op-amp                         |

| 5.17 | Closed loop AC characteristics of X8 OTA based op-amp                       |

| 5.18 | Transient response of X8 OTA based op-amp to a 200 MHz 100 mV <sub>pp</sub> |

|      | input pulse                                                                 |

| 5.19 | Schematic view of low open loop-gain OTA                                    |

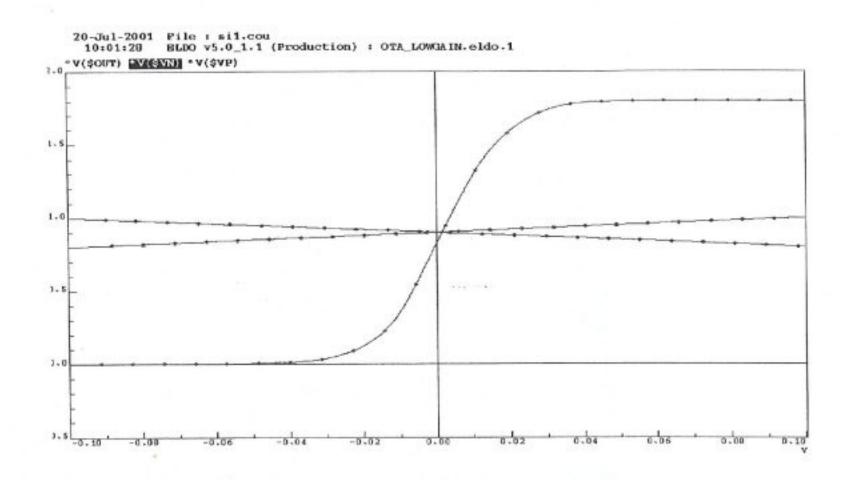

| 5.20 | Dc characteristics of low open loop-gain OTA based op-amp                   |

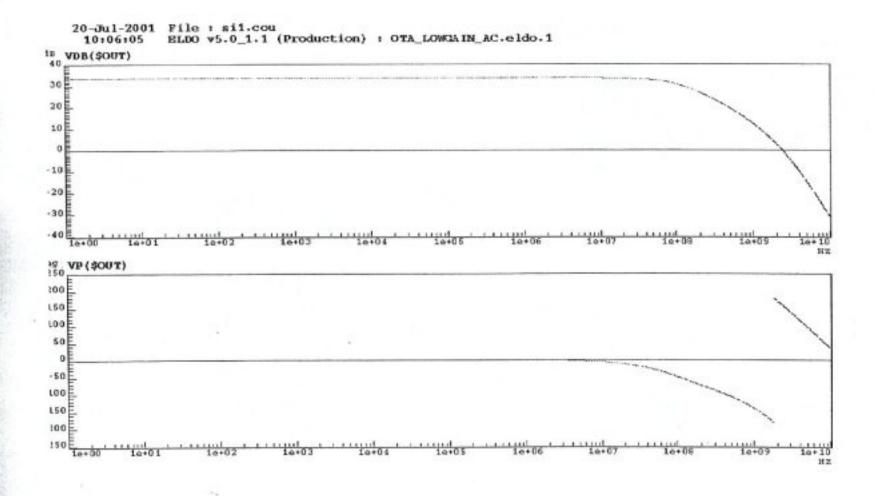

| 5.21 | Open loop AC characteristics of low open loop-gain OTA based                |

|      | op-amp                                                                      |

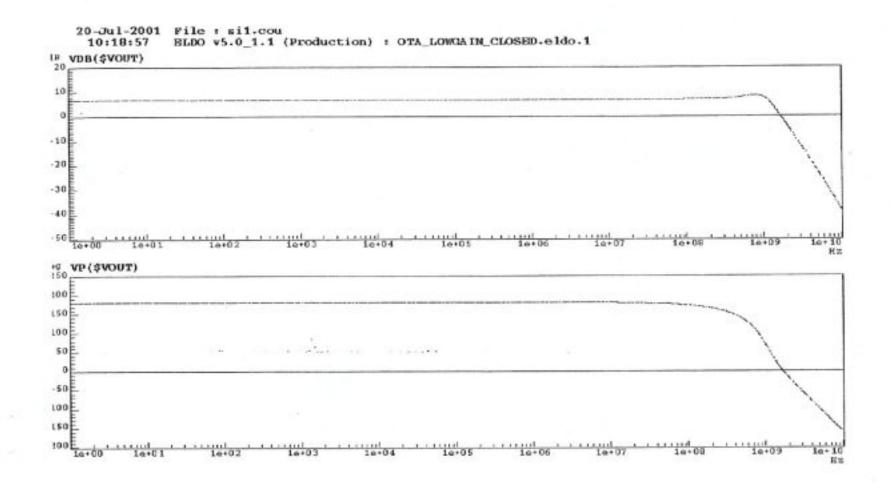

| 5.22 | Closed loop AC characteristics of low open loop gain OTA based              |

|      | op-amp                                                                      |

|      | 124                                                                         |

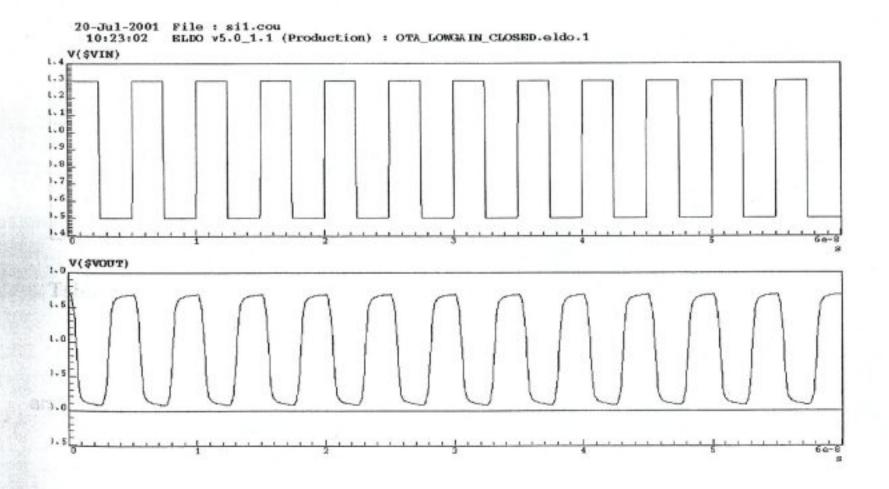

| 5.23 | Transient response of X2 feedback configuration to a 200 MHz               |

|------|----------------------------------------------------------------------------|

|      | 800 mV <sub>pp</sub> input pulse signal                                    |

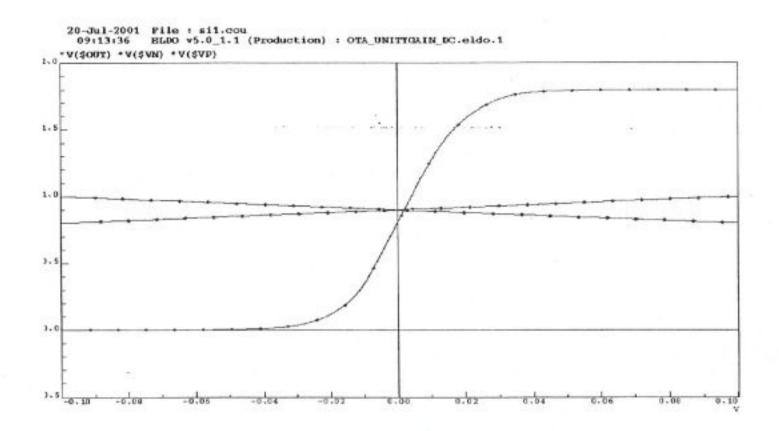

| 5.24 | DC characteristics of unity gain stable OTA based op-amp                   |

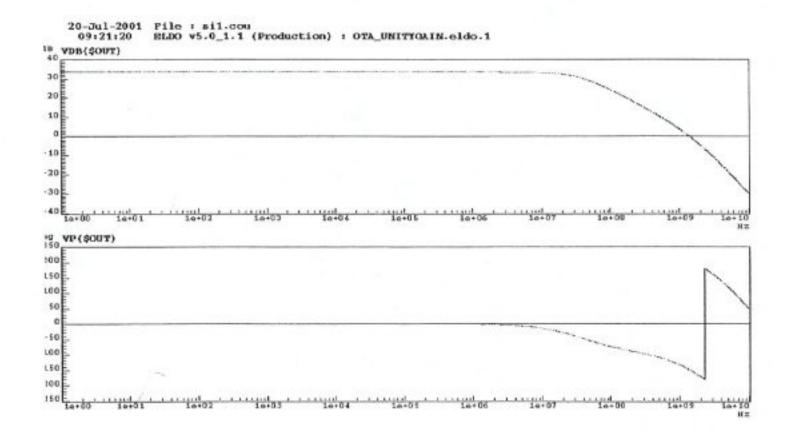

| 5.25 | Open loop AC characteristics of unity gain stable OTA based op-amp 127     |

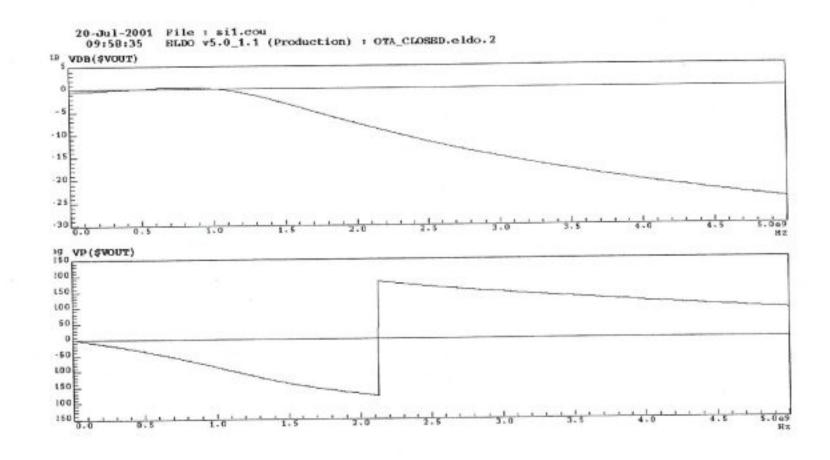

| 5.26 | Closed loop AC characteristics of unity gain stable OTA based op-amp 128   |

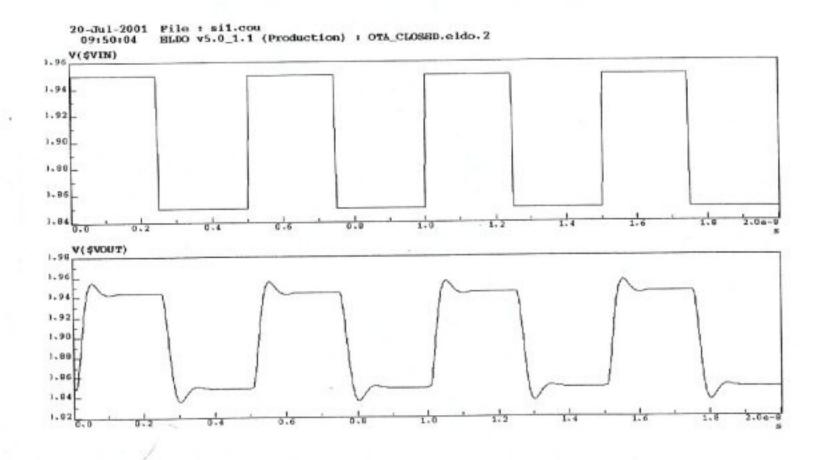

| 5.27 | Transient response of unity gain stable OTA based op-amp to a 200 MHz      |

|      | 10 mV <sub>pp</sub> input pulse signal                                     |

| 5.28 | Block representation of sample-and-hold circuit                            |

| 5.29 | Block representation of residue amplifier                                  |

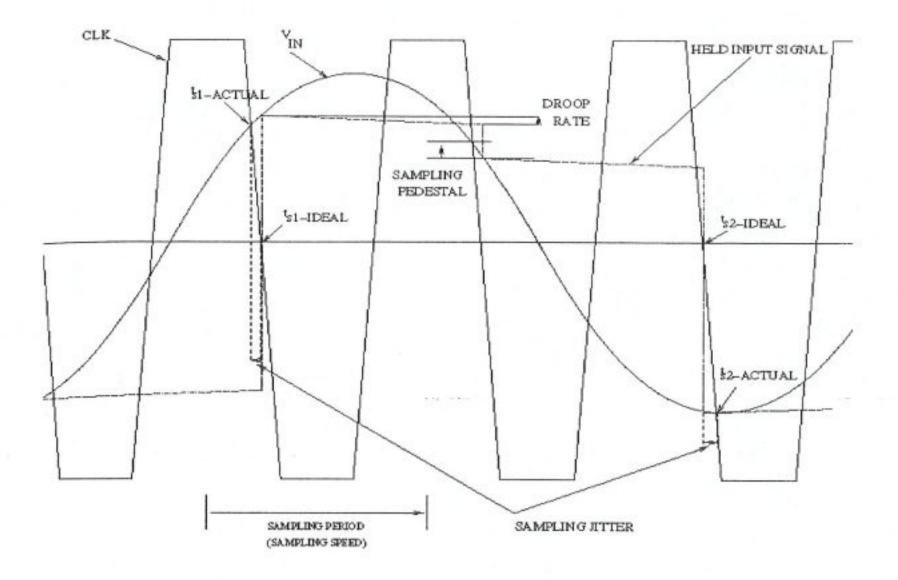

| 5.30 | Sampled voltage versus sampling pedestal, where input signal frequency     |

|      | is 50 kHz and sampling clock frequency is 200 MHz131                       |

| 5.31 | Sampled voltage versus held voltage, where input signal frequency is       |

|      | 50 kHz and sampling clock frequency is 200 MHz131                          |

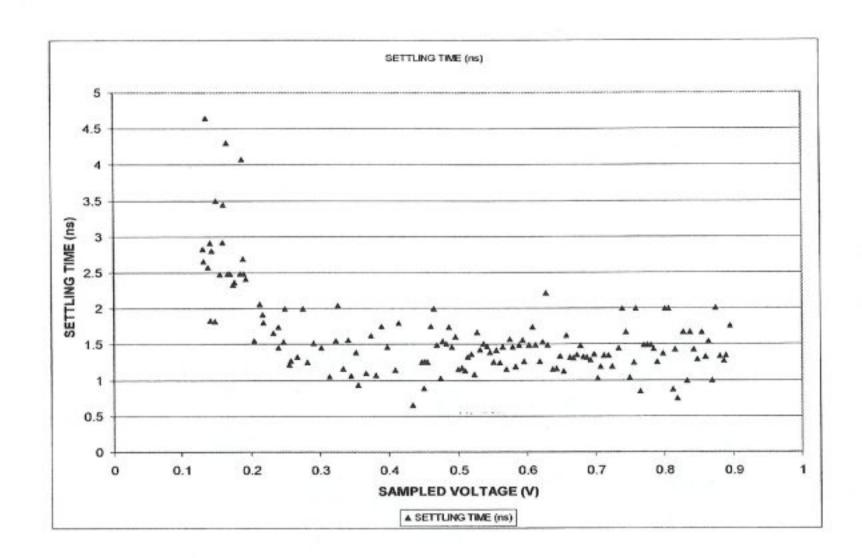

| 5.32 | Sampled voltage versus settling time, input signal frequency is 50 kHz     |

|      | and sampling clock frequency is 200 MHz                                    |

| 5.33 | Sampled voltage versus sampling pedestal, where input signal frequency     |

|      | is 30 MHz and sampling clock frequency is 200 MHz                          |

| 5.34 | Sampled voltage versus held voltage, where input signal frequency is       |

|      | 30 MHz and sampling clock frequency is 200 MHz                             |

| 5.35 | Sampled voltage versus settling time, input signal frequency is 30 MHz     |

|      | and sampling clock frequency is 200 MHz                                    |

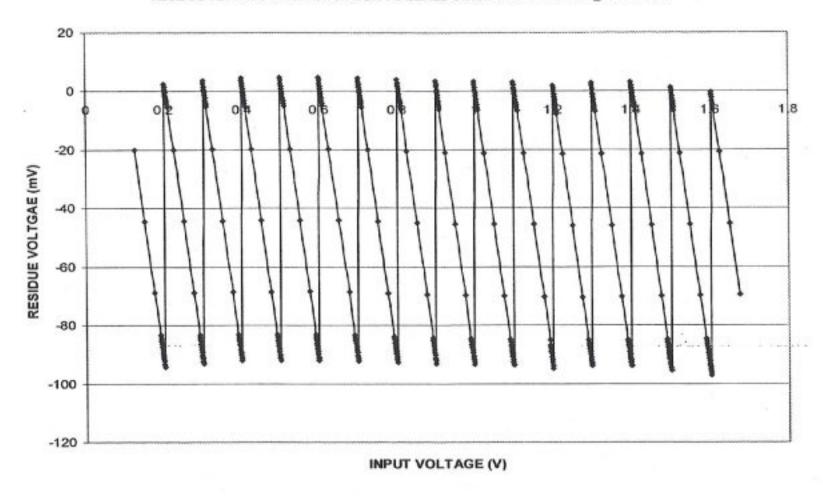

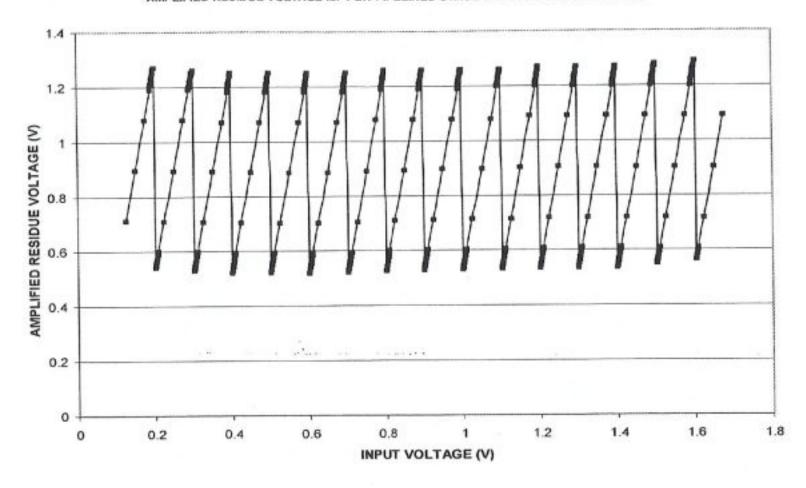

| 5.36 | Residue voltage obtained versus input voltage for typical simulation       |

|      | corner                                                                     |

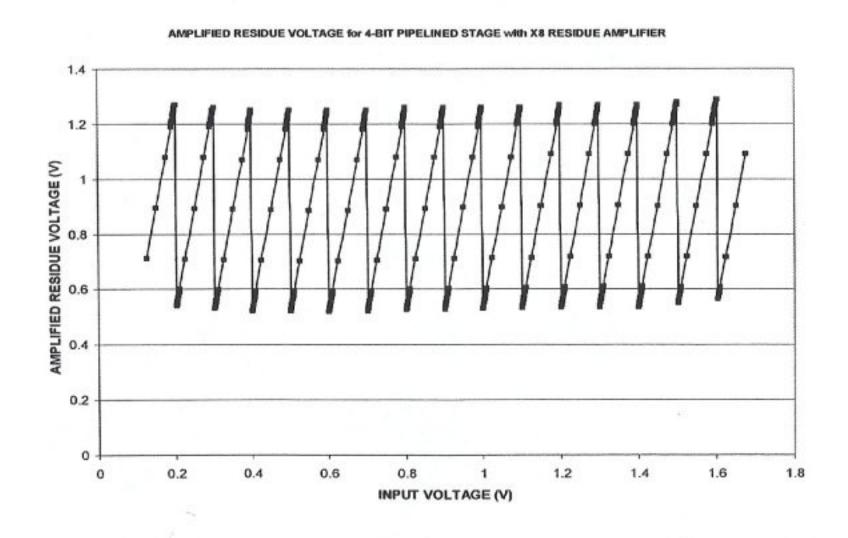

| 5.37 | Amplified residue voltage by X8 amplification factor                       |

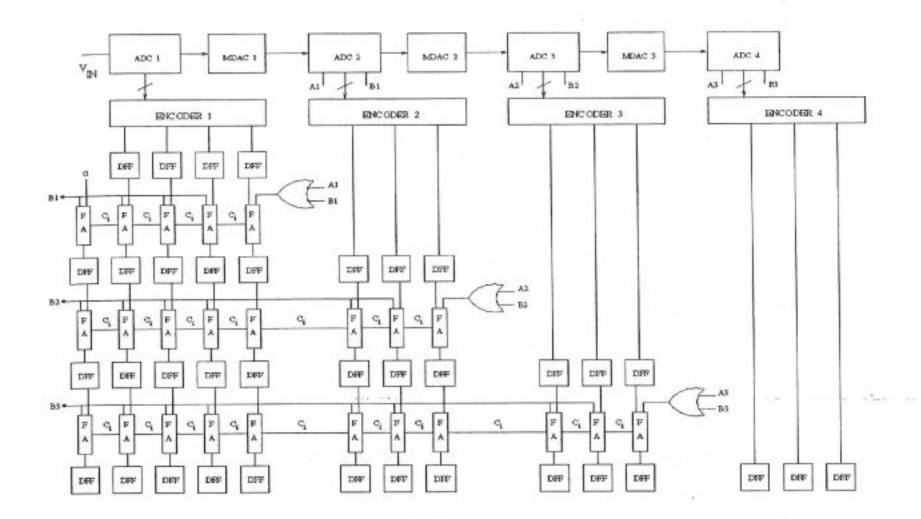

| 6.1  | Four stage pipelined A/D converter schematic. Ai and Bi bits are overflow  |

|      | and underflow bits respectively. They will be explained in detail later in |

|      | this chapter                                                               |

| 6.2  | Simplified schematic of one stage of a 4-bit pipeline ADC                  |

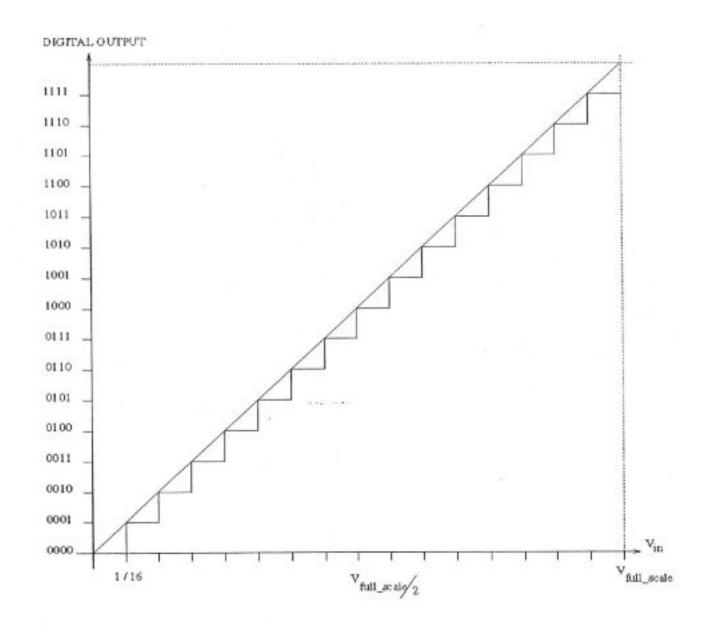

| 6.3  | DC input-output characteristics of a 4-bit piepline A/D converter          |

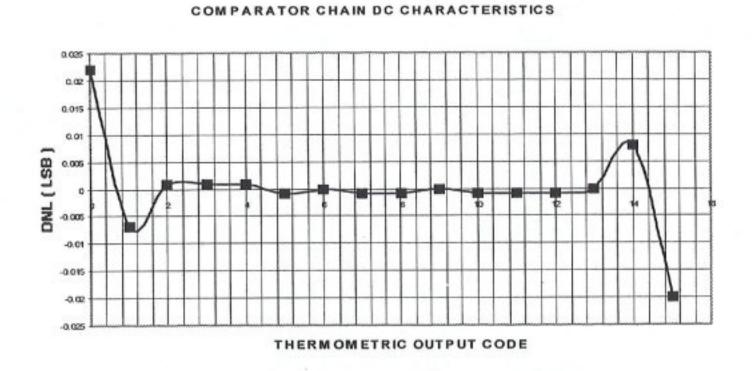

| 6.4  | Typical corner DNL plot for the 4-bit A/D converter                        |

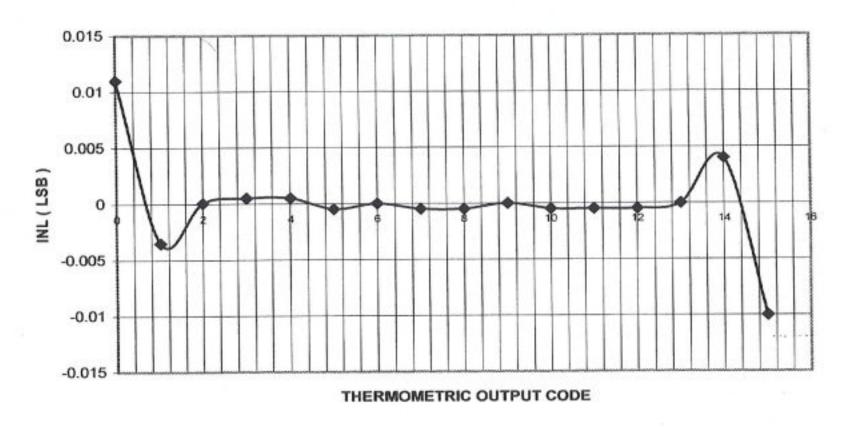

| 6.5  | Typical corner INL plot for the 4-bit A/D converter                        |

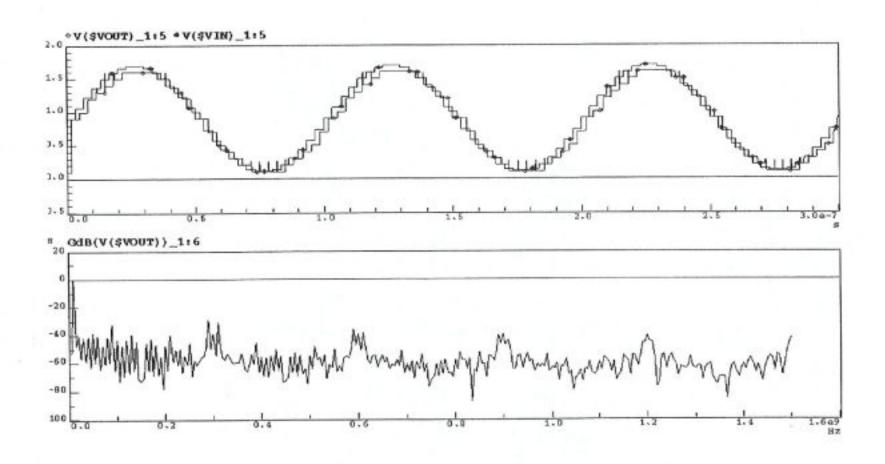

| 6.6  | Typical FFT plot obtained for a 4-bit A/D converter when the input signal  |

|      | frequency is 10 MHz and the sampling clock frequency is 300 MHz 140        |

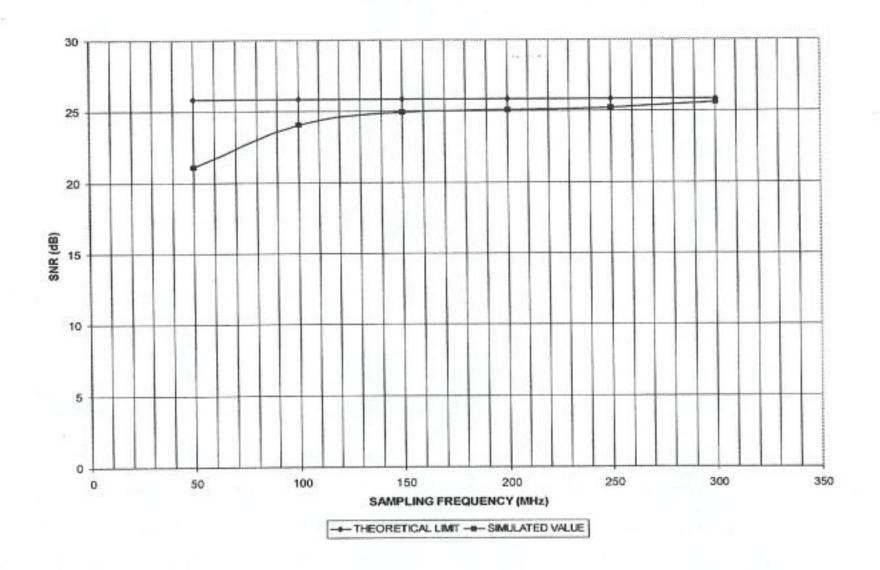

| 6.7  | SNR of the 4-bit ADC as a function of sampling frequency, with input signal       |

|------|-----------------------------------------------------------------------------------|

|      | frequency of 10 MHz and the sampling clock frequency is varied from               |

|      | 50 MHz to 300 MHz                                                                 |

| 6.8  | SNR of the 4-bit ADC as a function of sampling frequency, with input              |

|      | signal frequency of 10 MHz and the sampling clock frequency is varied             |

|      | from 500 MHz to 1.2 GHz                                                           |

| 6.9  | Overall variation of SNR as a function of the sampling ferquency, with input      |

|      | signal frequency of 10 MHz                                                        |

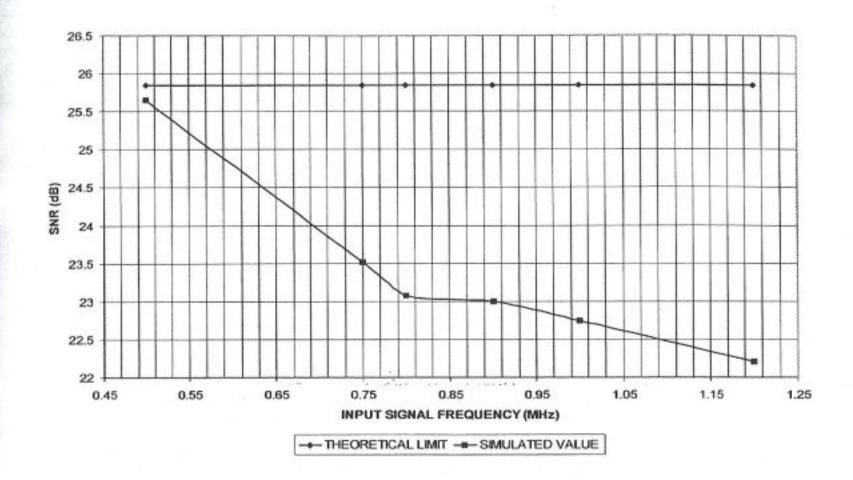

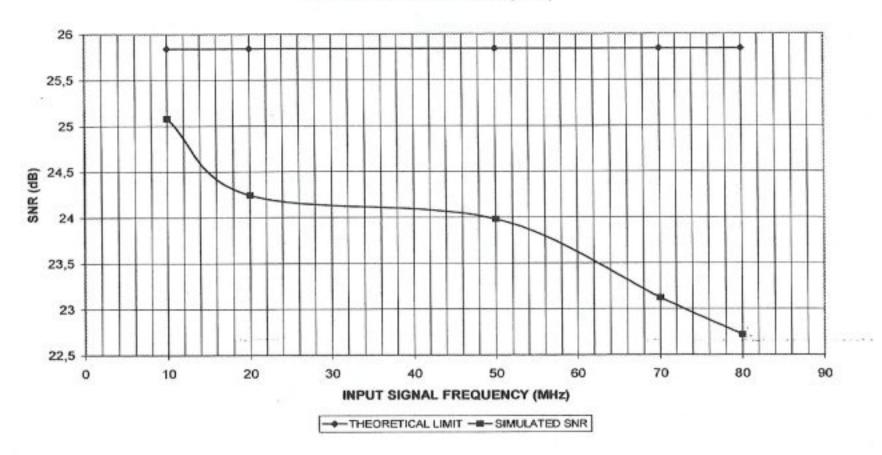

| 6.10 | SNT of the 4-bit ADC as a function of input signal frequency, with                |

|      | sampling clock frequency of 200 MHz and the input signal frequency is             |

|      | varied from 10 MHz to 80 MHz                                                      |

| 6.11 | Ideal input-output characteristics for a three bit D/A converter                  |

| 6.12 | Implementation of a 3-bit voltage scaling D/A converter                           |

| 6.13 | N-bit charge-scaling D/A converter schematic                                      |

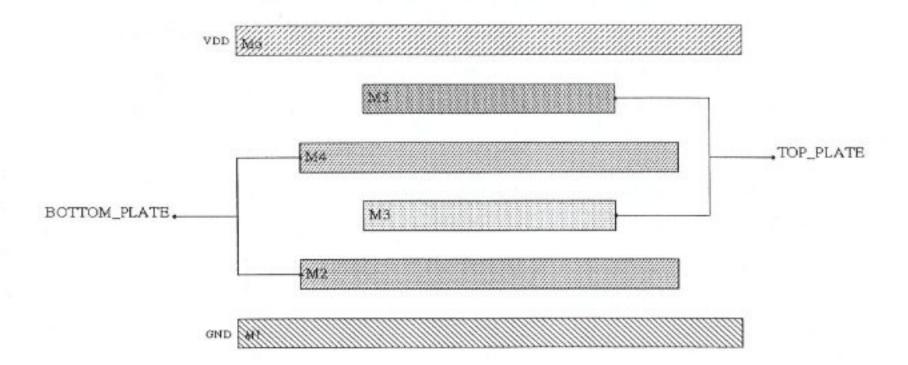

| 6.14 | Schematic view of a 4-bit MDAC                                                    |

| 6.15 | Simplified cross-section representation of metal-metal capacitors constructed     |

|      | in N-well. Note that N-well is not shown in figure for simplicity                 |

| 6.16 | Residue voltages obtained for different input voltage levels applied to the       |

|      | input of the 4-bit pipeline stage. The sampling clock frequency                   |

|      | is 200 MHz                                                                        |

| 6.17 | Time-dependent variation of the amplified residue voltage, with a sampling        |

|      | clock frequency of 200 MHz                                                        |

| 6.18 | Residue voltage obtained versus input voltage for typical simulation              |

|      | corner at 200 MHz sampling rate                                                   |

| 6.19 | Variation of the amplified residue voltage given Figure 6.19 as a function of the |

|      | input voltage level, with X8 amplification factor                                 |

| 6.20 | Residue voltage obtained for different input voltage levels applied to the        |

|      | input of the 4-bit pipeline stage. The sampling clock frequency                   |

|      | is 50 MHz                                                                         |

| 6.21 | Time-dependent variation of the amplified residue voltage, with a sampling        |

|      | clock frequency of 50 MHz                                                         |

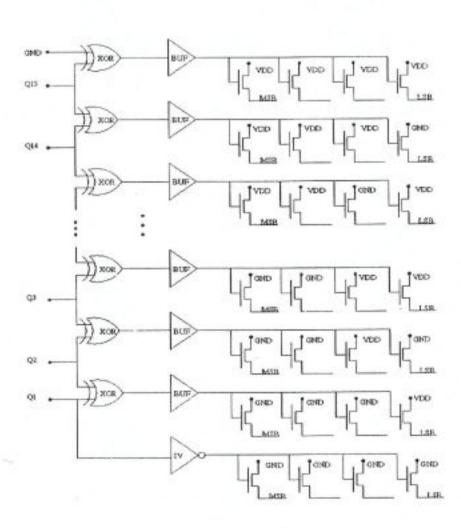

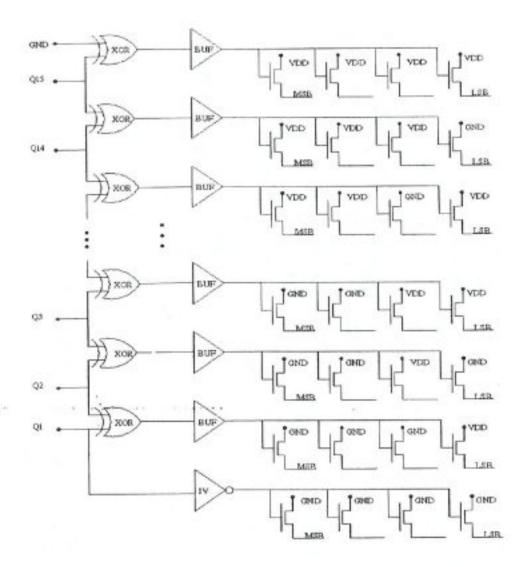

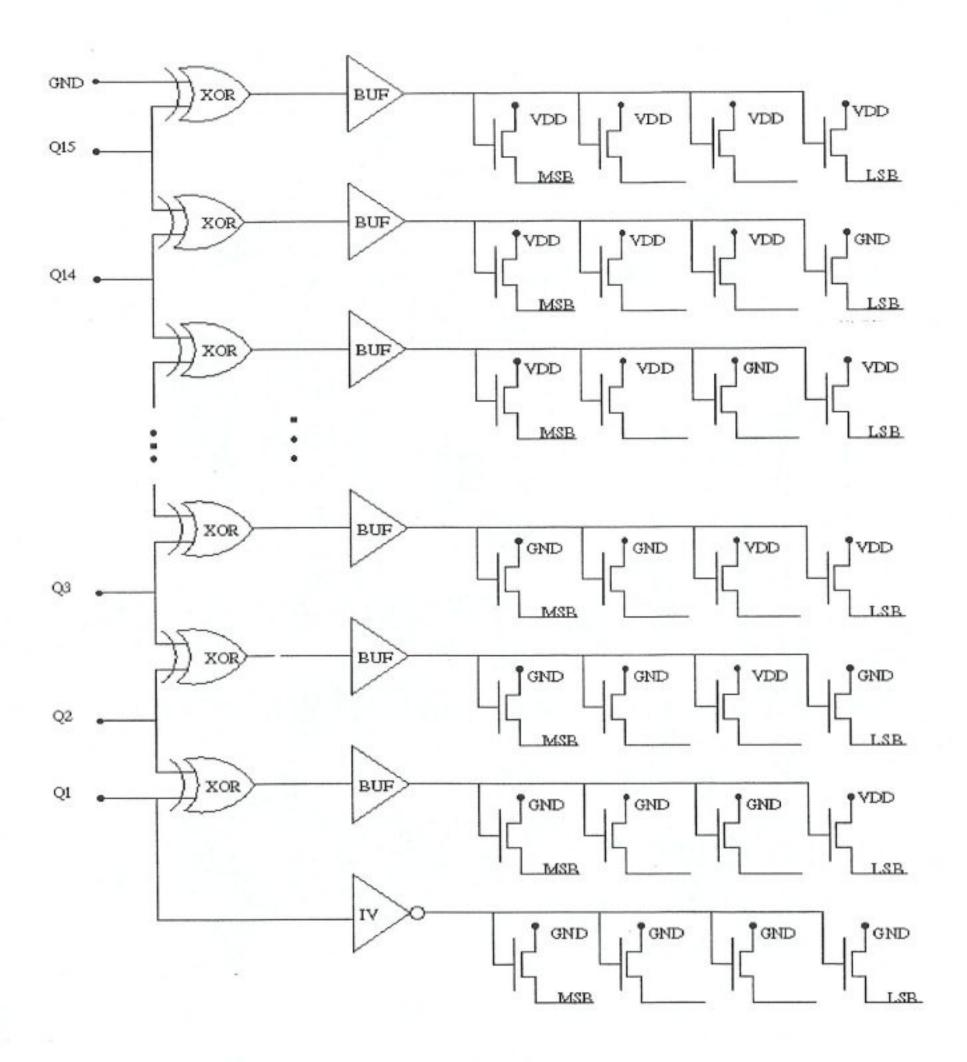

| 6.22 | Simplified schematic view of a 4-bit encoder block used in stage 1                |

| 6.23 | 1-Bit-overlapping technique that is used in the design of the pipeline            |

|      | stages                                                                            |

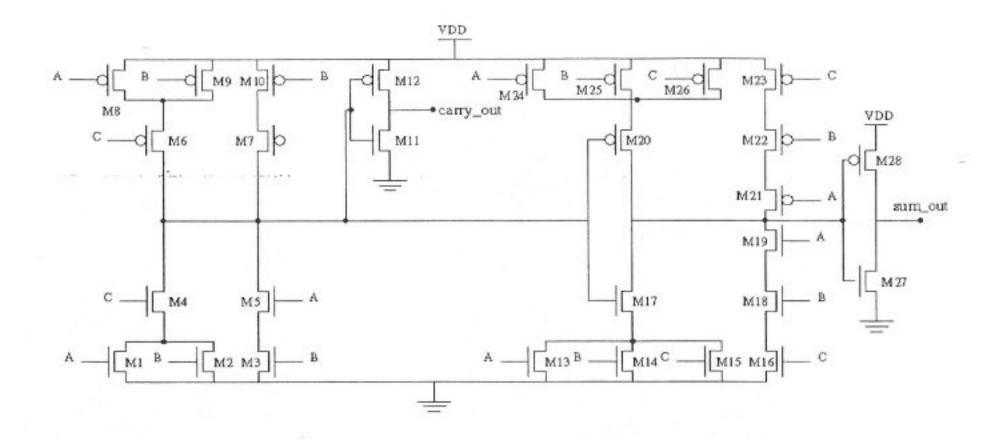

| 7.1  | Gate level schematic of the one-bit full-adder circuit                            |

|------|-----------------------------------------------------------------------------------|

| 7.2  | Completely symmetric 1-bit full adder cell                                        |

| 7.3  | Simulated input and output waveforms of 1-bit full adder circuit                  |

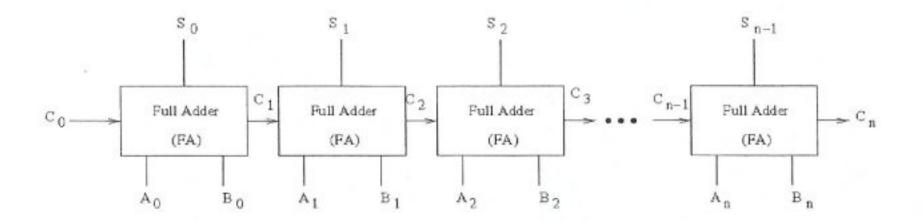

| 7.4  | Block diagram of a carry ripple adder chain consisting of n 1-bit                 |

|      | full adders                                                                       |

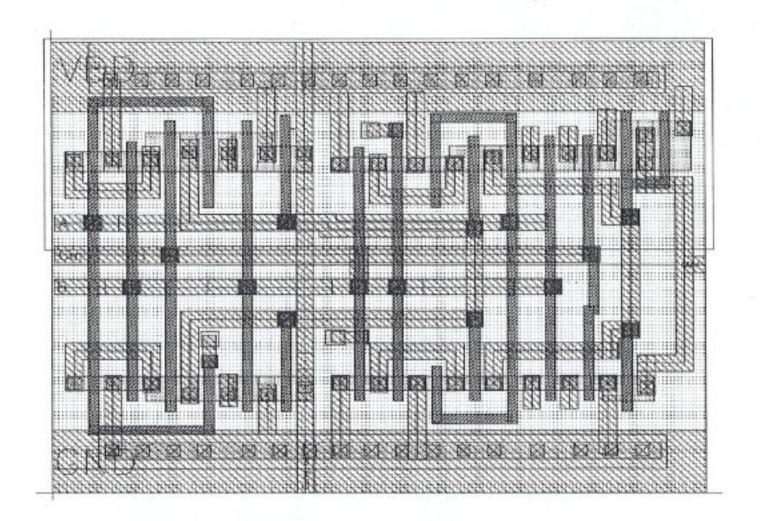

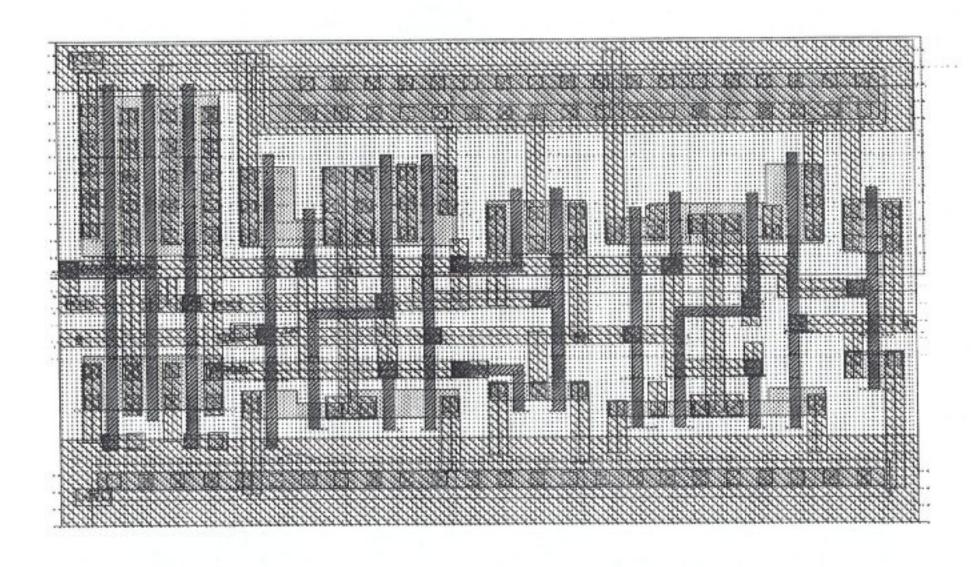

| 7.5  | Layout view of the designed 1-bit full adder circuit                              |

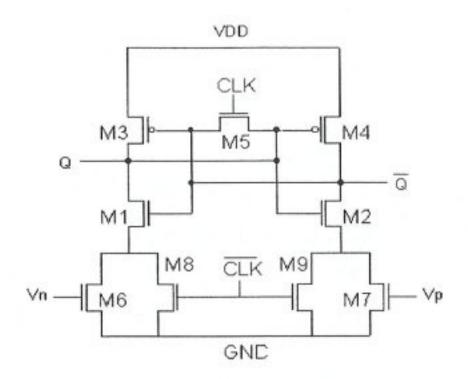

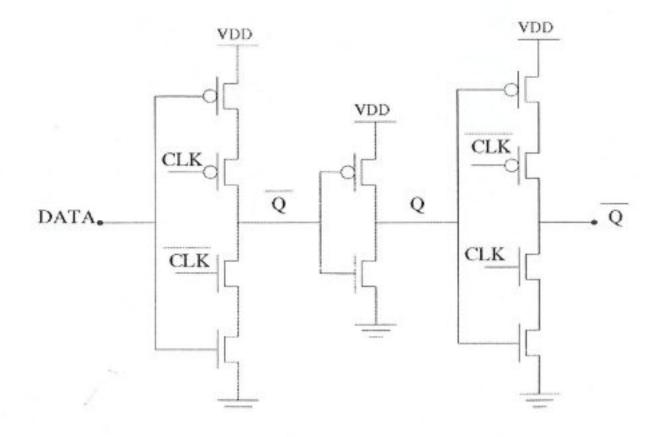

| 7.6  | CMOS implementation of the D-latch circuit                                        |

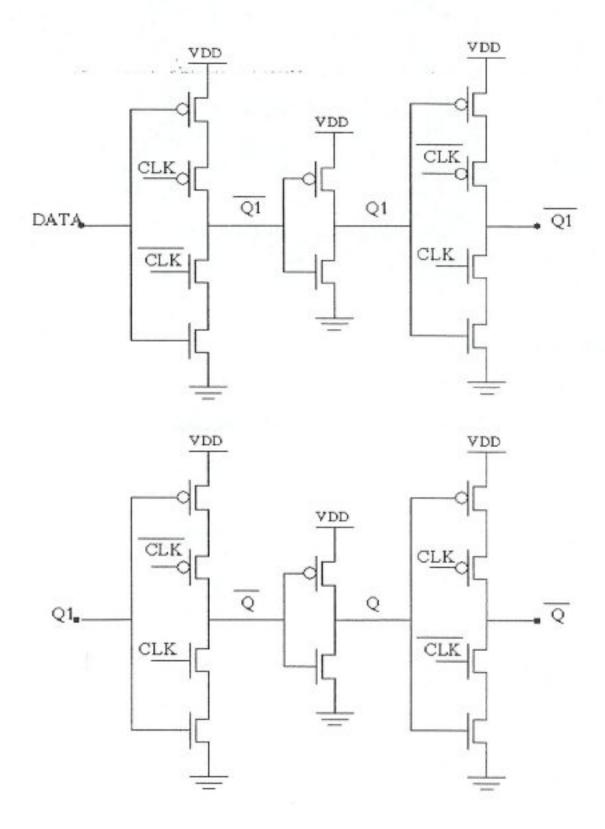

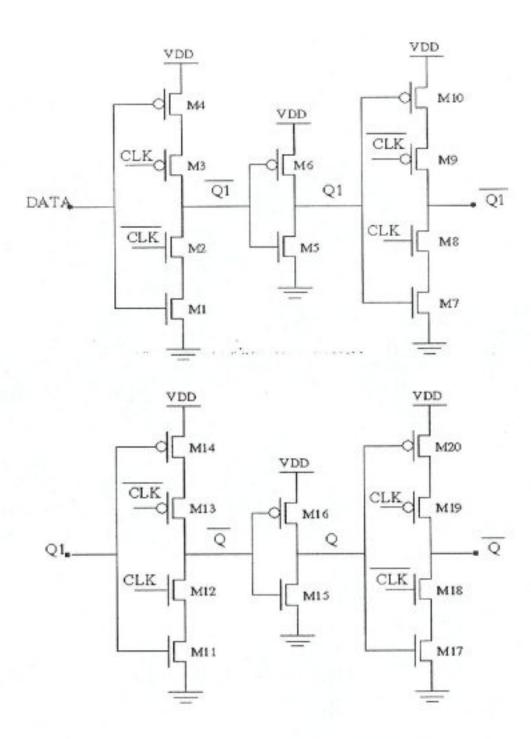

| 7.7  | CMOS rising edge-triggered master-slave D flip-flop                               |

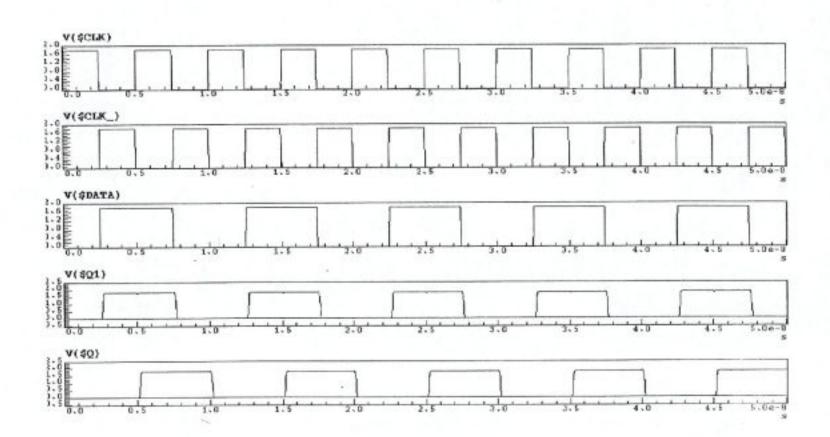

| 7.8  | Simulated input and output waveforms of the CMOS DFF circuit given                |

|      | in Figure 7.7                                                                     |

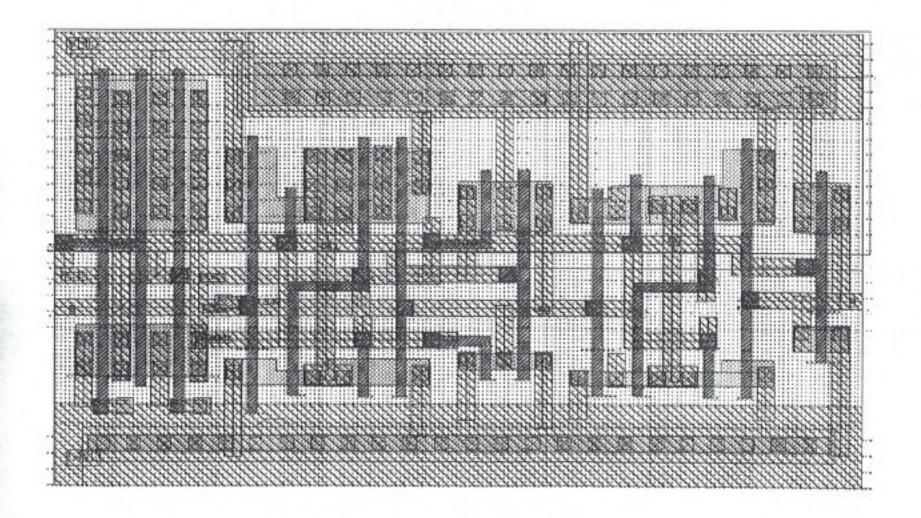

| 7.9  | Layout view of designed D-type flip-flop. Area is aproximately                    |

|      | 132 μm <sup>2</sup> 172                                                           |

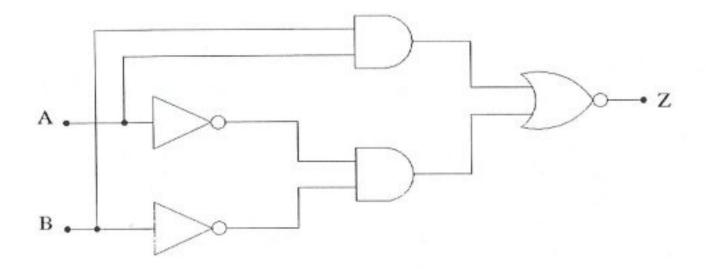

| 7.10 | Gate level representation of XOR function                                         |

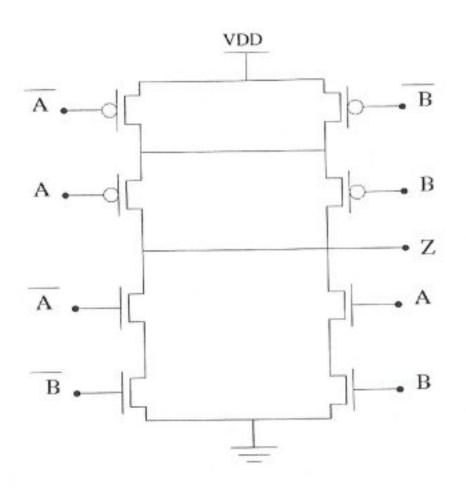

| 7.11 | Full CMOS implementation of XOR function174                                       |

| 7.12 | Layout view of the designed XOR gate. Area is aproximately 45 μm <sup>2</sup> 175 |

| 7.13 | Simulated input and output waveforms of the designed XOR circuit 175              |

| 7.14 | Simplified schematic view of a 4-bit encoder block                                |

| 8.1  | Block level representation of four-stage pipelined A/D converter                  |

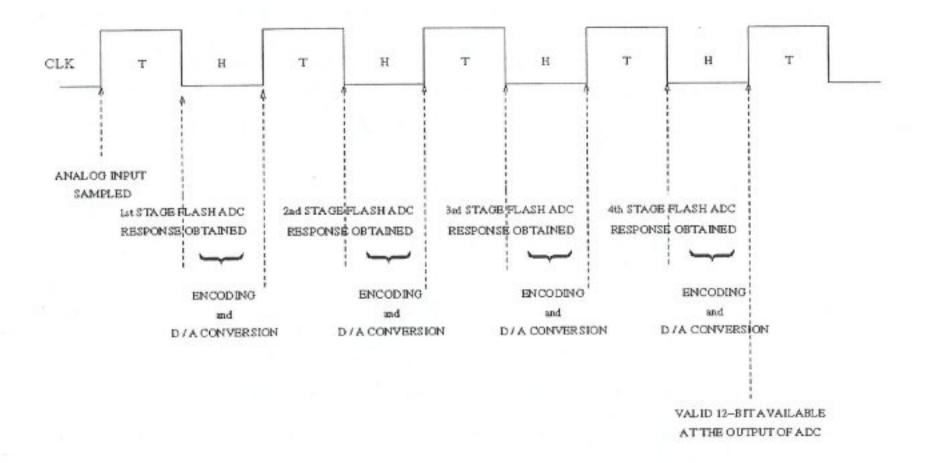

| 8.2  | Four-stage pipelined ADC clocking                                                 |

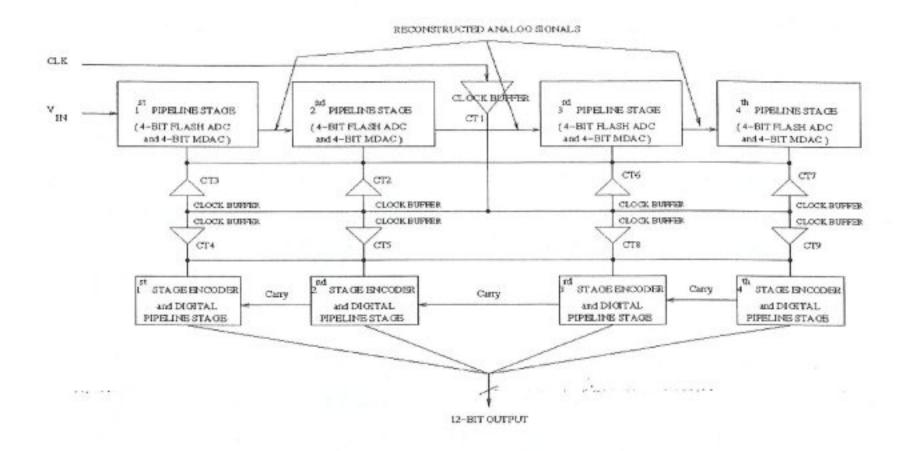

| 8.3  | Block level representation of the proposed clock distribution between             |

|      | functional modules of the pipelined ADC architecture                              |

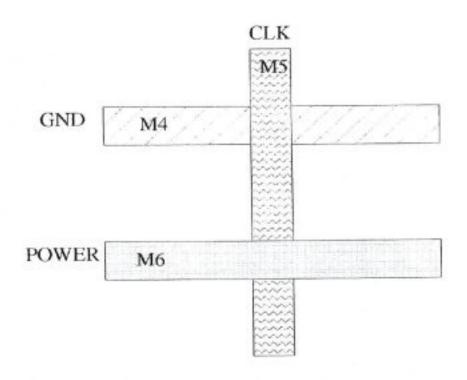

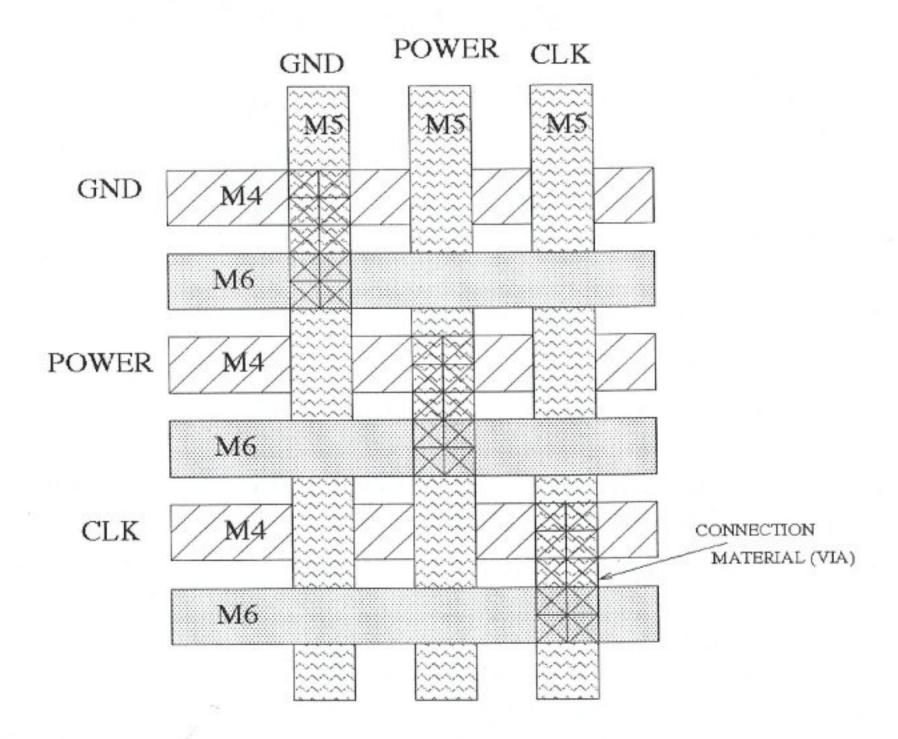

| 8.4  | Assignment of clock signal / power distribution to different metal layes 183      |

| 8.5  | Lattice network consisting of clock and power distribution                        |

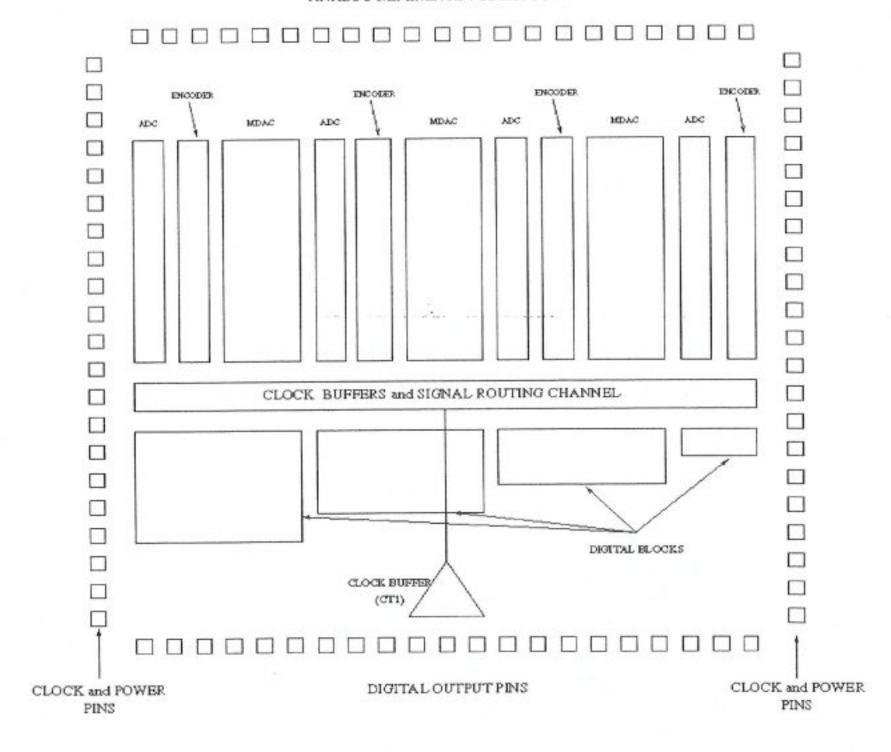

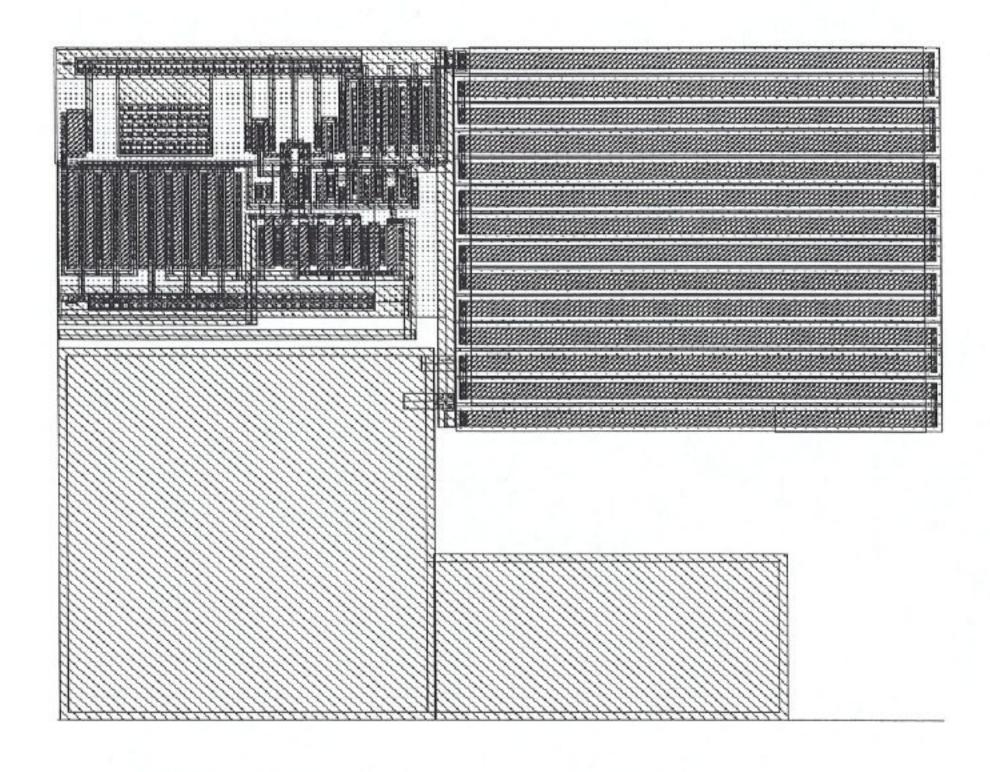

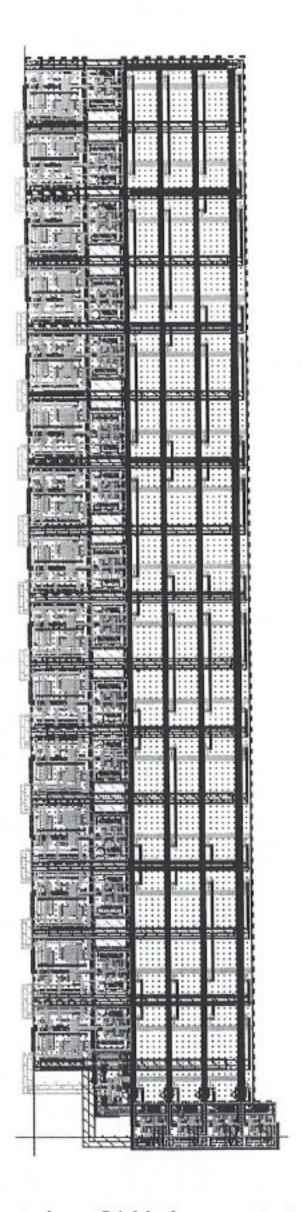

| 8.6  | Top-level floorplan of the designed 12-bit pipelined A/D converter 184            |

## LIST OF TABLES

| 1.1  | Typical applications that require high-speed ADCs 1                     | 5  |

|------|-------------------------------------------------------------------------|----|

| 3.1  | Pipelined A/D converter performance summary 4                           | 1  |

| 3.2  | Parameter limit values applied to Matlab code 4                         | 3  |

| 3.3  | Parameter limit values that will be used in input sitimuli for combined |    |

|      | parameter set Matlab simulations4                                       | 3  |

| 3.4  | Maximum and minimum values obtained for INL-DNL characteristics         |    |

|      | for each parameter4                                                     | 4  |

| 3.5  | Maximum tolerable input parameter set 4                                 | 4  |

| 4.1  | Design specifications of proposed pipelined A/D converter               | 1  |

| 5.1  | Typical specifications of a CMOS op-amp1                                | 02 |

| 5.2  | Aspect ratio table for high open loop-gain OTA1                         | 12 |

| 5.3a | Simulation results of the most important specifications                 | 15 |

| 5.3b | Comparison of simulated and manually calculated pole/zero               |    |

|      | frequencies                                                             | 16 |

| 5.4  | Aspect ratio table for X8 OTA based op-amp configuration                | 17 |

| 5.5a | Simulation results of the most important specifications                 | 19 |

| 5.5b | Comparison of simulated and manually calculated pole/zero frequencies 1 | 20 |

| 5.6  | Aspect ratio table for low open loop-gain OTA1                          | 21 |

| 5.7a | Simulation results of the most important specifications                 | 25 |

| 5.7b | Comparison of simulated and manually calculated pole/zero frequencies 1 | 25 |

| 5.8  | Element aspect ratios of unity gain stable OTA based op-amp 1           | 26 |

| 5.9a | Simulation results of the most important specifications                 | 29 |

| 5.9b | Comparison of simulated and manually calculated pole/zero               |    |

|      | frequencies1                                                            | 29 |

| 6.1  | Encoding strategy of the related pipeline stage                         | 62 |

| 7.1  | Truth table for the full adder circuit                                  | 64 |

| 7.2  | Simulated carry_out dynamic performance results1                        | 68 |

| 7.3  | Simulated sum_out dynamic performance results 1                         | 68 |

| 7.4 | Simulated dynamic characteristics of two-stage master-slave  |

|-----|--------------------------------------------------------------|

|     | DFF circuit                                                  |

| 7.5 | Truth table of exclusive OR function                         |

| 7.6 | Simulated dynamic performance characteristics of XOR circuit |

# DESIGN AND REALIZATION OF A HIGH-SPEED 12-BIT PIPELINED ANALOG / DIGITAL CONVERTER IP BLOCK

## by ZEYNEP TOPRAK

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabancı University

Spring 2001

## © Zeynep TOPRAK 2001

All Rigths Reserved

## DESIGN AND REALIZATION OF A HIGH-SPEED 12-BIT PIPELINED ANALOG / DIGITAL CONVERTER IP BLOCK

### APPROVED BY:

Assoc. Prof. Dr. Yusuf LEBLEBİCİ

(Thesis Supervisor)

Turns Chiles

Asistant Prof. Dr. Yaşar GÜRBÜZ

Assoc. Prof. Dr. Naci İNCİ

M. Szihi

Asistant Prof. Dr. İbrahim TEKİN

20HH

DATE OF APPROVAL:

1 4 Eylül 2001

To my parents,

my sister

and

to my Doc.

### ACKNOWLEDGEMENTS

I would like to thank the following persons and organisations who contributed to my thesis.

First, I would like to thank my supervisor Yusuf Leblebici for his excellent support, assistance and knowledge. I was truly lucky to have the opportunity to work with a supervisor like him.

I am grateful to Alcatel Teletas for funding my graduate studies at Sabancı University. As part of an industry-university collaborate agreement I would like to thank Alcatel Microelectronics (AME) group for supporting my thesis as a commercial project.

My special thanks go to Aslı Arslan Eşme and Geert Evens for their technical advice and support, besides their intensive interest in my work.

I would like to thank also the current members of microelectronics group in Alcatel Teletas, for technical suggestions as well as great collegial working atmosphere.

Last, but by no means the least, I am grateful to my family for their patience and encouragement during my education. Finally, I am most indebted to Engin whose love; understanding and patience made it possible for me to be successfull at the end.

## DESIGN AND REALIZATION OF A HIGH-SPEED 12-BIT PIPELINED ANALOG / DIGITAL CONVERTER IP BLOCK

#### ABSTRACT

This thesis presents the design, verification, system integration and the physical realization of a monolithic high-speed analog-digital converter (ADC) with 12-bit accuracy. The architecture of the ADC has been realized as a pipelined structure consisting of four pipeline stages, each of which is capable of processing the incoming analog signal with 4-bit accuracy. A bit-overlapping technique has been employed for digital error correction between the pipeline stages so that the influence of possible errors that occur during analog signal processing can be minimized. The entire circuit architecture is built with a modular approach, consisting of identical blocks organized into an easily expandable pipeline chain.

All analog as well as digital sub-blocks of the ADC architecture presented in this work operate on a single clock signal (and its inverse), which significantly simplifies the design while ensuring a more robust performance. Other important features of this ADC include small area, single power supply, low power consumption, capability to operate at very high sampling clock rates, and the ability to handle a wide range of input signal amplitudes. The analog processing modules were designed using single-ended signals and the single-ended building blocks (as opposed to differential signals and building blocks) for simplicity. The ADC architecture was realized using a conventional 0.18 micron digital CMOS technology (Foundry: UMC), which ensures a lower overall cost and better portability for the design.

The ADC architecture presented in this work is capable of operating at sampling frequencies of up to 200 MHz, and still can achieve the nominal bit-resolution that was

intended for 12-bit accuracy. The entire circuit is designed with single 1.8 V power supply. The maximum range of the input signal amplitude that the ADC can handle is 1.6 Vpp, with 1.8 V supply voltage. The input signal range as well as the operating points of critical components can be adjusted externally using dedicated control pins. The overall power consumption is estimated as 67.5 mW at 200 MHz sampling rate. Each 4-bit pipeline stage consists of a 4-bit flash A/D converter, a fully capacitive multiplying DAC (MDAC) and the corresponding digital encoding circuitry. The overall silicon area of the ADC is approximately 0.25 mm<sup>2</sup>.

The ADC architecture presented in this thesis is intended as a state-of-the-art data converter for very high-speed applications such as digital video transmission or high bandwidth wireless communication needs. It can be used either as a stand-alone single-chip unit, or as an embedded IP block that can be integrated with other modules on chip.

### ÖZET

Bu tez, 12-bit doğrulukla çalışan bir monolitik yüksek hızlı analog-sayısal dönüştürücünün (ADC) tasarımı, sınanması, sistem düzeyinde tümleştirilmesi ve fiziksel tasarımının gerçekleştirilmesi aşamalarından oluşmuştur. ADC'nin mimarisi, herbiri gelen analog işareti 4-bit doğrulukla işleyebilen dört kademeden oluşan bir veri yolu yapısı olarak gerçekleştirilmiştir. Analog işaret işlenmesi sırasında meydana gelebilecek olası hataların etkisini en aza indirebilmek amacı ile veri yolu kademeleri arasındaki sayısal hataları düzeltmek için bir bit-çakıştırma tekniği kullanılmıştır. Devrenin tüm mimarisi, benzer blokların kolayca genişletilebilir bir veriyolu zinciri biçiminde dizilmesinden oluşan, modüler bir yaklaşımla şekillendirilmiştir.

Bu çalışma kapsamında ele alınan ADC mimarisinin tüm analog ve sayısal altblokları, tasarımı belirgin biçimde basitleştirmek ve aynı zamanda blokların daha güvenli olarak çalışmalarını sağlamak amacıyla, tek saat işareti (ve tersi) ile işlem yapabilecek şekilde tasarlanmıştır. Bu ADC'nün diğer önemli özellikleri arasında küçük kırmık alanı, tek güç kaynağı kullanılması, düşük güç gereksinimi, çok yüksek örnekleme hızlarında ve geniş bir giriş işareti genliği alanı içinde çalışabilme kabiliyeti sayılabilir. Çalışma kolaylığı nedeniyle, analog işlem modülleri, diferansiyel işaret ve yapısal bloklar yerine, tek uçlu işaretler ve tek sonlu yapısal bloklar kullanılarak tasarlanmıştır. Bu tezde sunulan ADC mimarisi, daha düşük toplam maliyet ve tasarıma daha iyi taşınabilirlik sağlamak amacıyla, endüstride yaygın olarak kullanılan 0.18 mikron sayısal CMOS teknolojisi (Foundry: UMC) kullanılarak gerçekleştirilmiştir. Tasarlanan dönüştürücü devresi, 200 MHz örnekleme frekansına kadar doğru çalışabilme ve bu yüksek örnekleme hızında hedeflenmiş olan 12-bit çözünürlüğü elde edebilme özelliklerine sahiptir. Devrenin tamamı bir tek 1.8 V güç kaynağı ile beslenebilecek şekilde tasarlanmıştır. ADC'nin 1.8 V besleme gerilimi ile işleyebileceği en yüksek giriş işareti genliği (tepeden tepeye) 1.6 Vpp'dir. Giriş işareti genliği ve bununla birlikte kritik modüllerin çalışma noktaları, denetleme girişleri yardımıyla dışarıdan ayarlanabilir. 200 MHz örnekleme hızında, toplam güç tüketimi 67.5 mW olarak öngörülmektedir. Her 4-bitlik veri yolu kademesi, bir adet 4-bit flash A/D dönüştürücü, bir adet tamamen kapasitif çarpıcı DAC (MDAC) ve bunlarla birlikte çalışacak sayısal çözümleyici devrelerden oluşmaktadır. ADC'nin toplam silikon alanı yaklaşık 0.25 mm²'dir.

Bu tez çalışmasında tasarlanan ADC mimarisi, sayısal görüntü iletimi veya yüksek bant genişliğine sahip telsiz haberleşme gereksinimleri gibi çok yüksek hız gerektiren uygulamalarda kullanılmak amacıyla tasarlanmıştır. Bu dönüştürücü, tek başına bir kırmık olarak veya daha büyük bir kırmık üzerine başka modüllerle birleştirilebilecek bir IP (intellectual property) bloğu olarak kullanılabilir.

### TABLE OF CONTENTS

| 1 | ····Intro | duction                                         | 1  |

|---|-----------|-------------------------------------------------|----|

|   | 1.1       | Serial A/D Converters                           | 4  |

|   | 1.2       | Successive Approximation A/D Converters         | 7  |

|   | 1.3       | Parallel A/D Converters                         | 11 |

| 2 | Perfo     | rmance Measures of Analog-to-Digital Converters | 16 |

|   | 2.1       | Quantization Error                              | 16 |

|   | 2.2       | Quantization Noise                              | 17 |

|   | 2.3       | Dynamic Range                                   | 18 |

|   | 2.4       | Resolution                                      | 19 |

|   | 2.5       | Effective Number of Bits (ENOB)                 | 19 |

|   | 2.6       | Differential Nonlinearity (DNL)                 | 19 |

|   | 2.7       | Integral Nonlinearity (INL)                     | 20 |

|   | 2.8       | Absolute Accuracy                               | 22 |

|   | 2.9       | Gain Error                                      | 23 |

|   | 2.10      | Offset Error                                    | 24 |

|   | 2.11      | Transition Level                                | 24 |

|   | 2.12      | Monotonicity                                    | 26 |

|   | 2.13      | Missing Code                                    | 26 |

|   | 2.14      | Differential Phase and Gain                     | 27 |

|   | 2.15      | Conversion Time and Sampling Rate               | 27 |

|   | 2.16      | Sampling-Time Uncertainty                       | 28 |

|   | 2.17      | Input Bandwidth                                 | 29 |

| 3 | Pipel | Pipelined Analog-to-Digital Converters 3                       |       |  |

|---|-------|----------------------------------------------------------------|-------|--|

|   | 3.1   | Pipelined Operation                                            |       |  |

|   | 3.2   | Circuit Implementation of a Pipeline Stage41                   |       |  |

|   | 3.3   | Matlab Simulation Results                                      |       |  |

| 4 | Arch  | tecture Components: Voltage Comparator Design 51               |       |  |

|   | 4.1   | Pipelined ADC Architecture Overview                            |       |  |

|   | 4.2   | Voltage Comparators: Basic Concepts                            |       |  |

|   |       | 4.2.1 Model of a voltage comparator                            |       |  |

|   |       | 4.2.2 Examples of CMOS comparator circuits                     |       |  |

|   | 4.3   | Examples of State-of-Art Voltage Comparators                   |       |  |

|   | 4.4   | Proposed Voltage Comparator Architecture                       |       |  |

|   |       | 4.4.1 Basic comparator circuit                                 |       |  |

|   |       | 4.4.2 Full complementary voltage comparator                    |       |  |

|   |       | 4.4.3 Improved full complementary voltage comparator 79        |       |  |

|   |       | 4.4.4 Low power version of the complementary comparator 93     | 10.20 |  |

| 5 | Arch  | tecture Components: High-Speed Op-amp Design 95                | ,     |  |

|   | 5.1   | Introduction of Basic Concepts                                 |       |  |

|   | 5.2   | OTA Based Op-amp Design Flow                                   |       |  |

|   | 5.3   | Inverter-Based Output Stage Frequency Analysis                 |       |  |

|   | 5.4   | OTA Based High-Gain Op-amp Design                              |       |  |

|   | 5.5   | OTA Based Low-Gain Op-amp Design                               |       |  |

|   | 5.6   | OTA Based Op-amp Designed for Unity Gain Configuration 12      |       |  |

| 6 | Desi  | n of ADC/MDAC Pipeline Stages                                  | 6     |  |

|   | 6.1   | Design of the 4-Bit Flash A/D Converter                        | 8     |  |

|   | 6.2   | Digital-to-Analog Converter Design                             | 4     |  |

|   |       | 6.2.1 Current weighting D/A converter using ladder networks 14 | 5     |  |

|   |       | 6.2.2 Self-calibrating D/A converters                          | 6     |  |

|   |       | 6.2.3 Voltage and charge-scaling D/A converters                | 6     |  |

|   | 6.3   | Error Correction with Bit-Overlapping                          | 9     |  |

| 7   | Desig    | n of Digital Buildi | ng Blocks                        | 163 |

|-----|----------|---------------------|----------------------------------|-----|

|     | 7.1      | Full Adder Design   | n                                | 163 |

|     |          | 7.1.1 Single-b      | it adders                        | 164 |

|     |          | 7.1.2 Bit-para      | llel adder                       | 167 |

|     | 7.2      | D-type Flip-Flop    | (DFF) Design                     | 169 |

|     | 7.3      | Exclusive OR Ga     | te Design                        | 173 |

| 8   | Тор-     | Level Construction  | of the Pipelined ADC             | 177 |

|     | 8.1      | Overall Structure   | of the Pipeline                  | 177 |

|     | 8.2      | Timing Considera    | ations                           | 179 |

|     | 8.3      | General Floor-Pla   | anning and Layout Considerations | 181 |

| 9   | Con      | lusions             |                                  | 186 |

| A   | Lite     | ature Survey on A   | nalog-to-Digital Converters      | 189 |

| В   | Con      | plete Circuit Sche  | matics and Mask Layouts          | 201 |

| Bib | liograpl | у                   |                                  | 214 |

## LIST OF FIGURES

| 1.1  | Black box representation of an A/D converter                                |

|------|-----------------------------------------------------------------------------|

| 1.2  | Block diagram of single slope serial A/D converter 4                        |

| 1.3  | Block diagram of a dual-slope A/D converter 5                               |

| 1.4  | Waveforms of the dual-slope A/D converter in Figure 1.3 6                   |

| 1.5  | Example of successive approximation A/D converter                           |

| 1.6  | The successive approximation process                                        |

| 1.7  | Pipeline implementation of the algorithmic A/D converter                    |

| 1.8  | Implementation of the iterative, algorithmic A/D converter                  |

| 1.9  | A 3-bit, parallel (flash) A/D converter                                     |

| 1.10 | A time-interleaved A/D converter array                                      |

| 1.11 | Block representation of two-step flash A/D converter architecture           |

| 1.12 | Two-stages pipelined A/D converter configuration                            |

| 1.13 | Qualitative comparison of ADC techniques                                    |

| 2.1  | Input-output characteristics of an ideal 3-bit A/D converter and its        |

|      | quantization error                                                          |

| 2.2  | Illustration of DNL                                                         |

| 2.3  | Illustration of INL for a 3-bit A/D converter                               |

| 2.4  | Relation of DNL and INL                                                     |

| 2.5  | Absolute accuracy is the summation of other error sources                   |

| 2.6  | Illustration of gain error                                                  |

| 2.7  | Illustration of offset error                                                |

| 2.8  | Illustration of transition level                                            |

| 2.9  | A nonmonotonic ADC transfer function                                        |

| 2.10 | An ADC transfer function with a missing code (100)27                        |

| 2.11 | Illustration of sample period and conversion time                           |

| 3.1  | Typical two-step A/D converter architecture                                 |

| 3.2  | Multi-step A/D converter figure of performance illustration                 |

| 3.3  | Multi-step A/D converter's figure of performance illustration with internal |

|      | amplification                                                               |

|      |                                                                             |

| 3.4  | A simple pipelined A/D converter architecture33                               |

|------|-------------------------------------------------------------------------------|

| 3.5  | Implementation of i <sup>th</sup> stage of a pipelined converter              |

| 3.6  | A pipelined A/D converter architecture model with offset and gain error       |

|      | for both the S/H amplifier and the residue amplifier35                        |

| 3.7  | A 3-bit (1-bit per stage) pipelined A/D converter35                           |

| 3.8  | Implementation of each stage of Figure 3.735                                  |

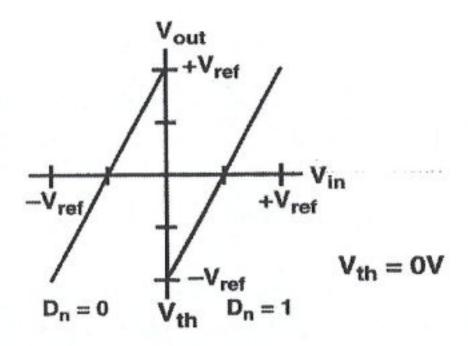

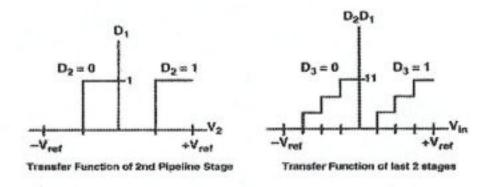

| 3.9  | The transfer function of the 1-bit stage shown in Figure 3.8                  |

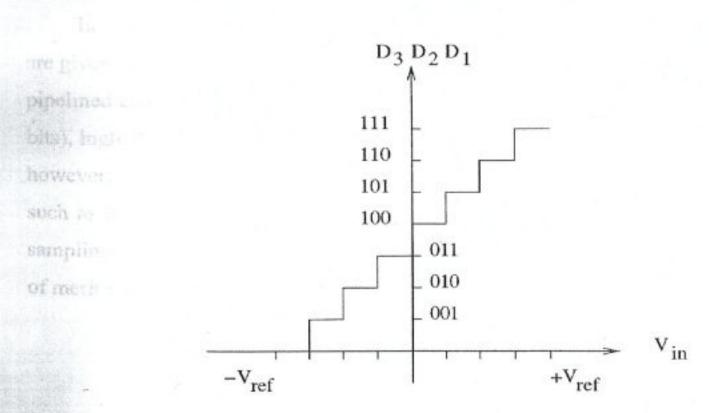

| 3.10 | Transfer function of 3-bit pipelined A/D converter                            |

| 3.11 | Detailed transfer function characteristics                                    |

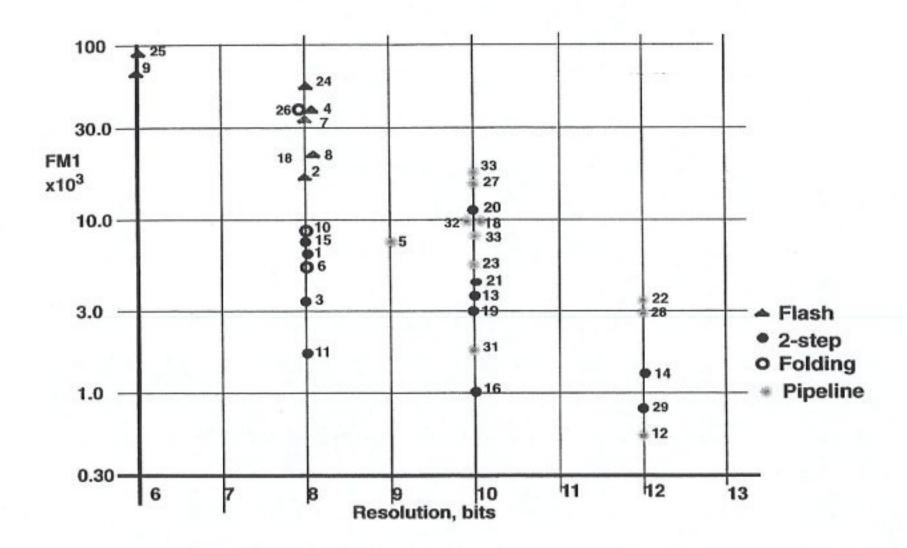

| 3.12 | Comparison of speed figure of merit, between Flash, 2-Step and                |

|      | Pipelined ADCs                                                                |

| 3.13 | Comparison of power figure of merit, between Flash, 2-Step and                |

|      | Pipelined ADCs39                                                              |

| 3.14 | Implementation of i <sup>th</sup> stage of a pipelined converter              |

| 3.15 | INL envelope obtained for different input voltage ranges                      |

| 3.16 | DNL envelope obtained for different input voltage ranges                      |

| 3.17 | INL envelope obtained for different resistor voltage variations               |

| 3.18 | DNL envelope obtained for different resistor voltage variations               |

| 3.19 | INL envelope obtained for different comparator offsets                        |

| 3.20 | DNL envelope obtained for different comparator offsets                        |

| 3.21 | INL envelope obtained for different supply voltage variations                 |

| 3.22 | DNL envelope obtained for different supply voltage variations                 |

| 3.23 | INL envelope obtained for combined parameter set simulations                  |

| 3.24 | DNL envelope obtained for combined parameter set simulations 50               |

| 4.1  | Simplified block diagram of the proposed A/D converter architecture 52        |

| 4.2  | Detailed circuit architecture for one of the four proposed pipeline stages 52 |

| 4.3  | Circuit symbol for a comparator54                                             |

| 4.4  | Zero-order transfer curve of a comparator                                     |

| 4.5  | Zero-order model for a comparator55                                           |

| 4.6  | First-order transfer curve of a comparator                                    |

| 4.7  | First-order model of comparator                                               |

| 4.8  | First-order transfer curve of a comparator including offset                   |

| 4.9  | First-order model of a comparator including offset. The ± sign of the         |

|      | offset voltage accounts for the fact that Vos is unknown in polarity 57       |

| 4.10 | Time domain response of a non-inverting first-order comparator 58                |

|------|----------------------------------------------------------------------------------|

| 4.11 | Current-sink inverter functioning as a comparator 59                             |

| 4.12 | DC transfer curve of simple comparator59                                         |

| 4.13 | Differential voltage comparator schematic                                        |

| 4.14 | DC transfer curve of a differential voltage comparator                           |

| 4.15 | Two-stage voltage comparator61                                                   |

| 4.16 | Comparator hysteresis curve                                                      |

| 4.17 | Comparator with hysteresis applied to the input differential stage only 63       |

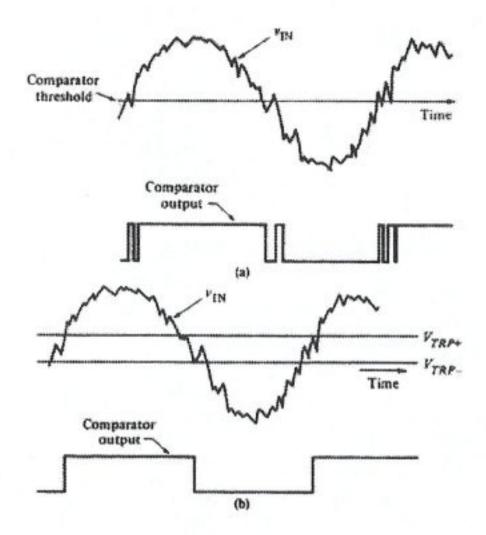

| 4.18 | (a) Comparator response to a noisy input (b) Comparator response to              |

|      | noisy input when hysteresis is added                                             |

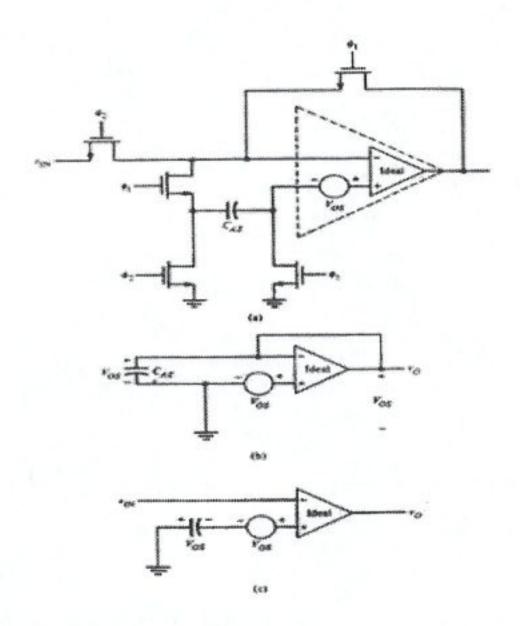

| 4.19 | (a) Circuit implementation of an auto-zeroed comparator (b) Comparator           |

|      | during φ <sub>1</sub> auto-sero state (c) Comparator during φ <sub>2</sub> state |

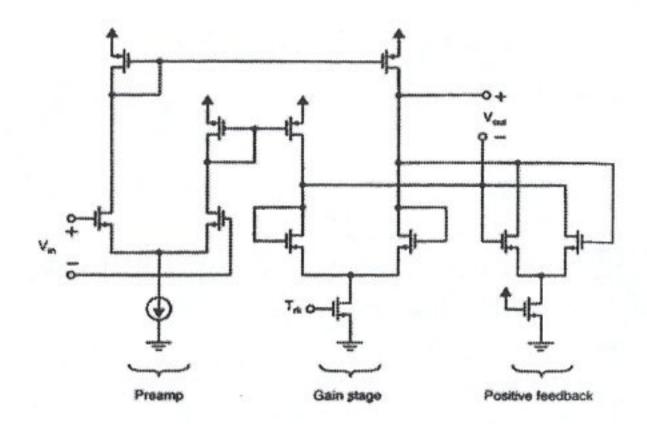

| 4.20 | A two-stage comparator that has a preamplifier and a positive-feedback           |

|      | track-and-latch state                                                            |

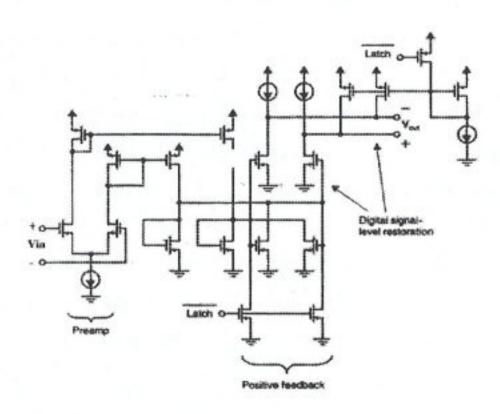

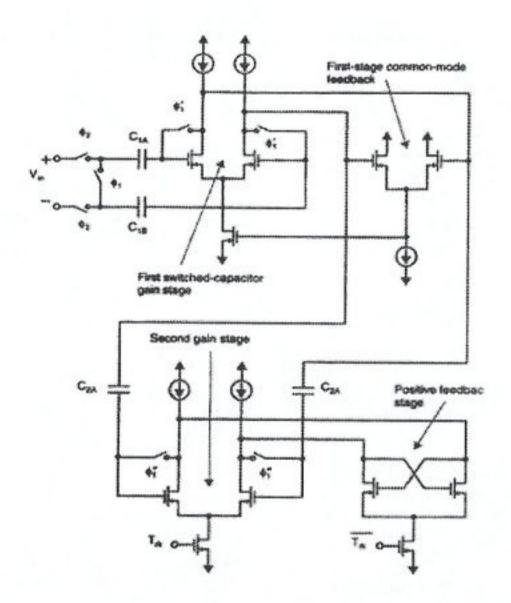

| 4.21 | A two-stage comparator 66                                                        |

| 4.22 | A two-stage comparator with capacitive coupling to eliminate input-offset        |

|      | voltage and clock-feedthrough errors along with positive-feedback for fast       |

|      | operation                                                                        |

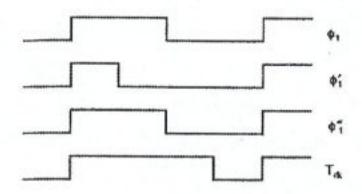

| 4.23 | The clock waveforms required by the comparator in Figure 4.22                    |

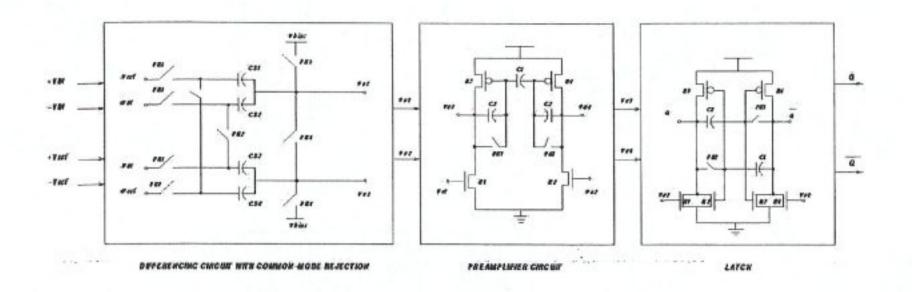

| 4.24 | A fully differential comparator with two nonoverlapping clocks by                |

|      | Lewis and Hurst                                                                  |

| 4.25 | A comparator by Razavi an Wooley69                                               |

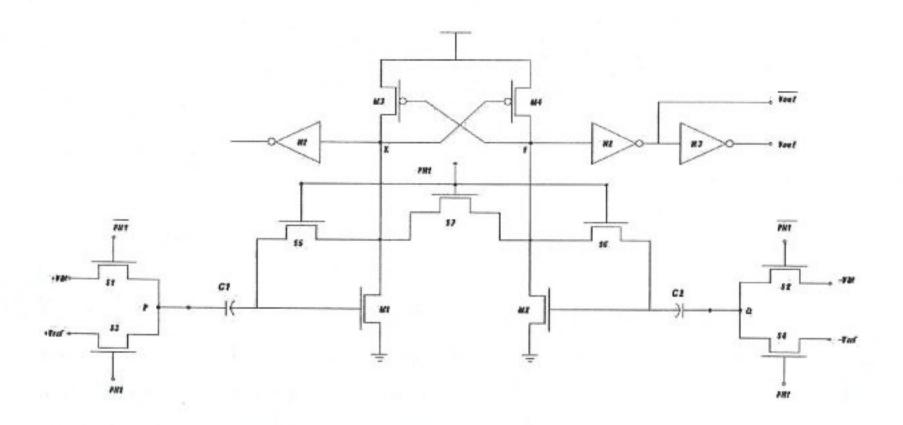

| 4.26 | A fully differential, high-speed voltage comparator 70                           |

| 4.27 | Timing information for the comparator given in Figure 4.26                       |

| 4.28 | Regeneration process small signal equivalent                                     |

| 4.29 | Basic voltage comparator schematic                                               |

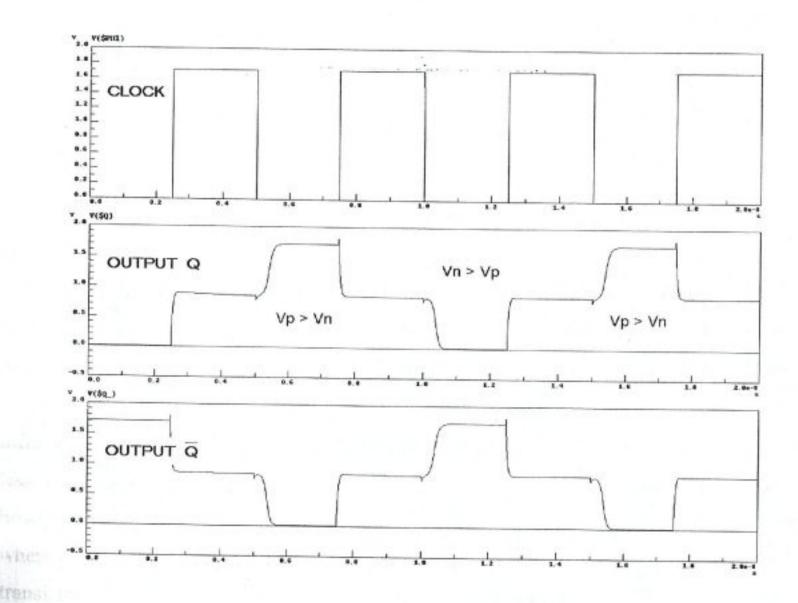

| 4.30 | Output waveforms of basic voltage comparator circuit                             |

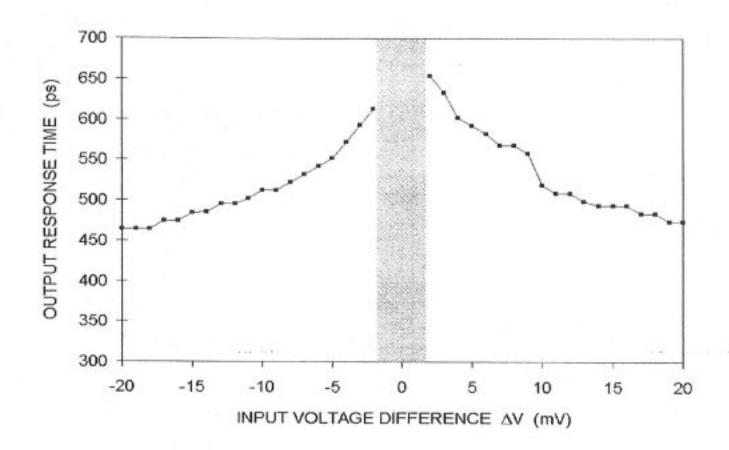

| 4.31 | Response time v.s input voltage difference                                       |

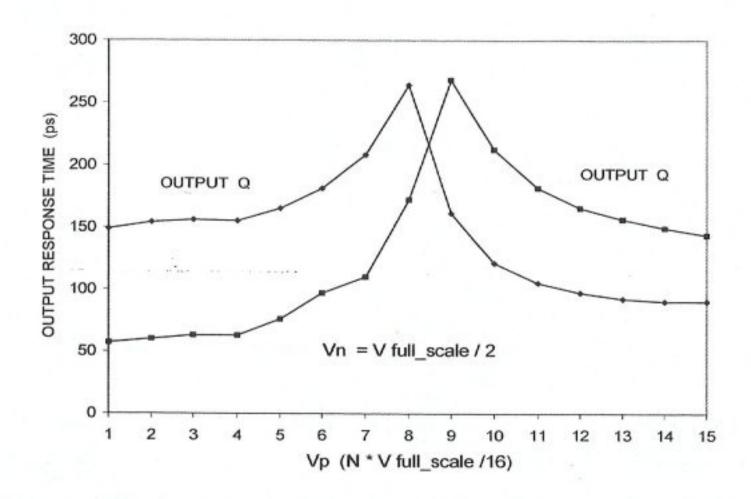

| 4.32 | Response time variation along the entire input dynamic range for basic           |

|      | voltage comparator (V <sub>full-scale</sub> = 1.8V)                              |

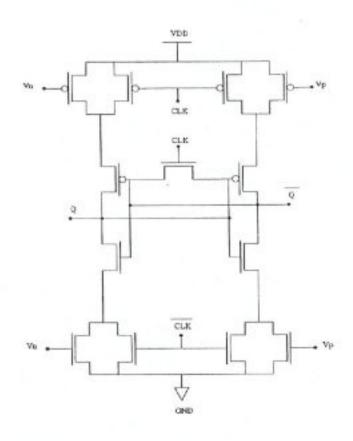

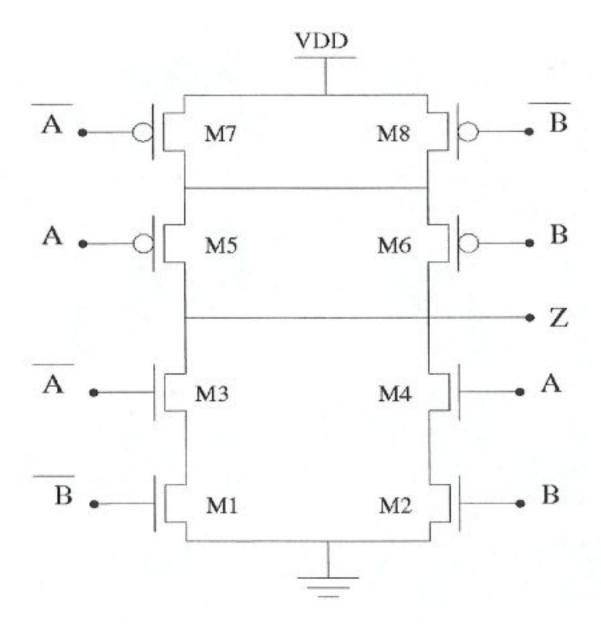

| 4.33 | Fully-complementary voltage comparator circuit diagram 78                        |

| 4.34 | Improved full complementary voltage comparator circuit                           |

| 4.35 | Response time of improved full complementary comparator with respect             |

|      | to input voltage difference                                                      |

| 4.36 | Response times of the improved full complementary voltage comparator,               |

|------|-------------------------------------------------------------------------------------|

|      | obtained for the entire input range81                                               |

| 4.37 | Response times obtained for different input voltage differences                     |

| 4.38 | Power consumption for different input voltage differences                           |

| 4.39 | Power consumption for different sampling frequencies 82                             |

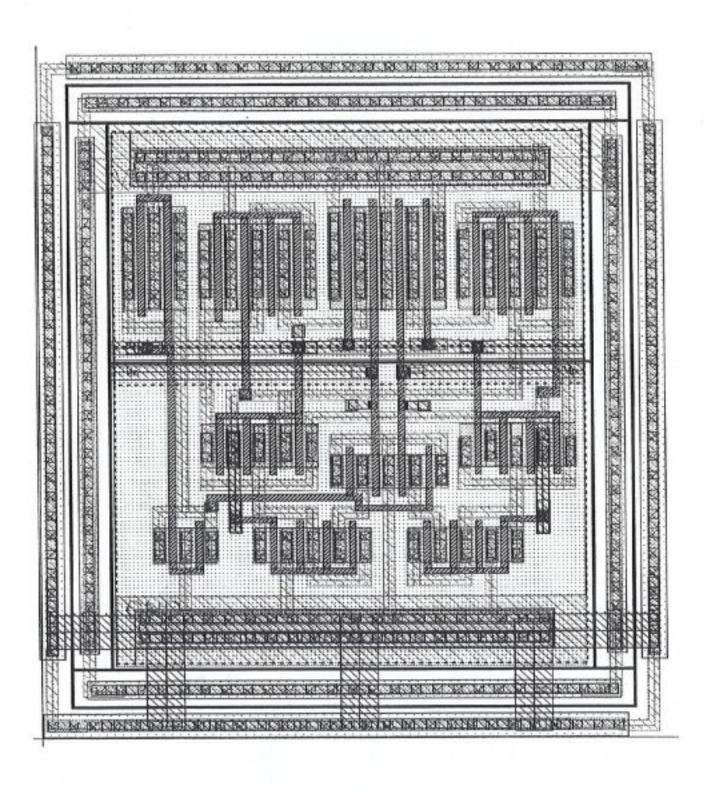

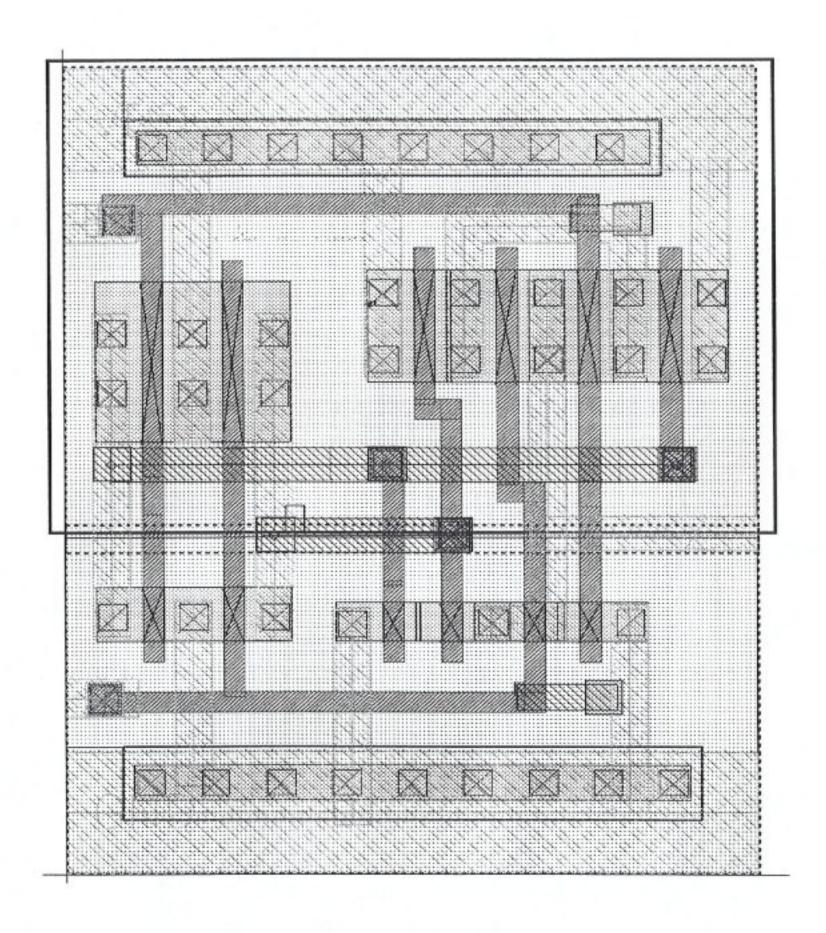

| 4.40 | Layout of the improved complementary-in voltage comparator 83                       |

| 4.41 | Four bits ADC/MDAC schematic used in improved full complementary                    |

|      | voltage comparator verification 84                                                  |

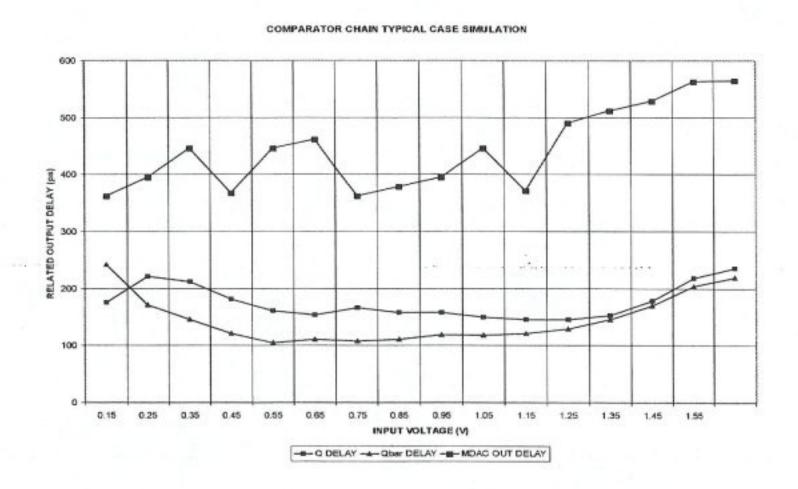

| 4.42 | Response times for Q, $\overline{Q}$ and MDAC output voltage in ideal conditions 85 |

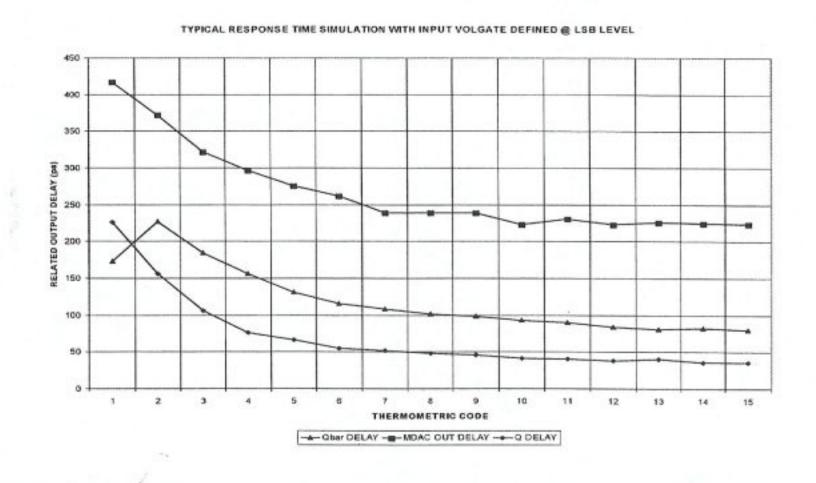

| 4.43 | Response times obtained for input voltage at LSB level, typical corner              |

|      | and nMOS input stage transistor with mismatch                                       |

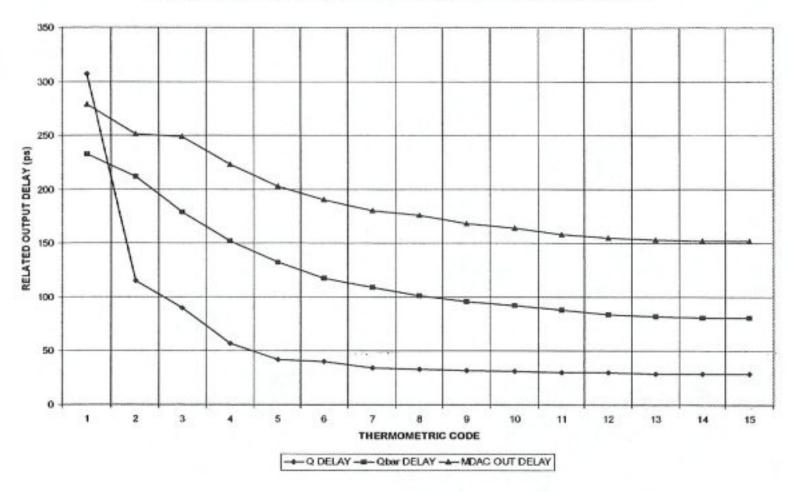

| 4.44 | Response times obtained for input voltage at LSB level, typical corner              |

|      | and pMOS input stage transistor with mismatch 86                                    |

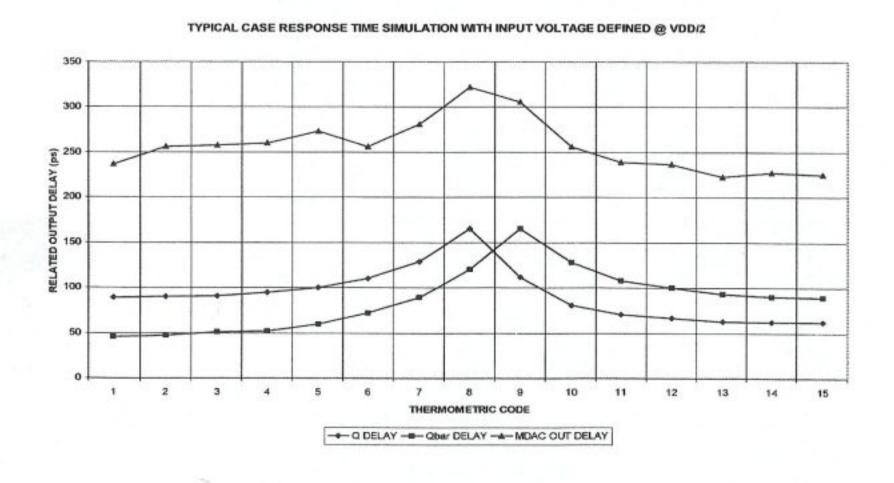

| 4.45 | Response times obtained for input voltage at Vfull_scale/2 level, typical           |

|      | corner and nMOS input stage transistor with mismatch 86                             |

| 4.46 | Response times obtained for input voltage at Vfull_scale level, typical             |

|      | corner and pMOS input stage transistor with mismatch 87                             |

| 4.47 | Response times obtained for input voltage at MSB level, typical corner              |

|      | and nMOS input stage transistor with mismatch 87                                    |

| 4.48 | Response times obtained for, typical corner simulations for 500 MHz                 |

|      | clock frequency                                                                     |

| 4.49 | Response times obtained for typical corner simulations for 750 MHz                  |

|      | clock frequency                                                                     |

| 4.50 | Response times obtained for typical corner simulations for 1 GHz clock              |

|      | frequency                                                                           |

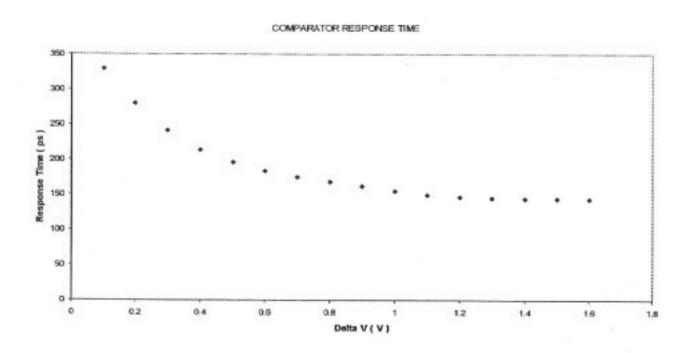

| 4.51 | Worst-case response time v.s input voltage in a simulated 4-bit ADC 90              |

| 4.52 | Avarage power dissipation of the comparator circuits vs. sampling                   |

|      | frequency91                                                                         |

| 4.53 | Integral non-linearity obtained with improved full complementary                    |

|      | comparator for typical simulation corner92                                          |

| 4.54 | Differential non-linearity obtained with improved full complementary                |

|      | comparator for typical simulation corner92                                          |

| 4.55 | Comparator circuit with latched output stage during reset mode              |

|------|-----------------------------------------------------------------------------|

|      | (Low power comparator version)93                                            |

| 5.1  |                                                                             |

|      | illustrating some possible errors96                                         |

| 5.2  | Behavioral model for ideal differential input, single-ended output          |

|      | op-amp                                                                      |

| 5.3  | A model for an ideal op-amp showing some of the nonideal                    |

|      | characteristics99                                                           |

| 5.4  | Typical frequency response for an op-amp 100                                |

| 5.5  | The differential OTA symbol and ideal model 103                             |

| 5.6  | Symmetrical CMOS OTA schematic                                              |

| 5.7  | Inverter-based output stage schematic 108                                   |

| 5.8  | Simplified small signal equivalent of the inverter 109                      |

| 5.9  | Equivalent circuit of Figure 5.8                                            |

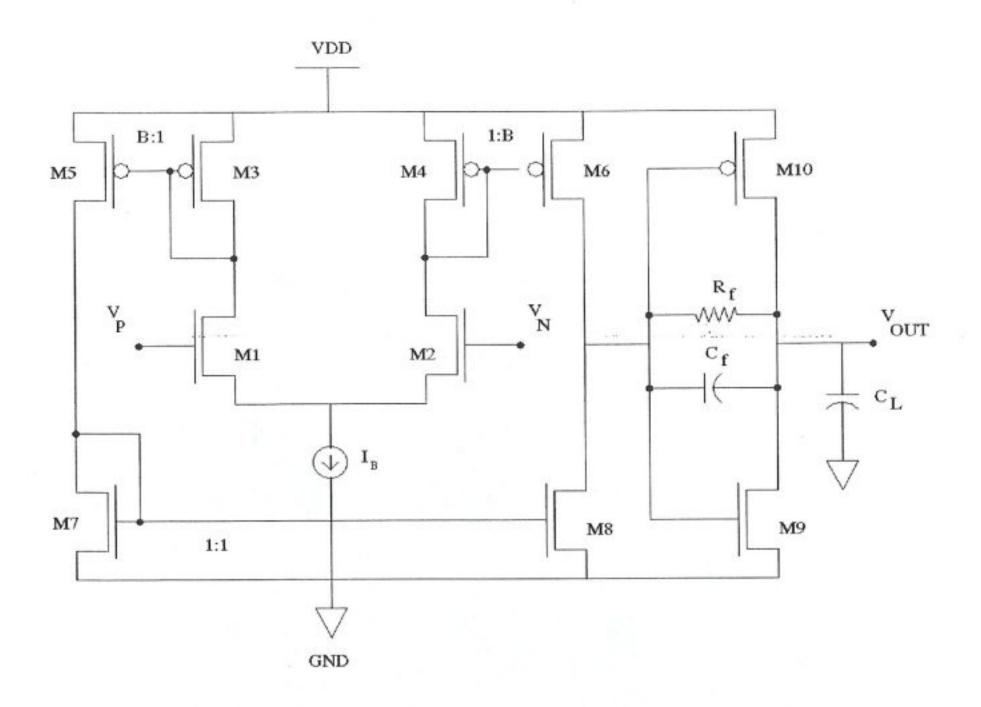

| 5.10 | High open loop-gain OTA based op-amp schematic                              |

| 5.11 | DC characteristics of high open loop-gain OTA based op-amp 113              |

| 5.12 | Open loop AC characteristics of high open loop-gain OTA based               |

|      | op-amp                                                                      |

| 5.13 | Closed loop AC characteristics of high open loop-gain OTA based             |

|      | op-amp                                                                      |

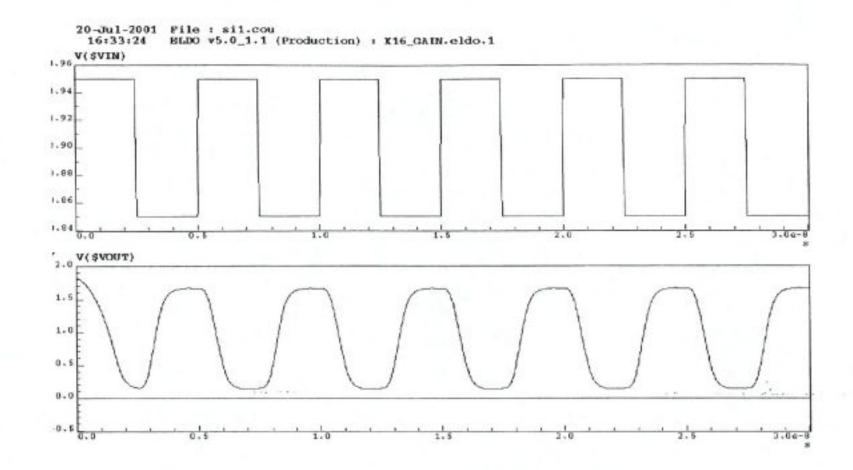

| 5.14 | Transient characteristics of high open loop-gain OTA used in X16 feedback   |

|      | gain for residue amplifier for a 200 MHz 100 mV <sub>pp</sub> input pulse   |

| 5.15 | DC characteristics of X8 OTA based op-amp                                   |

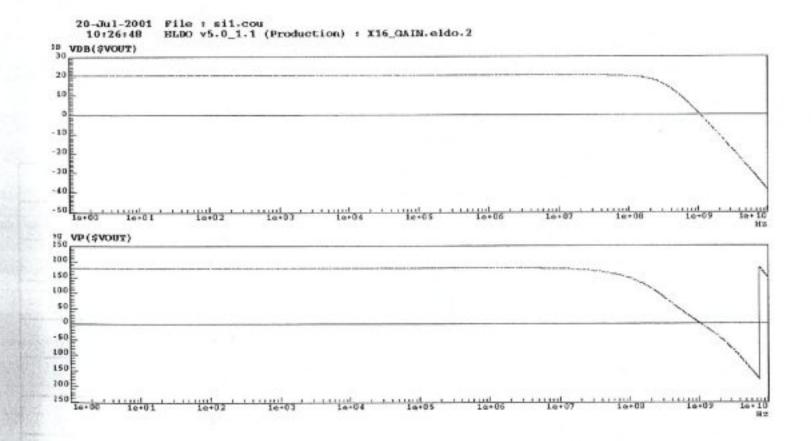

| 5.16 | Open loop AC characteristics of X8 OTA based op-amp                         |

| 5.17 | Closed loop AC characteristics of X8 OTA based op-amp                       |

| 5.18 | Transient response of X8 OTA based op-amp to a 200 MHz 100 mV <sub>pp</sub> |

|      | input pulse                                                                 |

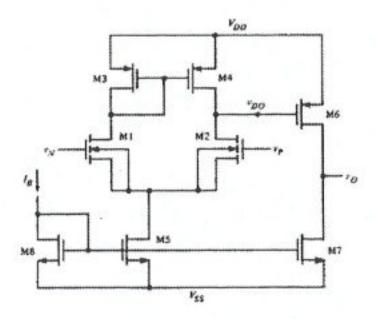

| 5.19 | Schematic view of low open loop-gain OTA                                    |

| 5.20 | Dc characteristics of low open loop-gain OTA based op-amp                   |

| 5.21 | Open loop AC characteristics of low open loop-gain OTA based                |

|      | op-amp                                                                      |

| 5.22 | Closed loop AC characteristics of low open loop gain OTA based              |

|      | op-amp                                                                      |

|      | 124                                                                         |

| 5.23 | Transient response of X2 feedback configuration to a 200 MHz               |

|------|----------------------------------------------------------------------------|

|      | 800 mV <sub>pp</sub> input pulse signal                                    |

| 5.24 | DC characteristics of unity gain stable OTA based op-amp                   |

| 5.25 | Open loop AC characteristics of unity gain stable OTA based op-amp 127     |

| 5.26 | Closed loop AC characteristics of unity gain stable OTA based op-amp 128   |

| 5.27 | Transient response of unity gain stable OTA based op-amp to a 200 MHz      |

|      | 10 mV <sub>pp</sub> input pulse signal                                     |

| 5.28 | Block representation of sample-and-hold circuit                            |

| 5.29 | Block representation of residue amplifier                                  |

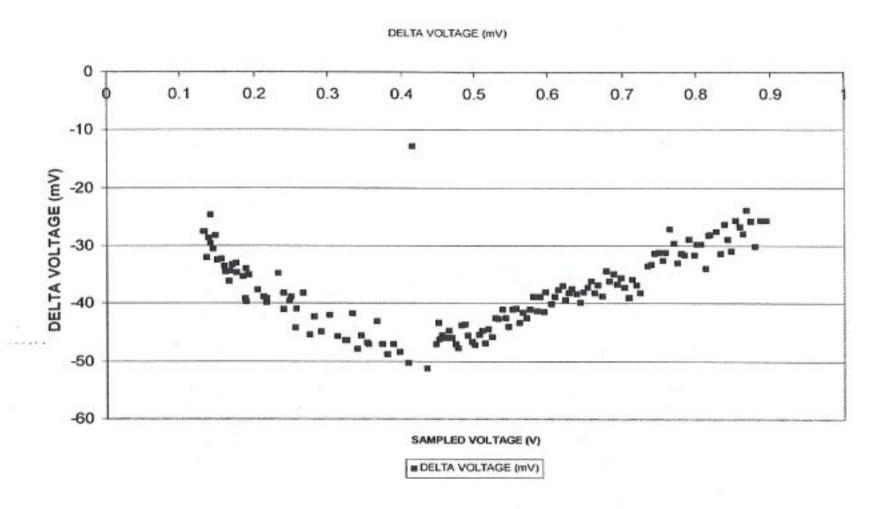

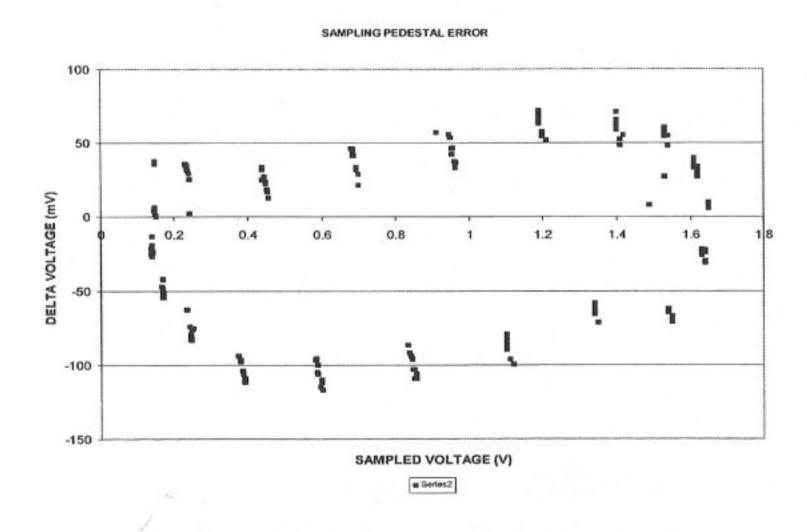

| 5.30 | Sampled voltage versus sampling pedestal, where input signal frequency     |

|      | is 50 kHz and sampling clock frequency is 200 MHz131                       |

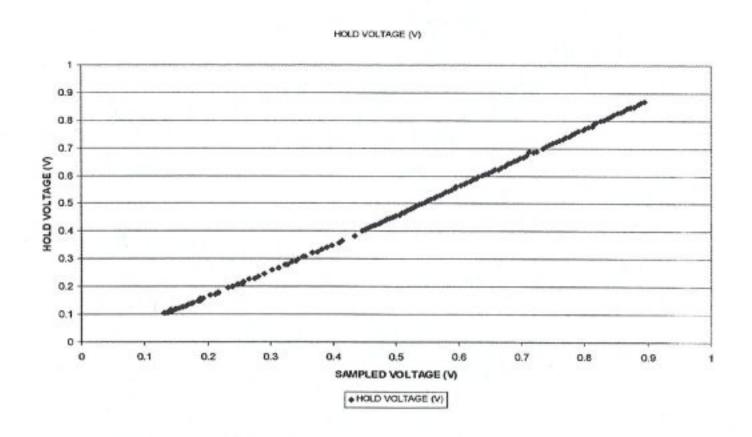

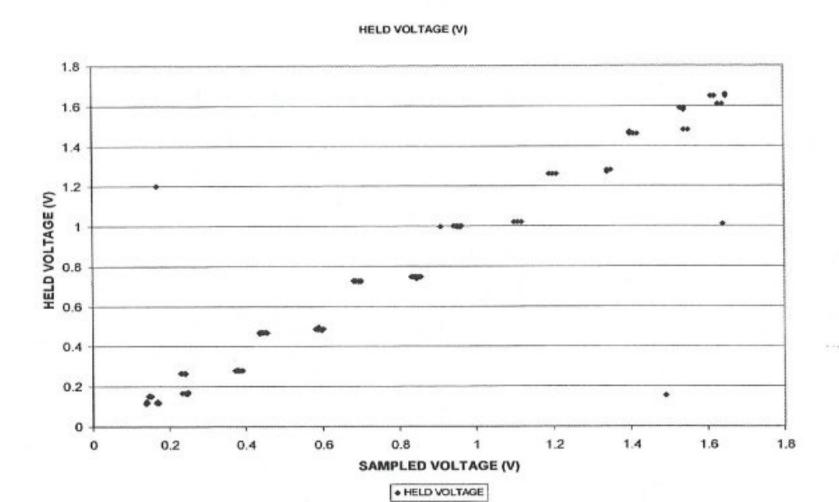

| 5.31 | Sampled voltage versus held voltage, where input signal frequency is       |

|      | 50 kHz and sampling clock frequency is 200 MHz                             |

| 5.32 | Sampled voltage versus settling time, input signal frequency is 50 kHz     |

|      | and sampling clock frequency is 200 MHz132                                 |

| 5.33 | Sampled voltage versus sampling pedestal, where input signal frequency     |

|      | is 30 MHz and sampling clock frequency is 200 MHz                          |

| 5.34 | Sampled voltage versus held voltage, where input signal frequency is       |

|      | 30 MHz and sampling clock frequency is 200 MHz                             |

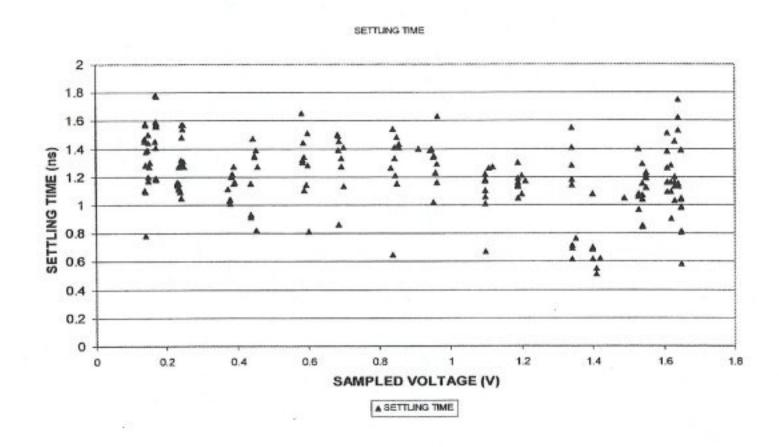

| 5.35 | Sampled voltage versus settling time, input signal frequency is 30 MHz     |

|      | and sampling clock frequency is 200 MHz                                    |

| 5.36 | Residue voltage obtained versus input voltage for typical simulation       |

|      | corner                                                                     |

| 5.37 | Amplified residue voltage by X8 amplification factor                       |

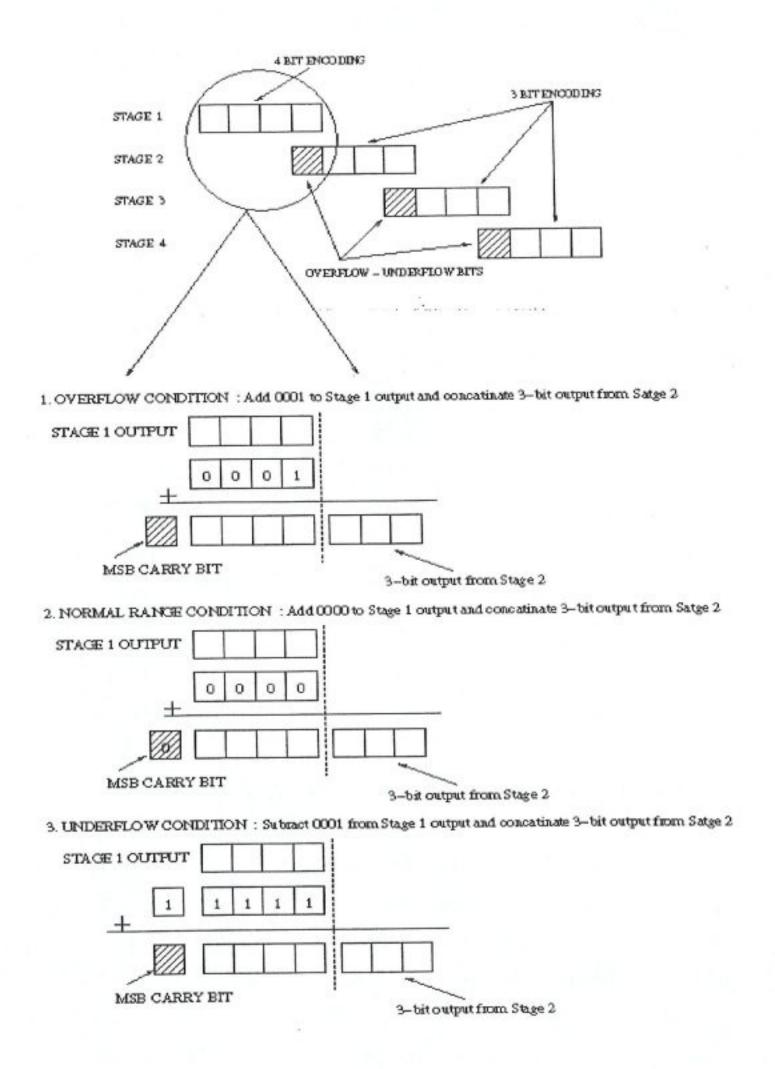

| 6.1  | Four stage pipelined A/D converter schematic. Ai and Bi bits are overflow  |

|      | and underflow bits respectively. They will be explained in detail later in |

|      | this chapter                                                               |

| 6.2  | Simplified schematic of one stage of a 4-bit pipeline ADC                  |

| 6.3  | DC input-output characteristics of a 4-bit piepline A/D converter          |

| 6.4  | Typical corner DNL plot for the 4-bit A/D converter                        |

| 6.5  | Typical corner INL plot for the 4-bit A/D converter                        |

| 6.6  | Typical FFT plot obtained for a 4-bit A/D converter when the input signal  |

|      | frequency is 10 MHz and the sampling clock frequency is 300 MHz 140        |

| 6.7  | SNR of the 4-bit ADC as a function of sampling frequency, with input signal       |

|------|-----------------------------------------------------------------------------------|

|      | frequency of 10 MHz and the sampling clock frequency is varied from               |

|      | 50 MHz to 300 MHz                                                                 |

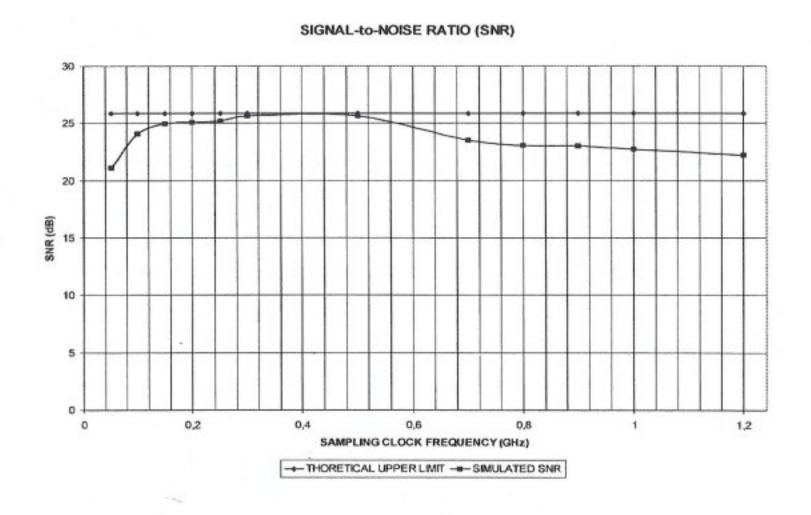

| 6.8  | SNR of the 4-bit ADC as a function of sampling frequency, with input              |

|      | signal frequency of 10 MHz and the sampling clock frequency is varied             |

|      | from 500 MHz to 1.2 GHz                                                           |

| 6.9  | Overall variation of SNR as a function of the sampling ferquency, with input      |

|      | signal frequency of 10 MHz                                                        |

| 6.10 | SNT of the 4-bit ADC as a function of input signal frequency, with                |

|      | sampling clock frequency of 200 MHz and the input signal frequency is             |

|      | varied from 10 MHz to 80 MHz                                                      |

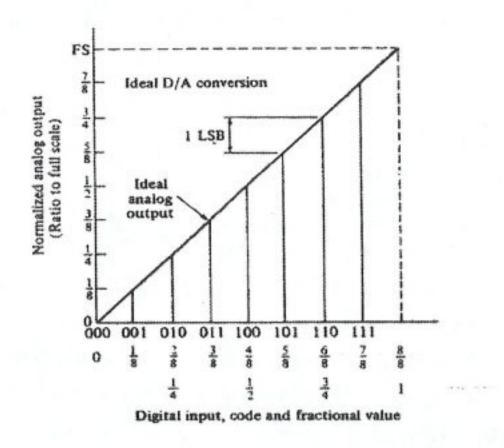

| 6.11 | Ideal input-output characteristics for a three bit D/A converter                  |

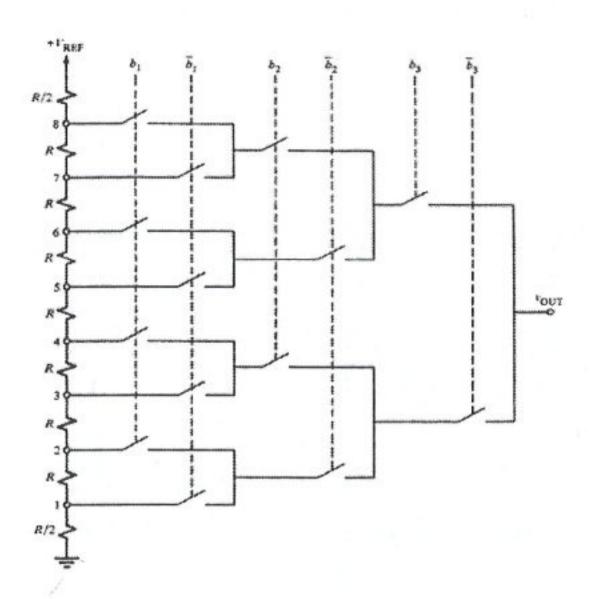

| 6.12 | Implementation of a 3-bit voltage scaling D/A converter                           |

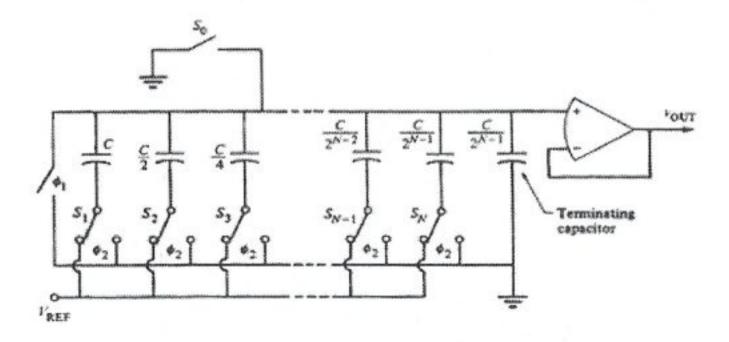

| 6.13 | N-bit charge-scaling D/A converter schematic                                      |

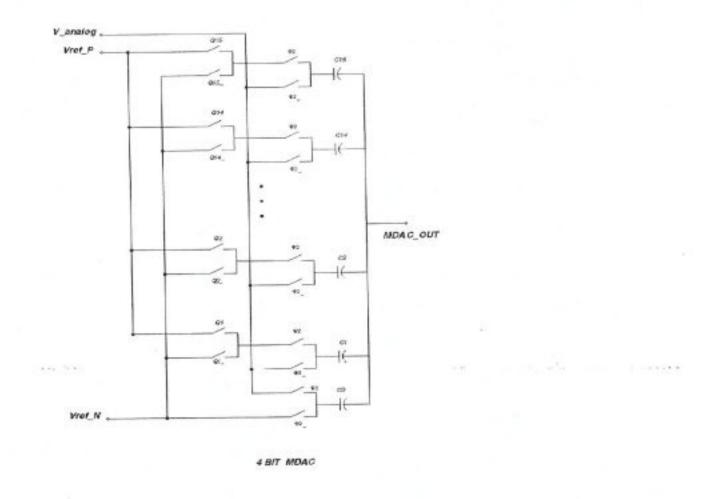

| 6.14 | Schematic view of a 4-bit MDAC                                                    |

| 6.15 | Simplified cross-section representation of metal-metal capacitors constructed     |

|      | in N-well. Note that N-well is not shown in figure for simplicity                 |

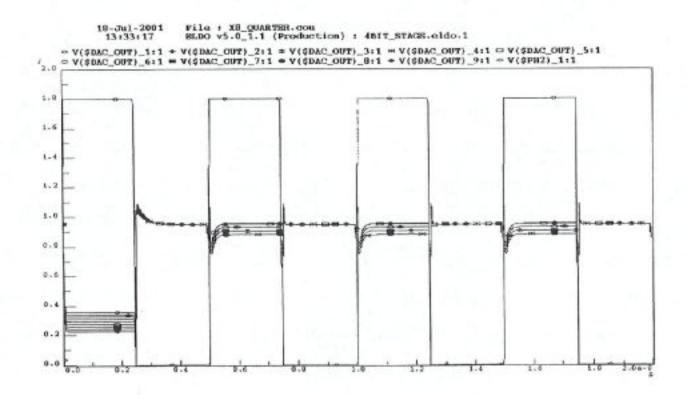

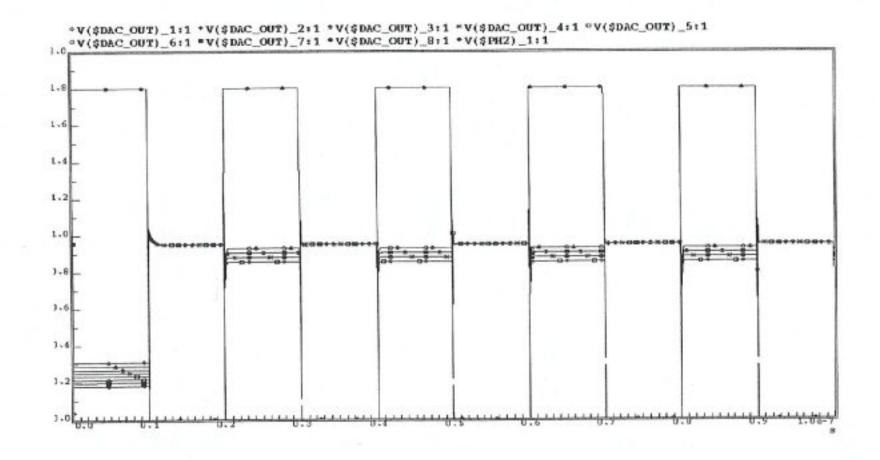

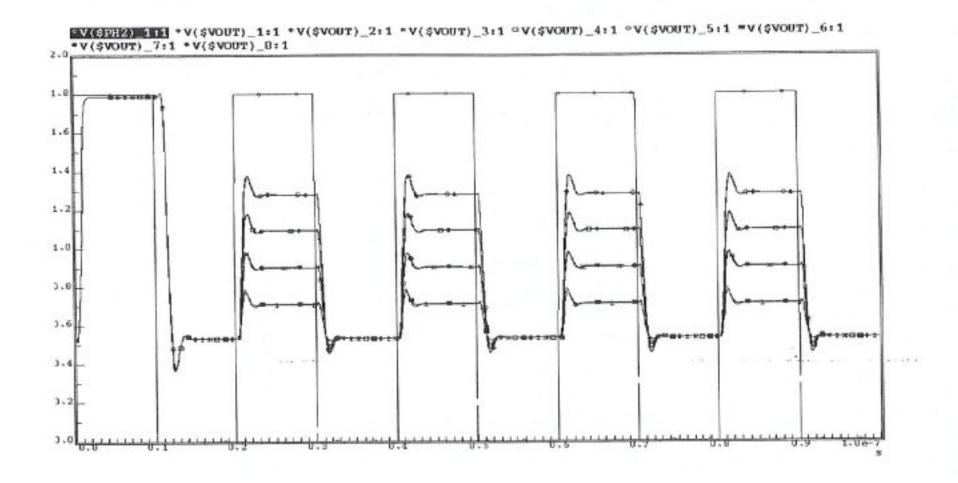

| 6.16 | Residue voltages obtained for different input voltage levels applied to the       |

|      | input of the 4-bit pipeline stage. The sampling clock frequency                   |

|      | is 200 MHz                                                                        |

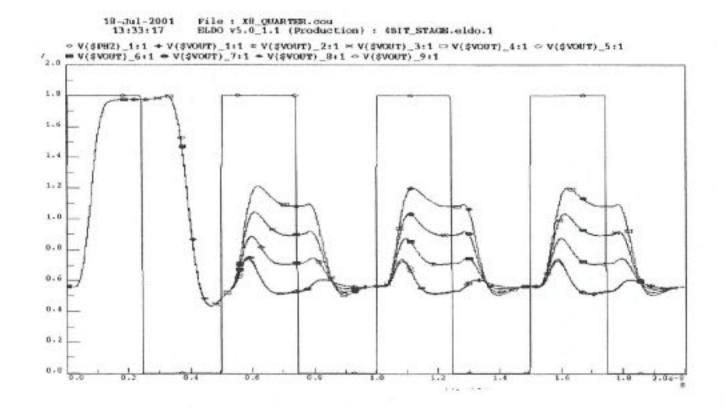

| 6.17 | Time-dependent variation of the amplified residue voltage, with a sampling        |

|      | clock frequency of 200 MHz                                                        |

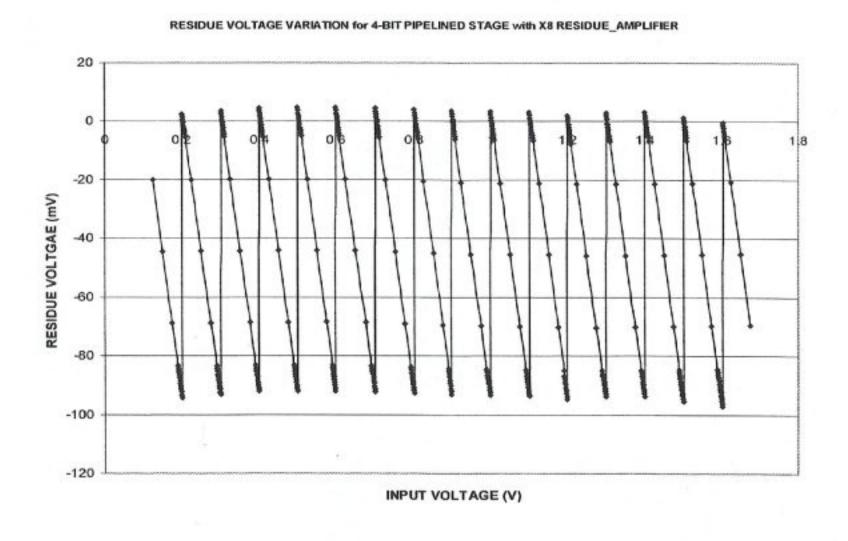

| 6.18 | Residue voltage obtained versus input voltage for typical simulation              |

|      | corner at 200 MHz sampling rate                                                   |

| 6.19 | Variation of the amplified residue voltage given Figure 6.19 as a function of the |

|      | input voltage level, with X8 amplification factor                                 |

| 6.20 | Residue voltage obtained for different input voltage levels applied to the        |

|      | input of the 4-bit pipeline stage. The sampling clock frequency                   |

|      | is 50 MHz                                                                         |

| 6.21 | Time-dependent variation of the amplified residue voltage, with a sampling        |

|      | clock frequency of 50 MHz                                                         |

| 6.22 | Simplified schematic view of a 4-bit encoder block used in stage 1 160            |

| 6.23 | 1-Bit-overlapping technique that is used in the design of the pipeline            |

|      | stages                                                                            |

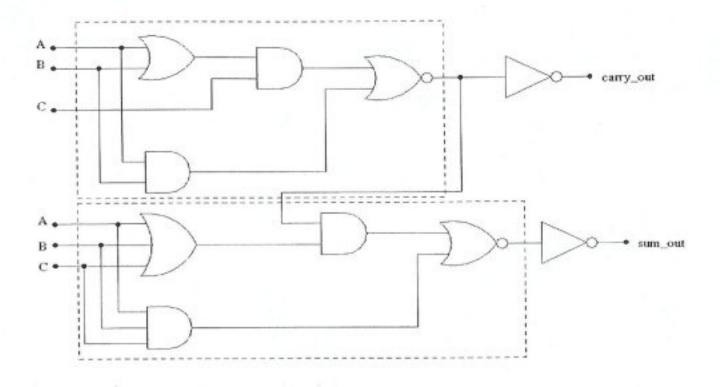

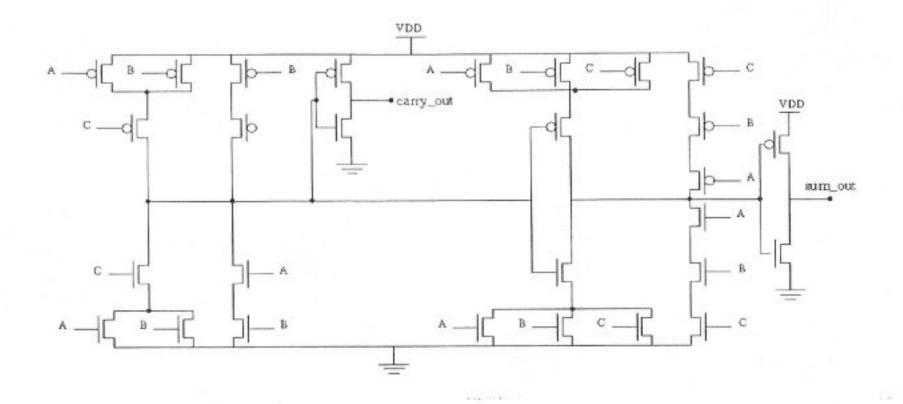

| 7.1  | Gate level schematic of the one-bit full-adder circuit                            |

|------|-----------------------------------------------------------------------------------|

| 7.2  | Completely symmetric 1-bit full adder cell                                        |

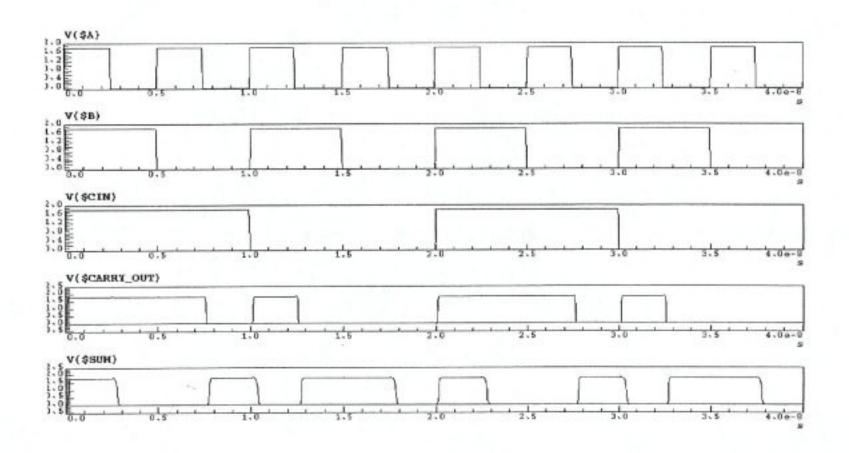

| 7.3  | Simulated input and output waveforms of 1-bit full adder circuit                  |

| 7.4  | Block diagram of a carry ripple adder chain consisting of n 1-bit                 |

|      | full adders                                                                       |

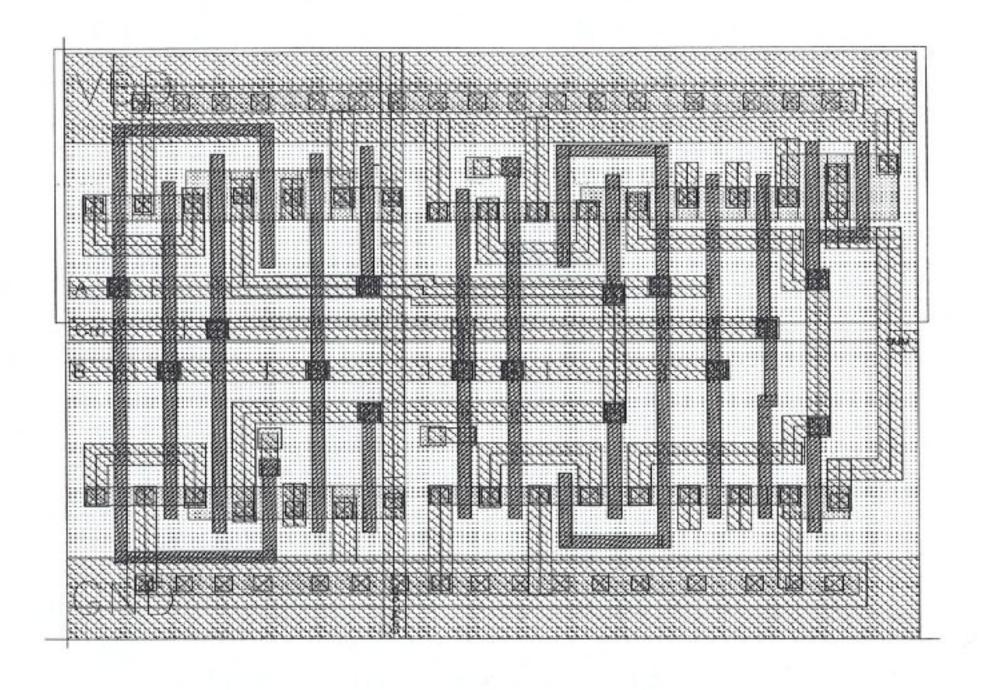

| 7.5  | Layout view of the designed 1-bit full adder circuit                              |

| 7.6  | CMOS implementation of the D-latch circuit                                        |