# Design and Simulation of Micro Resonator Oscillator for Communication Circuits

by Mustafa Parlak

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabanci University Spring 2003

| Design and Simulation of Micro Resonator Oscil    | lator for Communication Circuits |

|---------------------------------------------------|----------------------------------|

| APPROVED BY                                       |                                  |

| Assoc. Prof. Dr. Yasar GURBUZ (Thesis Supervisor) |                                  |

| Assist. Prof. Dr. Ayhan BOZKURT                   |                                  |

| Assist. Prof. Dr. Mehmet KESKINOZ                 |                                  |

| DATE OF APPROVAL:                                 |                                  |

©Mustafa Parlak 2003 All Rights Reserved

### Acknowledgments

First of all, I would like to thank my thesis advisor Yasar Gurbuz for his support and encouragement. The other jury members, including Ayhan Bozkurt and Mehmet Keskinoz, which provided helpful feedback on the thesis are thanked as well.

Thanks to my dearest friends during the masters including Nurullah Beyter and Ibrahim Ulusoy.

The guys who helped me in the thesis and kept me company throughout two years of study including Mansoor Naseer, Alisher Kholmatov, Mazhar Adli, Mustafa Coban, Mehmet Ozdemir, Ercument Zorlu, Murat Erman, Durdu Guney, Erdem Bala, Volkan Vural, Ercan bey and Veysi bey are thanked. I wish best of luck for their future.

Our laboratory assistant Bulent Koroglu has to be thanked for his limitless help until the last minute. I must include the names my respected friends Thomas Bechteler and Mustafa Unel, who instructed and helped me and never made me feel our student–teacher relationship.

My most beloved family; my father and mother, who supported me through the effort and lived a tough life for safe and better upbringing of their children. My elder brothers who always encouraged and guided me, and my younger sisters, who were always with me. I thank you all for being there when I needed you.

## Design and Simulation of Micro Resonator Oscillator for Communication Circuits

#### Abstract

In this theses design and simulation of a Micro Electro Mechanical System (MEMS) based oscillator is presented. Electrostatic comb drive is chosen as the core structure in oscillator. MicroElectroMechanical (MEM) vibrating structures such as linear drive resonators can be used as driving components in signal processing applica-The choice of these components is assisted by the fact that these MEM devices display high quality factor values when operated under vacuum. The design of a highly stable oscillator is an example utilizing the linear drive resonators and working samples are demonstrated at 16.5 kHz. For this oscillator to be used in portable communication devices, the operating frequency will have to be increased to at least IF band (> 450kHz). MEMS based microstructures are simulated and prepared for implementation by properly adjusting the physical dimensions of the micromechanical resonator. The Dimensions of the resonator is tuned to achieve higher resonance frequencies. Electrical model and governing equations of interdigitated finger structure are studied. Based on results of these studies a micromechanical oscillator is designed to attain above-mentioned frequency. The study is carried out both analytically and on the equivalent circuit.

Integration of MEMS structure with Complementary Metal Oxide Semiconductor (CMOS) electronics is another motivation and driving force of this study. Therefore completely monolithic high-Q micromechanical oscillator integrated with CMOS circuits is aimed and described. As it has high Q (over 80.000) and very stable, laterally driven microresonators can be a good miniaturized replacement of a crystal and surface acoustic wave (SAW) resonator based oscillators used in telecommunication applications. The electrical model of the microresonator is given and used as a frequency selective network in the oscillator design. Different oscillator circuits are designed and simulated to estimate and compare their performance to other mechanical based oscillators (SAW, FBAR, Crystal etc.). Analog CMOS integraated circuits are designed and optimized to achieve highly stable oscillations.

## Haberleşme Devreleri için Mikro Rezonatör Osilatörlerin Tasarımı ve Simülasyonu

### Özet

Bu tez MikroelektroMekanik sistem (MEMS) bazlı osilatörün tasarımını ve simlasyonunu sunar. Elektrostatik olarak etkileşebilen tarak benzeri (Mikro Rezonatör) bir MEMS yapısı osilatörün yapı taşı olarak kullanıldı. Bu tezin konusu olan mikro rezonatör gibi MEMS bazlı titreşen yapılar işaret işleme uygulamalarında kullanılabilecek aletlerdir. Osilatör yapımında Mikro Rezonatörün kullanılmasının seçimi MEMS bazlı yapıların havasız ortamda yüksek kalite faktörüne (Yüksek-Q) sahip olmasından kaynaklanmaktadır. Yüksek kararlı osilatörler Mikro Rezonatörler kullanılarak yapılabilmekte ve 16 kHz'de çalışan örnekleri gösterilmiştir. Fakat bu osilatörlerin taşınabilir haberleşme devrelerinde kullanılabilmesi için çalışma frekansının en azından IF bandına (> 455 kHz) çıkartılması gerekmektedir. Bu tezde MEMS bazlı osilatörlerin simulasyonu yapıldı ve fiziksel boyutlarında yapılan uygun değişikliklerle istenilen frekans aralığında çalışması sağlandı. Mikro Rezonatörün elektriksel eşdeğer devreleri ve belirleyici matematiksel denklemleri incelendi. Elde edilen bu sonuçlar kullanılarak MEMS bazlı, 500 kHz'de çalışan bir osilatör tasarlandı. Bu calişmalar hem Mikro Rezonatörün eşdeğer devresi hem de matematiksel denklemleri kullanılarak yapıldı.

Bu çalışmanın yapılmasındaki diğer bir amaç MEMS yapılarının kolaylıkla CMOS elektronik devreleriyle entegre olabilme özelliğidir. Dolayısıyla tamamıyla aynı çip üzerinde gerçeklenmiş MEMS tabanlı osilatörler amaç olarak seçilmiştir. Yüksek kalite faktörüne sahip olan MEMS yapıları şu anda haberleşme devrelerinde kullanılan kristal ve yüzey akustik dalga (SAW) rezonatörlerinin yerine kullanabilecek bir kapasiteye sahiptir. Bu tezde Mikro Rezonatörün elektriksel modeli osilatörde frekans belirleyici devre olarak kullanıldı. Değişik osilatörler dizayn edildi ve rezonatör performansları diğer mekanik (SAW, kristal) rezonatörlerle karşılaştırıldı. Osilatör devresi gerçeklenirken daha karalı salınım sağlayabilmesi için çeşitli CMOS analog devreleri tasarlandı ve optimize edildi.

## **Table of Contents**

|          | Ack | nowled  | lgments                                                      | iv           |

|----------|-----|---------|--------------------------------------------------------------|--------------|

|          | Abs | stract  |                                                              | $\mathbf{v}$ |

|          | Öz  | et      |                                                              | vi           |

| 1        | Int | roduc   | tion                                                         | 1            |

| _        | 1.1 |         | tant Resonator Properties                                    |              |

|          | 1.2 |         | of-the-art Resonators                                        |              |

| <b>2</b> | De  |         | of MEMS resonator and its fabrication                        | 6            |

|          | 2.1 | Transf  | er Function                                                  | . 8          |

|          | 2.2 | Mecha   | nical Analysis                                               | . 10         |

|          |     | 2.2.1   | Lateral Resonant Frequency                                   |              |

|          |     | 2.2.2   | Quality Factor                                               | . 11         |

|          | 2.3 |         | Resonator Fabrication                                        |              |

|          | 2.4 | Small   | Signal Equivalent Circuits for Micromechanical Resonators .  | . 12         |

|          | 2.5 | Summ    | ary                                                          | . 13         |

| 3        | De  | sign o  | f CMOS Analog Integrated Circuits for MEMS                   | $\mathbf{S}$ |

|          | Ose | cillato | $\mathbf{r}$                                                 | 17           |

|          | 3.1 | Two S   | tage CMOS Op-amp                                             | . 17         |

|          |     | 3.1.1   | The Frequency Response, Compensation                         |              |

|          |     | 3.1.2   | Open Circuit Voltage Gain                                    |              |

|          |     | 3.1.3   | DC Offsets, DC Biasing                                       |              |

|          |     | 3.1.4   | Slew Rate                                                    | . 25         |

|          |     | 3.1.5   | Power Dissipation                                            |              |

|          |     | 3.1.6   | Noise Performance                                            | . 27         |

|          |     | 3.1.7   | DC Power Supply Rejection                                    | . 28         |

|          |     | 3.1.8   | Output Stage                                                 | . 31         |

|          |     | 3.1.9   | Linearity                                                    |              |

|          |     | 3.1.10  | Phase Margin                                                 |              |

|          |     | 3.1.11  | Two Stage Op-Amp Design and Simulation                       | . 35         |

|          | 3.2 | Design  | and small signal analysis of a two-stage folded-cascode CMOS |              |

|          |     | Opera   | tional Amplifier                                             | . 36         |

| 4            | Osc | cillator                                                        | 42 |

|--------------|-----|-----------------------------------------------------------------|----|

|              | 4.1 | General Consideration                                           | 43 |

|              | 4.2 | LC Oscillators                                                  | 44 |

|              | 4.3 | Bandwidth and Quality Factor                                    | 45 |

|              |     | 4.3.1 The Frequency Response versus the Natural Response of the |    |

|              |     | Parallel RLC Circuit                                            |    |

|              | 4.4 | Series Resonance                                                | 48 |

|              | 4.5 | Analysis of a Practical Parallel Resonant Circuit               | 49 |

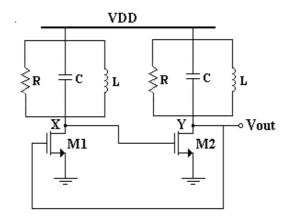

|              | 4.6 | Parallel Crossed-Coupled Oscillator                             |    |

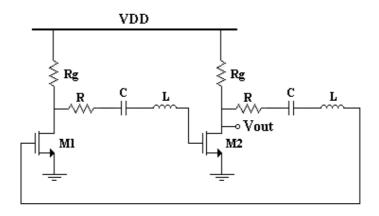

|              | 4.7 | Series Crossed-Coupled Oscillator                               |    |

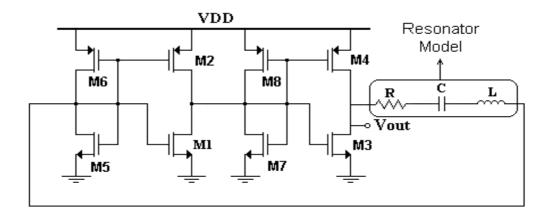

|              | 4.8 | Microelectromechanical Resonator Oscillator Design              |    |

|              | 4.9 | Phase Noise in Oscillators                                      | 56 |

| 5            | Co  | nclusions                                                       | 64 |

|              | App | pendix                                                          | 66 |

| $\mathbf{A}$ | Lay | routs                                                           | 66 |

| В            | Opa | amp characteristics                                             | 69 |

|              | Bib | liography                                                       | 74 |

# List of Figures

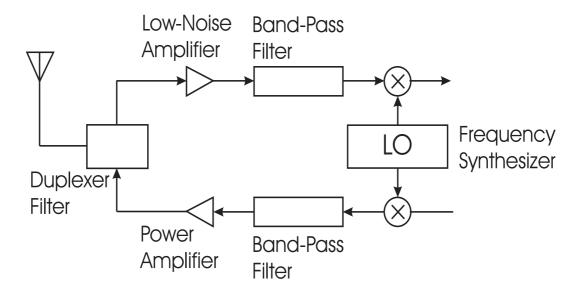

| 1.1  | Block diagram of a heterodyne receiver used in cellular phones and              |    |

|------|---------------------------------------------------------------------------------|----|

|      | mobile communication systems                                                    | 3  |

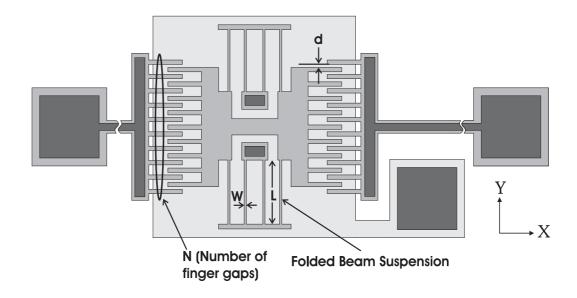

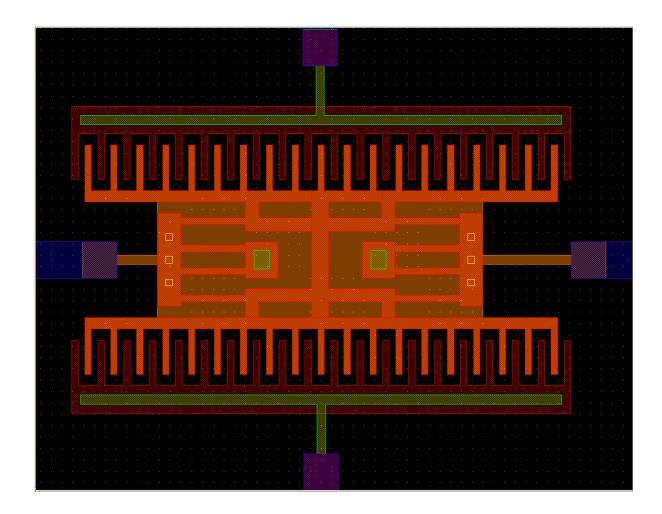

| 2.1  | Layout of a linear lateral resonator                                            | 7  |

| 2.2  | Electric Field distribution before and after the movable finger dis-            |    |

|      | places by $\Delta x$ into the slot                                              | 8  |

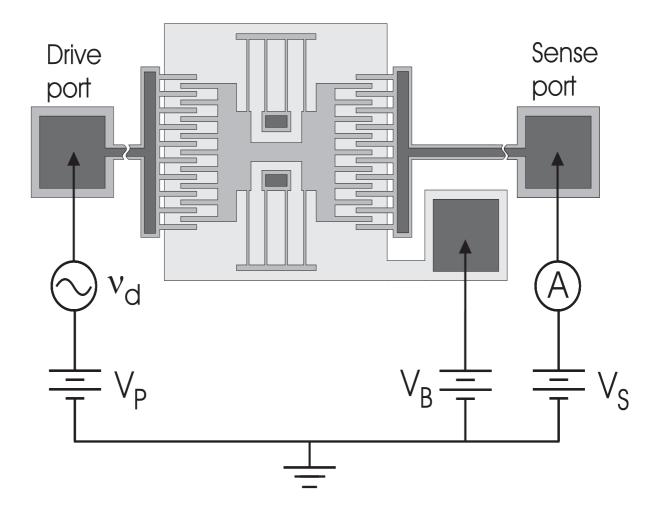

| 2.3  | A linear resonator electrostatically driven from one side and sensed            |    |

|      | capacitively at the other side                                                  | 6  |

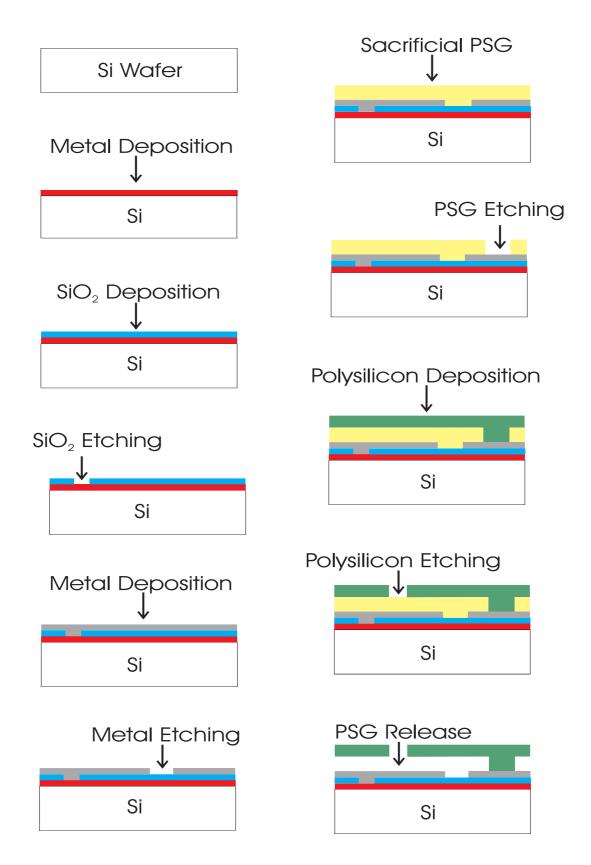

| 2.4  | Process Sequence of the Micro resonator                                         | 15 |

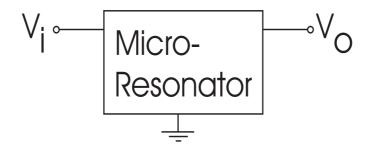

| 2.5  | Block representation of the microresonator                                      | 16 |

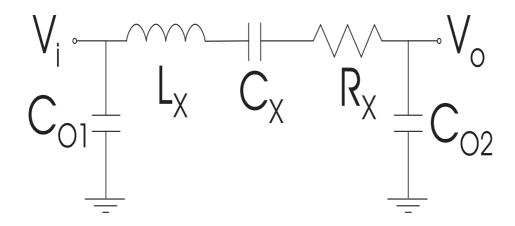

| 2.6  | Equivalent circuit model of the microresonator                                  | 16 |

| 2.7  | Critical Dimensions of a comb drive                                             | 16 |

| 3.1  | Simplified basic two stage Op-amp                                               | 18 |

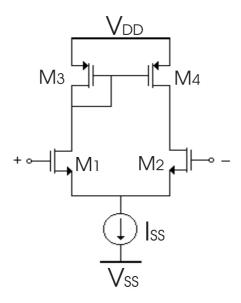

| 3.2  | MOS differential pair                                                           | 19 |

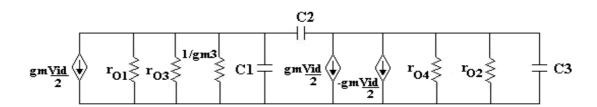

| 3.3  | The simplified equivalent model of differential pair                            | 19 |

| 3.4  | Simplified small signal model of the basic two stage Op-amp added               |    |

|      | with the nulling resistor                                                       | 21 |

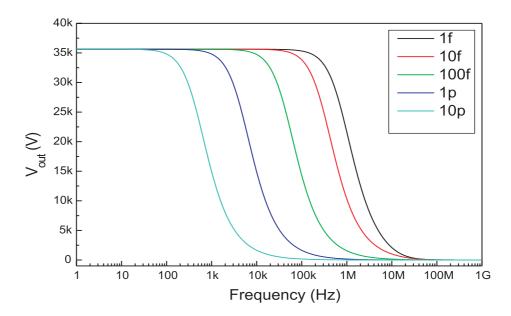

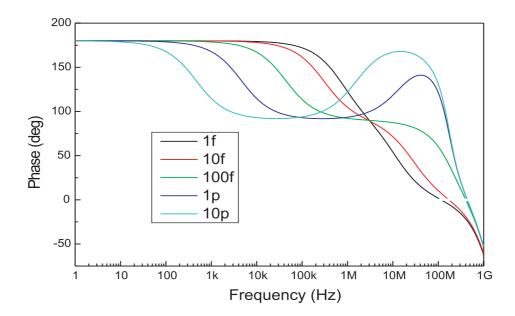

| 3.5  | AC Frequency Simulation of the Op-Amp. DC gain of this Op-Amp                   |    |

|      | is more than 6000 V/V                                                           | 23 |

| 3.6  | AC Frequency Response in terms of dB. DC gain is 75 dB                          | 24 |

| 3.7  | Simplified small signal model of the basic two stage Op-amp $\ \ldots \ \ldots$ | 24 |

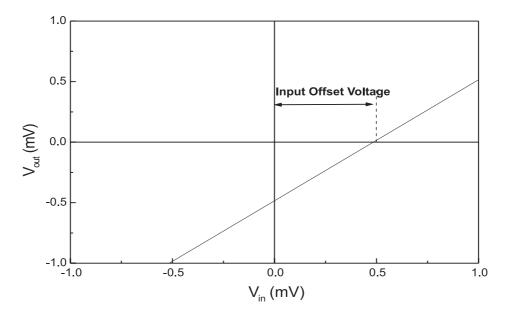

| 3.8  | Simulation results showing the Input Offset voltage (484.6 $\mu V$ in this      |    |

|      | circuit)                                                                        | 25 |

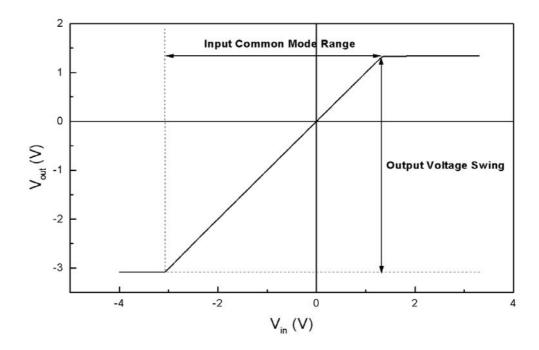

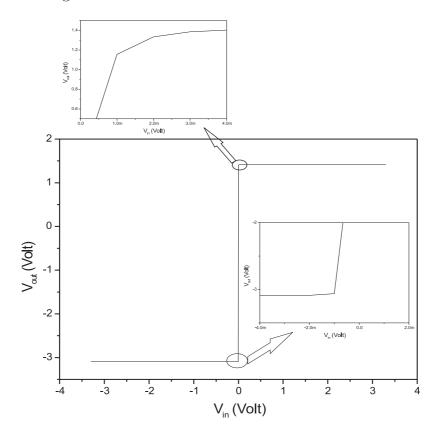

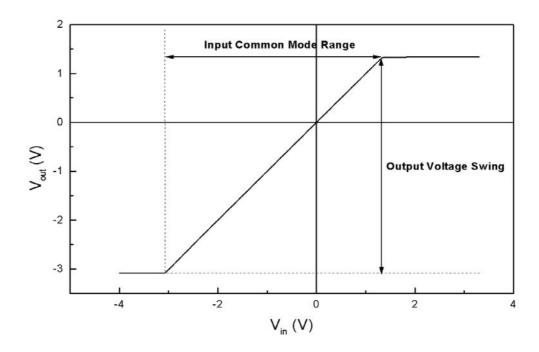

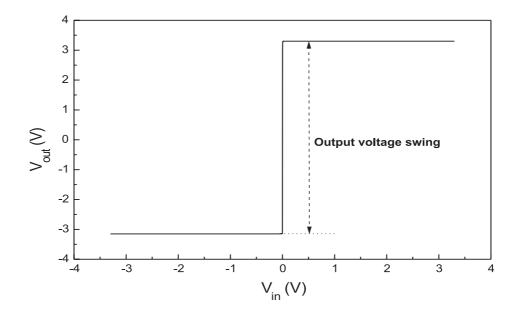

| 3.9  | Simulation results showing the ICMR and output swing                            | 26 |

| 3.10 | Circuit for testing slew-rate performance                                       | 27 |

| 3.11 | Simplified schematic of a two-stage MOS op-amp for slew rate calculations           | 28  |

|------|-------------------------------------------------------------------------------------|-----|

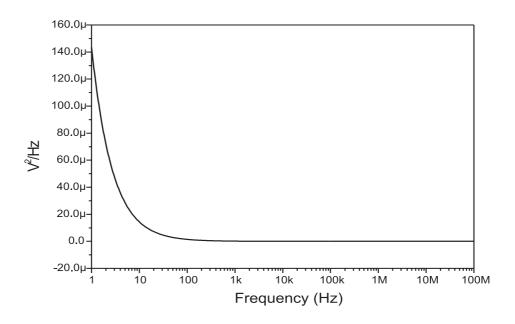

| 3.12 | Output noise spectrum of the two stage op-amp                                       | 29  |

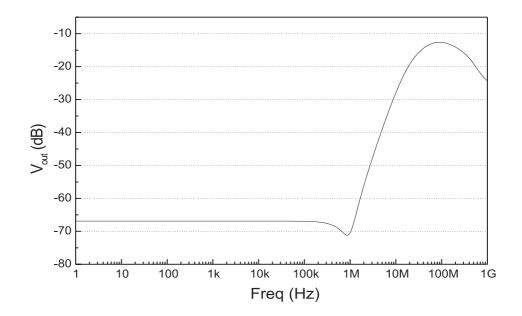

|      | Simulation results showing the PSRR- for the circuit shown in Figure                | -0  |

| 0.10 | 3.22                                                                                | 30  |

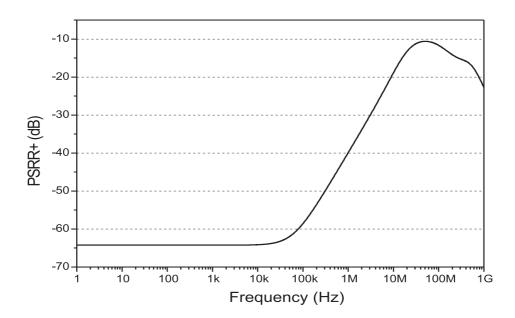

| 3.14 | Simulation results showing the PSRR+ for the circuit shown in Figure                | 00  |

| 3.11 | 3.22                                                                                | 30  |

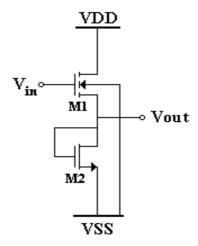

| 3.15 | Common-drain (Source-follower) output amplifier                                     | 31  |

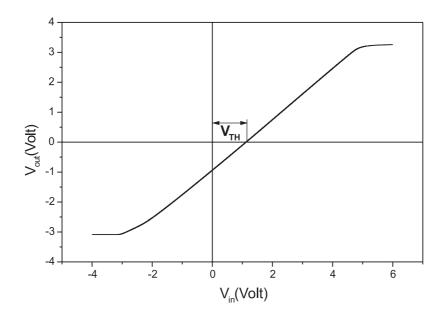

|      | Transfer characteristics of the ClassA output stage                                 | 32  |

|      | Linearity of basic two stage op-amp                                                 | 33  |

|      | Linearity of the two stage op-amp with employing negative feedback.                 | 34  |

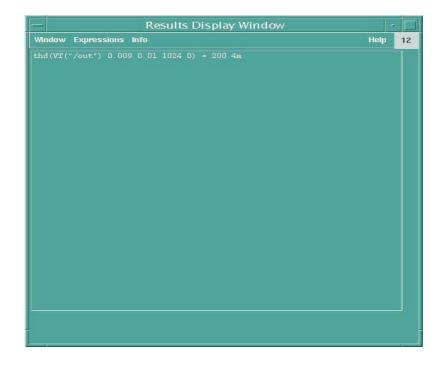

|      | THD of the basic op-amp                                                             | 35  |

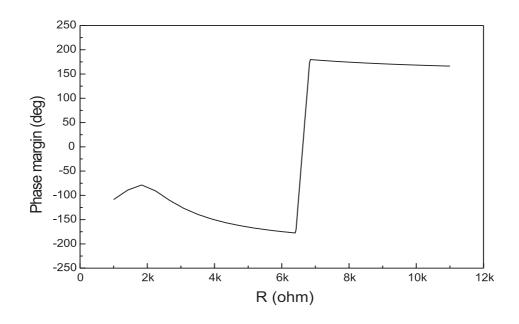

|      | Phase margin versus nulling resistor R                                              | 36  |

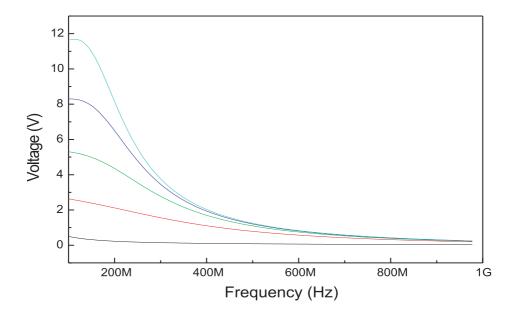

|      | Effect of R on op-amp bandwidth                                                     | 37  |

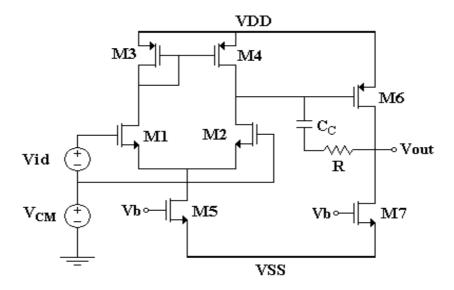

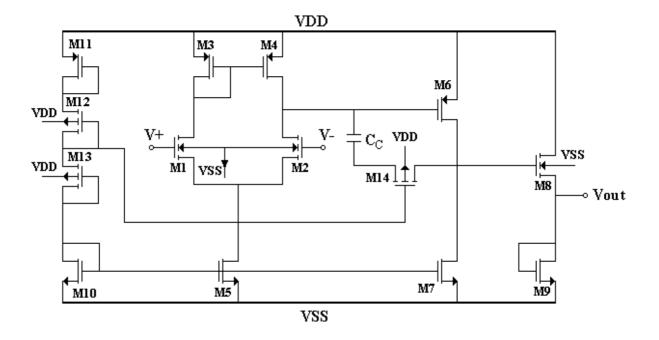

|      | Complete schematic of the two stage Op-amp                                          | 38  |

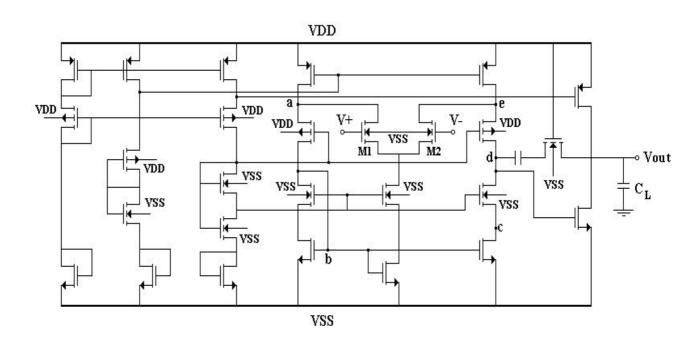

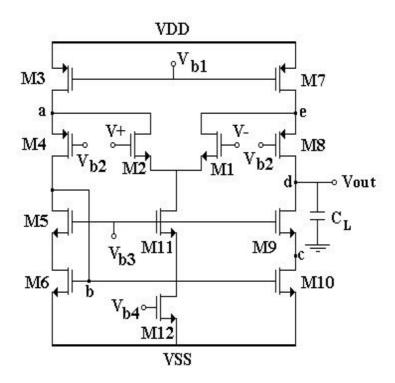

|      | Two-stage folded-cascode                                                            | 39  |

| 3.24 | One-stage single-ended folded-cascode CMOS operational amplifier .                  | 41  |

| 3.25 | A complete small signal model for the op-amp of Figure 3.2. Node                    |     |

|      | voltages $V_a - V_e$ refer to nodes a-e in Figure 3.24, and $V_{out}$ is associated |     |

|      | with node d                                                                         | 41  |

| 1 1  |                                                                                     | 4.4 |

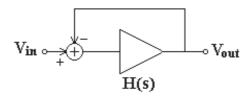

| 4.1  | Basic structures of a feedback system                                               | 44  |

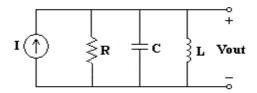

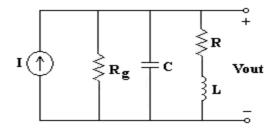

| 4.2  | The parallel-resonant circuit                                                       | 44  |

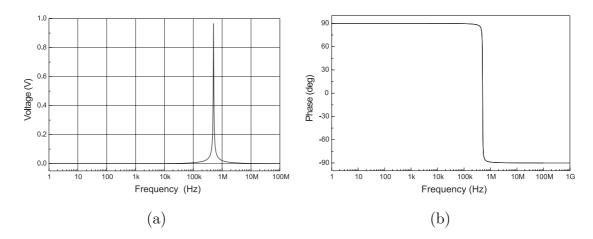

| 4.3  | (a) Amplitude and (b) phase versus frequency for the circuit of Fig-                | 15  |

| 4 4  | ure 4.2                                                                             |     |

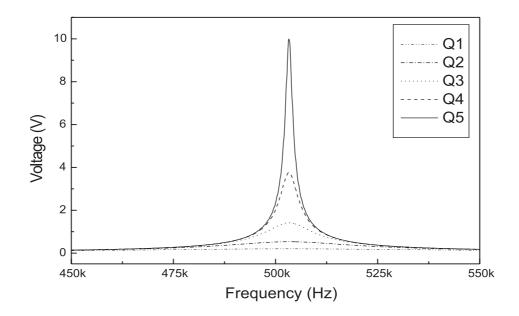

| 4.4  | Effect of Q on resonant circuit magnitude response $(Q5 \ge Q1)$                    |     |

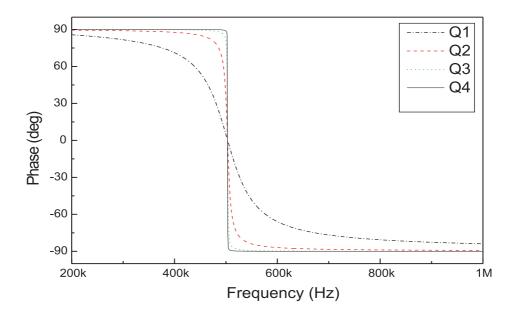

| 4.5  | Effect of Q on resonant circuit phase response $(Q4 \ge Q1)$                        |     |

| 4.6  | Series-resonant circuit                                                             |     |

| 4.7  | A parallel-resonant circuit containing a low loss inductor                          |     |

| 4.8  | Two tuned stages placed in a feedback loop                                          |     |

| 4.9  | Series cross-coupled oscillator                                                     |     |

| 4.10 | Complete circuit for the oscillator shown in Figure 4.9                             |     |

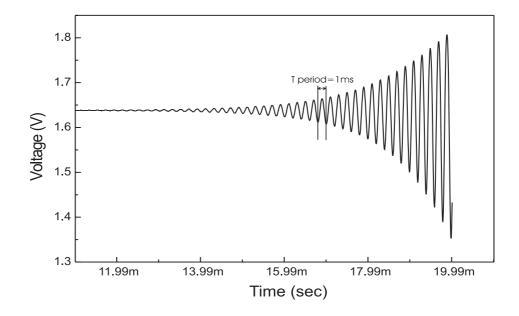

| 111  | Oscillation at 5 KHz                                                                | 52  |

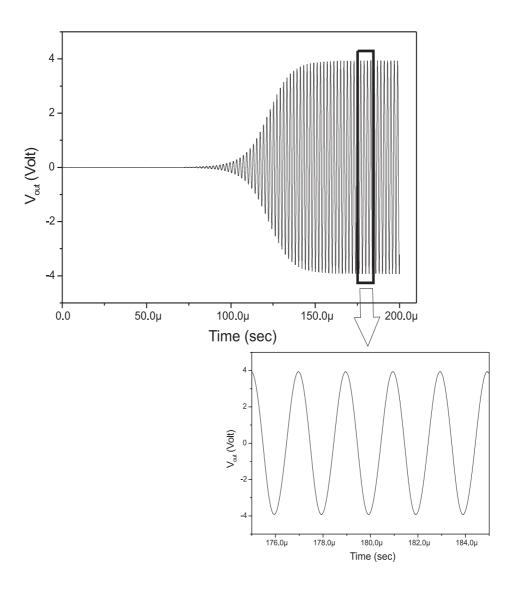

| 4.12 | Oscillation at 500 KHz                                                      | 53 |

|------|-----------------------------------------------------------------------------|----|

| 4.13 | Equivalent circuit for a two-port capacitively transduced resonator.        |    |

|      | It is basically a series resonant circuit                                   | 54 |

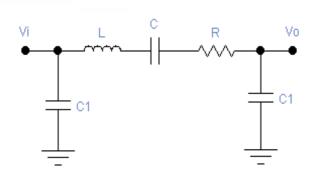

| 4.14 | Schematic example of parallel resonant oscillator architecture              | 54 |

| 4.15 | Schematic example of series resonant oscillator architecture                | 55 |

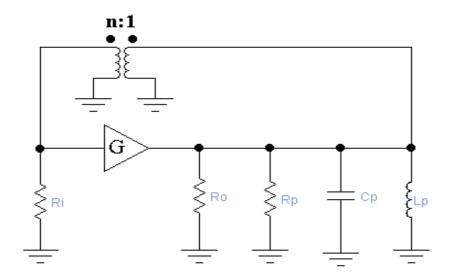

| 4.16 | System level schematic showing the basic series resonant architecture       |    |

|      | used for the CMOS micromechanical reso nator oscillator of this work.       | 56 |

| 4.17 | System level schematic using op-amp as a sustaining amplifier               | 57 |

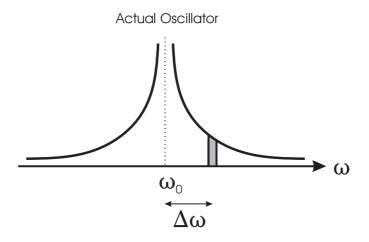

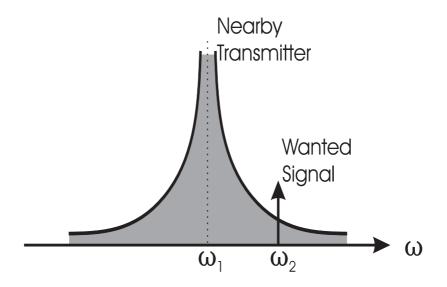

| 4.18 | Spectrum of an ideal and actual oscillator showing phase noise in           |    |

|      | oscillators                                                                 | 58 |

| 4.19 | Generic wireless transceiver                                                | 59 |

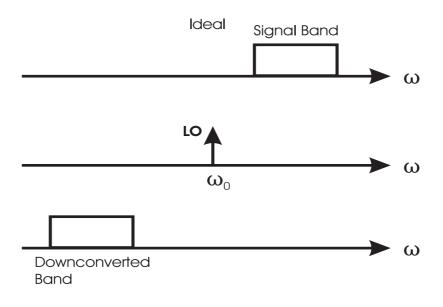

| 4.20 | Effect of phase noise on receive path                                       | 61 |

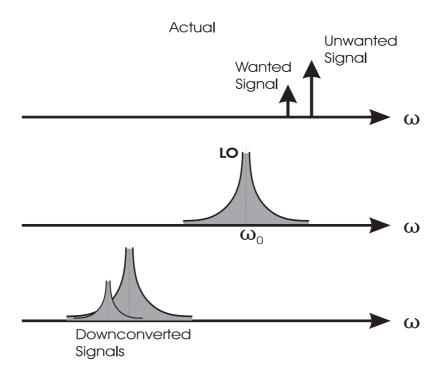

| 4.21 | Effect of phase noise on transmit path                                      | 62 |

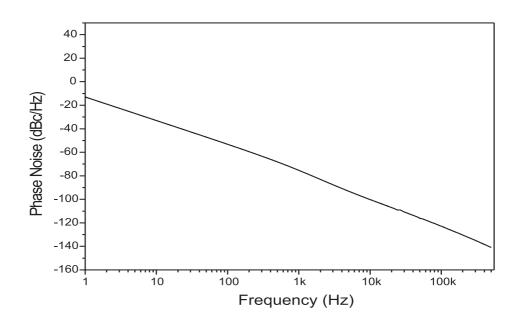

| 4.22 | Phase noise for the circuit shown in Figure 4.7                             | 62 |

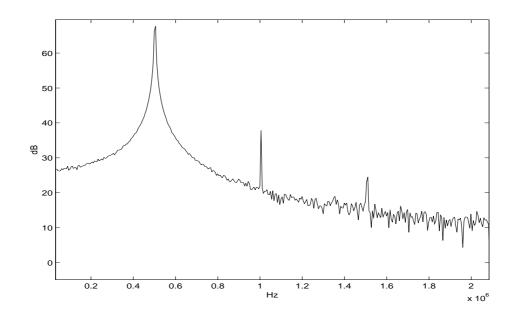

| 4.23 | Power spectrum of the oscillator output operating at 500 kHz $$             | 63 |

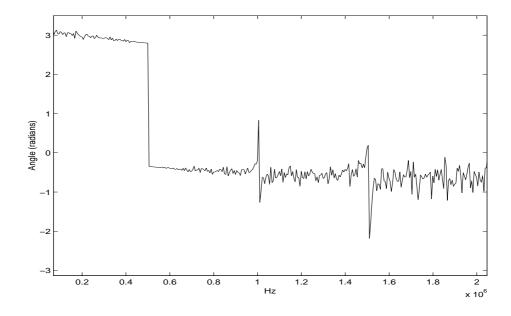

| 4.24 | Angle spectrum of the oscillator output operating at 500 kHz                | 63 |

| A.1  | Mask layout of the electrostatic comb drive                                 | 66 |

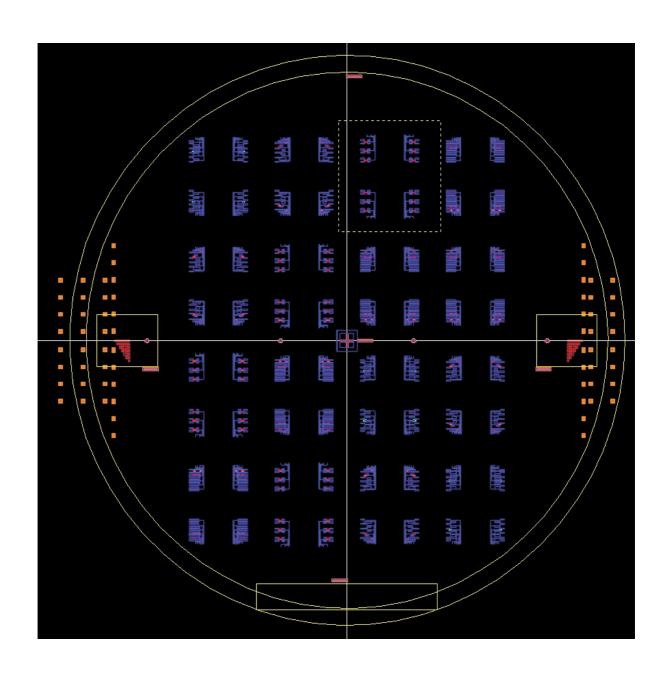

| A.2  | Complete Mask layout of the electrostatic comb drives and Filters $$ . $$ . | 67 |

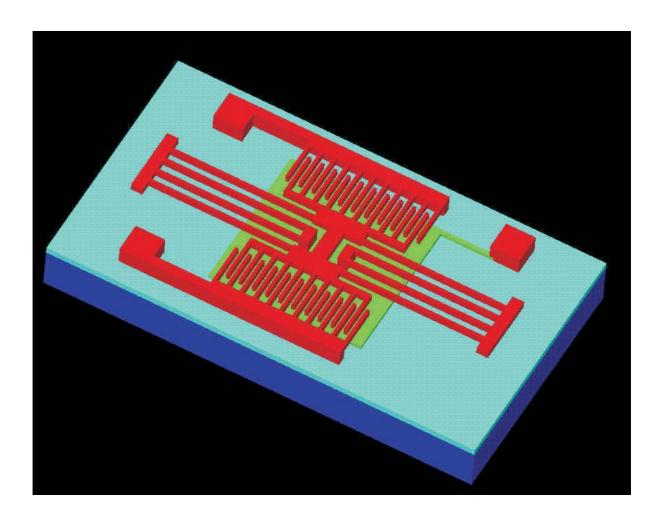

| A.3  | 3-D view of the electrostatic comb resonator. 3-D view is produced          |    |

|      | by MEMCAD®                                                                  | 68 |

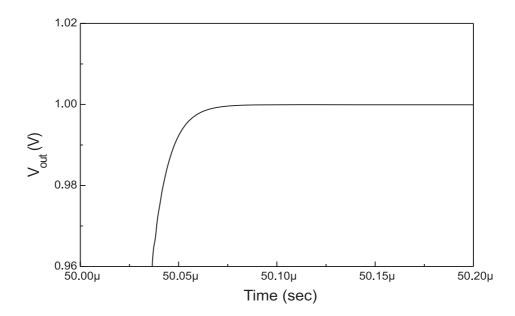

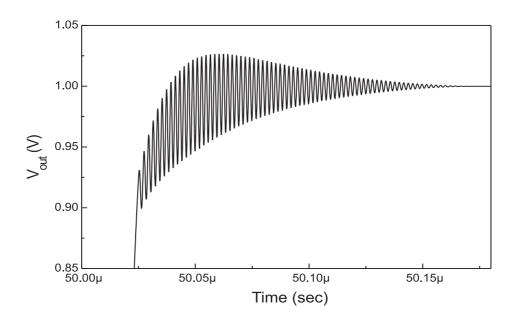

| B.1  | Settling for $R=4k\Omega$ phase margin = 29.7                               | 69 |

| B.2  | Settling for R=7k $\Omega$ phase margin =179                                | 70 |

| В.3  | Output voltage swing of the folded cascode op-amp                           | 70 |

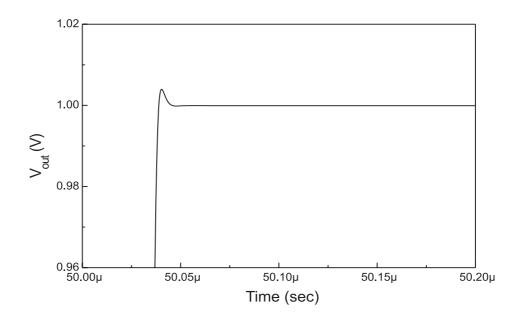

| B.4  | Settling for R=1k $\Omega$ phase margin = 72                                | 71 |

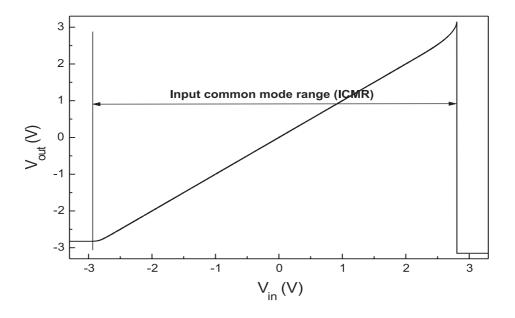

| B.5  | Input Common Mode Range                                                     | 71 |

| B.6  | Effect of compensation C on magnitude response of the folded cascode        |    |

|      | opamp                                                                       | 72 |

| B.7  | Effect of compensation capacitor on the phase response of the folded        |    |

|      | cascode op-amp                                                              | 72 |

| B.8  | Negative power supply rejection ratio PSRR                                  | 73 |

| B.9  | Positive power supply rejection ratio PSRR+                                 | 73 |

# List of Tables

| 1.1 | Comparison of some of the resonator technologies                    | 5  |

|-----|---------------------------------------------------------------------|----|

| 2.1 | Critical dimensions of 459 kHz microresonator used in the design of |    |

|     | oscillator                                                          | 14 |

| 3.1 | Nulling Resistor effect on Bandwidth and Phase Margin               | 35 |

| 3.2 | Overall Op-Amp Characteristics                                      | 39 |

| 3.3 | Critical values of the transistors in the op-amp                    | 40 |

# Design and Simulation of Micro Resonator Oscillator for Communication Circuits

by Mustafa Parlak

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabanci University Spring 2003

| Design and Simulation of Micro Resonator Oscil    | lator for Communication Circuits |

|---------------------------------------------------|----------------------------------|

| APPROVED BY                                       |                                  |

| Assoc. Prof. Dr. Yasar GURBUZ (Thesis Supervisor) |                                  |

| Assist. Prof. Dr. Ayhan BOZKURT                   |                                  |

| Assist. Prof. Dr. Mehmet KESKINOZ                 |                                  |

| DATE OF APPROVAL:                                 |                                  |

©Mustafa Parlak 2003 All Rights Reserved

### Acknowledgments

First of all, I would like to thank my thesis advisor Yasar Gurbuz for his support and encouragement. The other jury members, including Ayhan Bozkurt and Mehmet Keskinoz, which provided helpful feedback on the thesis are thanked as well.

Thanks to my dearest friends during the masters including Nurullah Beyter and Ibrahim Ulusoy.

The guys who helped me in the thesis and kept me company throughout two years of study including Mansoor Naseer, Alisher Kholmatov, Mazhar Adli, Mustafa Coban, Mehmet Ozdemir, Ercument Zorlu, Murat Erman, Durdu Guney, Erdem Bala, Volkan Vural, Ercan bey and Veysi bey are thanked. I wish best of luck for their future.

Our laboratory assistant Bulent Koroglu has to be thanked for his limitless help until the last minute. I must include the names my respected friends Thomas Bechteler and Mustafa Unel, who instructed and helped me and never made me feel our student–teacher relationship.

My most beloved family; my father and mother, who supported me through the effort and lived a tough life for safe and better upbringing of their children. My elder brothers who always encouraged and guided me, and my younger sisters, who were always with me. I thank you all for being there when I needed you.

## Design and Simulation of Micro Resonator Oscillator for Communication Circuits

#### Abstract

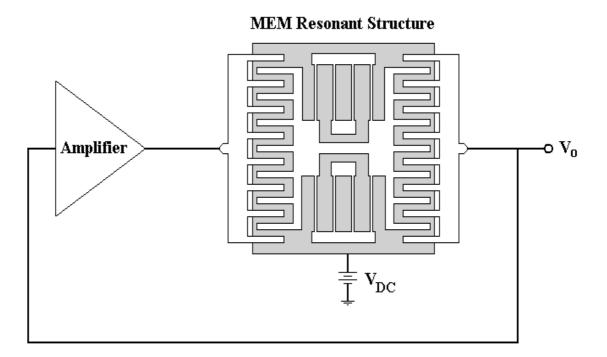

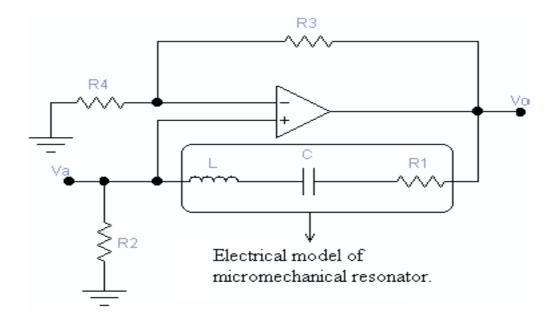

In this theses design and simulation of a Micro Electro Mechanical System (MEMS) based oscillator is presented. Electrostatic comb drive is chosen as the core structure in oscillator. MicroElectroMechanical (MEM) vibrating structures such as linear drive resonators can be used as driving components in signal processing applica-The choice of these components is assisted by the fact that these MEM devices display high quality factor values when operated under vacuum. The design of a highly stable oscillator is an example utilizing the linear drive resonators and working samples are demonstrated at 16.5 kHz. For this oscillator to be used in portable communication devices, the operating frequency will have to be increased to at least IF band (> 450kHz). MEMS based microstructures are simulated and prepared for implementation by properly adjusting the physical dimensions of the micromechanical resonator. The Dimensions of the resonator is tuned to achieve higher resonance frequencies. Electrical model and governing equations of interdigitated finger structure are studied. Based on results of these studies a micromechanical oscillator is designed to attain above-mentioned frequency. The study is carried out both analytically and on the equivalent circuit.

Integration of MEMS structure with Complementary Metal Oxide Semiconductor (CMOS) electronics is another motivation and driving force of this study. Therefore completely monolithic high-Q micromechanical oscillator integrated with CMOS circuits is aimed and described. As it has high Q (over 80.000) and very stable, laterally driven microresonators can be a good miniaturized replacement of a crystal and surface acoustic wave (SAW) resonator based oscillators used in telecommunication applications. The electrical model of the microresonator is given and used as a frequency selective network in the oscillator design. Different oscillator circuits are designed and simulated to estimate and compare their performance to other mechanical based oscillators (SAW, FBAR, Crystal etc.). Analog CMOS integraated circuits are designed and optimized to achieve highly stable oscillations.

## Haberleşme Devreleri için Mikro Rezonatör Osilatörlerin Tasarımı ve Simülasyonu

### Özet

Bu tez MikroelektroMekanik sistem (MEMS) bazlı osilatörün tasarımını ve simlasyonunu sunar. Elektrostatik olarak etkileşebilen tarak benzeri (Mikro Rezonatör) bir MEMS yapısı osilatörün yapı taşı olarak kullanıldı. Bu tezin konusu olan mikro rezonatör gibi MEMS bazlı titreşen yapılar işaret işleme uygulamalarında kullanılabilecek aletlerdir. Osilatör yapımında Mikro Rezonatörün kullanılmasının seçimi MEMS bazlı yapıların havasız ortamda yüksek kalite faktörüne (Yüksek-Q) sahip olmasından kaynaklanmaktadır. Yüksek kararlı osilatörler Mikro Rezonatörler kullanılarak yapılabilmekte ve 16 kHz'de çalışan örnekleri gösterilmiştir. Fakat bu osilatörlerin taşınabilir haberleşme devrelerinde kullanılabilmesi için çalışma frekansının en azından IF bandına (> 455 kHz) çıkartılması gerekmektedir. Bu tezde MEMS bazlı osilatörlerin simulasyonu yapıldı ve fiziksel boyutlarında yapılan uygun değişikliklerle istenilen frekans aralığında çalışması sağlandı. Mikro Rezonatörün elektriksel eşdeğer devreleri ve belirleyici matematiksel denklemleri incelendi. Elde edilen bu sonuçlar kullanılarak MEMS bazlı, 500 kHz'de çalışan bir osilatör tasarlandı. Bu calişmalar hem Mikro Rezonatörün eşdeğer devresi hem de matematiksel denklemleri kullanılarak yapıldı.

Bu çalışmanın yapılmasındaki diğer bir amaç MEMS yapılarının kolaylıkla CMOS elektronik devreleriyle entegre olabilme özelliğidir. Dolayısıyla tamamıyla aynı çip üzerinde gerçeklenmiş MEMS tabanlı osilatörler amaç olarak seçilmiştir. Yüksek kalite faktörüne sahip olan MEMS yapıları şu anda haberleşme devrelerinde kullanılan kristal ve yüzey akustik dalga (SAW) rezonatörlerinin yerine kullanabilecek bir kapasiteye sahiptir. Bu tezde Mikro Rezonatörün elektriksel modeli osilatörde frekans belirleyici devre olarak kullanıldı. Değişik osilatörler dizayn edildi ve rezonatör performansları diğer mekanik (SAW, kristal) rezonatörlerle karşılaştırıldı. Osilatör devresi gerçeklenirken daha karalı salınım sağlayabilmesi için çeşitli CMOS analog devreleri tasarlandı ve optimize edildi.

## **Table of Contents**

|          | Ack | nowled  | lgments                                                      | iv           |

|----------|-----|---------|--------------------------------------------------------------|--------------|

|          | Abs | stract  |                                                              | $\mathbf{v}$ |

|          | Öz  | et      |                                                              | vi           |

| 1        | Int | roduc   | tion                                                         | 1            |

| _        | 1.1 |         | tant Resonator Properties                                    |              |

|          | 1.2 |         | of-the-art Resonators                                        |              |

| <b>2</b> | De  |         | of MEMS resonator and its fabrication                        | 6            |

|          | 2.1 | Transf  | er Function                                                  | . 8          |

|          | 2.2 | Mecha   | nical Analysis                                               | . 10         |

|          |     | 2.2.1   | Lateral Resonant Frequency                                   |              |

|          |     | 2.2.2   | Quality Factor                                               | . 11         |

|          | 2.3 |         | Resonator Fabrication                                        |              |

|          | 2.4 | Small   | Signal Equivalent Circuits for Micromechanical Resonators .  | . 12         |

|          | 2.5 | Summ    | ary                                                          | . 13         |

| 3        | De  | sign o  | f CMOS Analog Integrated Circuits for MEMS                   | $\mathbf{S}$ |

|          | Ose | cillato | $\mathbf{r}$                                                 | 17           |

|          | 3.1 | Two S   | tage CMOS Op-amp                                             | . 17         |

|          |     | 3.1.1   | The Frequency Response, Compensation                         |              |

|          |     | 3.1.2   | Open Circuit Voltage Gain                                    |              |

|          |     | 3.1.3   | DC Offsets, DC Biasing                                       |              |

|          |     | 3.1.4   | Slew Rate                                                    | . 25         |

|          |     | 3.1.5   | Power Dissipation                                            |              |

|          |     | 3.1.6   | Noise Performance                                            | . 27         |

|          |     | 3.1.7   | DC Power Supply Rejection                                    | . 28         |

|          |     | 3.1.8   | Output Stage                                                 | . 31         |

|          |     | 3.1.9   | Linearity                                                    |              |

|          |     | 3.1.10  | Phase Margin                                                 |              |

|          |     | 3.1.11  | Two Stage Op-Amp Design and Simulation                       | . 35         |

|          | 3.2 | Design  | and small signal analysis of a two-stage folded-cascode CMOS |              |

|          |     | Opera   | tional Amplifier                                             | . 36         |

| 4            | Osc | cillator                                                        | 42 |

|--------------|-----|-----------------------------------------------------------------|----|

|              | 4.1 | General Consideration                                           | 43 |

|              | 4.2 | LC Oscillators                                                  | 44 |

|              | 4.3 | Bandwidth and Quality Factor                                    | 45 |

|              |     | 4.3.1 The Frequency Response versus the Natural Response of the |    |

|              |     | Parallel RLC Circuit                                            |    |

|              | 4.4 | Series Resonance                                                | 48 |

|              | 4.5 | Analysis of a Practical Parallel Resonant Circuit               | 49 |

|              | 4.6 | Parallel Crossed-Coupled Oscillator                             |    |

|              | 4.7 | Series Crossed-Coupled Oscillator                               |    |

|              | 4.8 | Microelectromechanical Resonator Oscillator Design              |    |

|              | 4.9 | Phase Noise in Oscillators                                      | 56 |

| 5            | Co  | nclusions                                                       | 64 |

|              | App | pendix                                                          | 66 |

| $\mathbf{A}$ | Lay | routs                                                           | 66 |

| В            | Opa | amp characteristics                                             | 69 |

|              | Bib | liography                                                       | 74 |

# List of Figures

| 1.1  | Block diagram of a heterodyne receiver used in cellular phones and              |    |

|------|---------------------------------------------------------------------------------|----|

|      | mobile communication systems                                                    | 3  |

| 2.1  | Layout of a linear lateral resonator                                            | 7  |

| 2.2  | Electric Field distribution before and after the movable finger dis-            |    |

|      | places by $\Delta x$ into the slot                                              | 8  |

| 2.3  | A linear resonator electrostatically driven from one side and sensed            |    |

|      | capacitively at the other side                                                  | 6  |

| 2.4  | Process Sequence of the Micro resonator                                         | 15 |

| 2.5  | Block representation of the microresonator                                      | 16 |

| 2.6  | Equivalent circuit model of the microresonator                                  | 16 |

| 2.7  | Critical Dimensions of a comb drive                                             | 16 |

| 3.1  | Simplified basic two stage Op-amp                                               | 18 |

| 3.2  | MOS differential pair                                                           | 19 |

| 3.3  | The simplified equivalent model of differential pair                            | 19 |

| 3.4  | Simplified small signal model of the basic two stage Op-amp added               |    |

|      | with the nulling resistor                                                       | 21 |

| 3.5  | AC Frequency Simulation of the Op-Amp. DC gain of this Op-Amp                   |    |

|      | is more than 6000 V/V                                                           | 23 |

| 3.6  | AC Frequency Response in terms of dB. DC gain is 75 dB                          | 24 |

| 3.7  | Simplified small signal model of the basic two stage Op-amp $\ \ldots \ \ldots$ | 24 |

| 3.8  | Simulation results showing the Input Offset voltage (484.6 $\mu V$ in this      |    |

|      | circuit)                                                                        | 25 |

| 3.9  | Simulation results showing the ICMR and output swing                            | 26 |

| 3.10 | Circuit for testing slew-rate performance                                       | 27 |

| 3.11 | Simplified schematic of a two-stage MOS op-amp for slew rate calculations           | 28  |

|------|-------------------------------------------------------------------------------------|-----|

| 3.12 | Output noise spectrum of the two stage op-amp                                       | 29  |

|      | Simulation results showing the PSRR- for the circuit shown in Figure                | -0  |

| 0.10 | 3.22                                                                                | 30  |

| 3.14 | Simulation results showing the PSRR+ for the circuit shown in Figure                | 00  |

| 3.11 | 3.22                                                                                | 30  |

| 3.15 | Common-drain (Source-follower) output amplifier                                     | 31  |

|      | Transfer characteristics of the ClassA output stage                                 | 32  |

|      | Linearity of basic two stage op-amp                                                 | 33  |

|      | Linearity of the two stage op-amp with employing negative feedback.                 | 34  |

|      | THD of the basic op-amp                                                             | 35  |

|      | Phase margin versus nulling resistor R                                              | 36  |

|      | Effect of R on op-amp bandwidth                                                     | 37  |

|      | Complete schematic of the two stage Op-amp                                          | 38  |

|      | Two-stage folded-cascode                                                            | 39  |

| 3.24 | One-stage single-ended folded-cascode CMOS operational amplifier .                  | 41  |

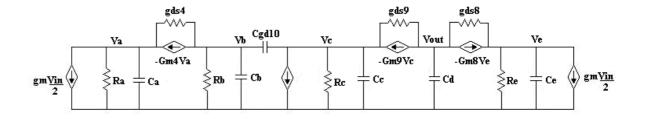

| 3.25 | A complete small signal model for the op-amp of Figure 3.2. Node                    |     |

|      | voltages $V_a - V_e$ refer to nodes a-e in Figure 3.24, and $V_{out}$ is associated |     |

|      | with node d                                                                         | 41  |

| 1 1  |                                                                                     | 4.4 |

| 4.1  | Basic structures of a feedback system                                               | 44  |

| 4.2  | The parallel-resonant circuit                                                       | 44  |

| 4.3  | (a) Amplitude and (b) phase versus frequency for the circuit of Fig-                | 15  |

| 4 4  | ure 4.2                                                                             |     |

| 4.4  | Effect of Q on resonant circuit magnitude response $(Q5 \ge Q1)$                    |     |

| 4.5  | Effect of Q on resonant circuit phase response $(Q4 \ge Q1)$                        |     |

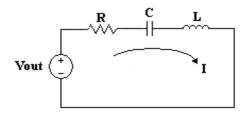

| 4.6  | Series-resonant circuit                                                             |     |

| 4.7  | A parallel-resonant circuit containing a low loss inductor                          |     |

| 4.8  | Two tuned stages placed in a feedback loop                                          |     |

| 4.9  | Series cross-coupled oscillator                                                     |     |

| 4.10 | Complete circuit for the oscillator shown in Figure 4.9                             |     |

| 111  | Oscillation at 5 KHz                                                                | 52  |

| 4.12 | Oscillation at 500 KHz                                                      | 53 |

|------|-----------------------------------------------------------------------------|----|

| 4.13 | Equivalent circuit for a two-port capacitively transduced resonator.        |    |

|      | It is basically a series resonant circuit                                   | 54 |

| 4.14 | Schematic example of parallel resonant oscillator architecture              | 54 |

| 4.15 | Schematic example of series resonant oscillator architecture                | 55 |

| 4.16 | System level schematic showing the basic series resonant architecture       |    |

|      | used for the CMOS micromechanical reso nator oscillator of this work.       | 56 |

| 4.17 | System level schematic using op-amp as a sustaining amplifier               | 57 |

| 4.18 | Spectrum of an ideal and actual oscillator showing phase noise in           |    |

|      | oscillators                                                                 | 58 |

| 4.19 | Generic wireless transceiver                                                | 59 |

| 4.20 | Effect of phase noise on receive path                                       | 61 |

| 4.21 | Effect of phase noise on transmit path                                      | 62 |

| 4.22 | Phase noise for the circuit shown in Figure 4.7                             | 62 |

| 4.23 | Power spectrum of the oscillator output operating at 500 kHz $$             | 63 |

| 4.24 | Angle spectrum of the oscillator output operating at 500 kHz                | 63 |

| A.1  | Mask layout of the electrostatic comb drive                                 | 66 |

| A.2  | Complete Mask layout of the electrostatic comb drives and Filters $$ . $$ . | 67 |

| A.3  | 3-D view of the electrostatic comb resonator. 3-D view is produced          |    |

|      | by MEMCAD®                                                                  | 68 |

| B.1  | Settling for $R=4k\Omega$ phase margin = 29.7                               | 69 |

| B.2  | Settling for R=7k $\Omega$ phase margin =179                                | 70 |

| В.3  | Output voltage swing of the folded cascode op-amp                           | 70 |

| B.4  | Settling for R=1k $\Omega$ phase margin = 72                                | 71 |

| B.5  | Input Common Mode Range                                                     | 71 |

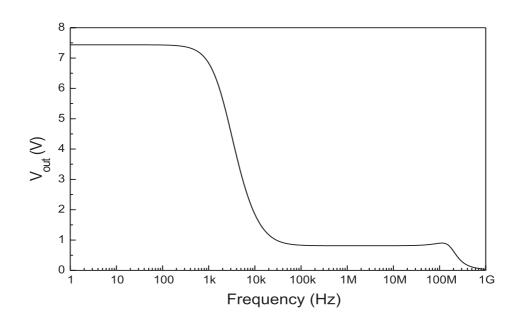

| B.6  | Effect of compensation C on magnitude response of the folded cascode        |    |

|      | opamp                                                                       | 72 |

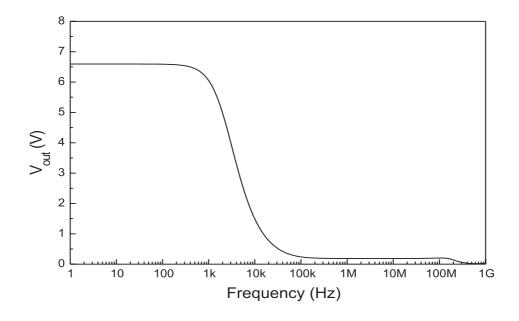

| B.7  | Effect of compensation capacitor on the phase response of the folded        |    |

|      | cascode op-amp                                                              | 72 |

| B.8  | Negative power supply rejection ratio PSRR                                  | 73 |

| B.9  | Positive power supply rejection ratio PSRR+                                 | 73 |

# List of Tables

| 1.1 | Comparison of some of the resonator technologies                    | 5  |

|-----|---------------------------------------------------------------------|----|

| 2.1 | Critical dimensions of 459 kHz microresonator used in the design of |    |

|     | oscillator                                                          | 14 |

| 3.1 | Nulling Resistor effect on Bandwidth and Phase Margin               | 35 |

| 3.2 | Overall Op-Amp Characteristics                                      | 39 |

| 3.3 | Critical values of the transistors in the op-amp                    | 40 |

## Chapter 1

### Introduction

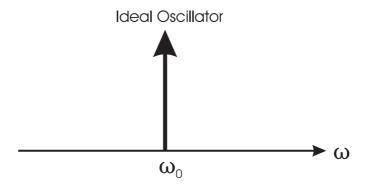

Oscillator circuits are widely used in communication circuits and instrumentation applications. Oscillators can be broadly classified into two groups: relaxation oscillators and harmonic oscillators. A relaxation oscillator tends to have poor phase noise characteristic and high harmonic content. A harmonic oscillator is capable of producing a near sinusoidal signal with good phase noise and high spectral purity. Harmonic oscillators usually use LC resonant circuits, crystals, or SAW resonators for defining the oscillation frequency.

Most of the high performance oscillators employ discrete components to meet many of the specifications for the functions required for communication technology. Using discrete components brings many disadvantages to communication circuits. First of all they are expensive and need to be integrated. But practically there are presently no integrated transistor- based filters or oscillators that can even match the performance of those based upon SAW resonators and Quartz crystals.

Integration is important not only for economic purposes but also in terms of size and power. These two are actually very much related when considering battery-operated wireless components. Although integration is necessary, product can not be made compact unless it consumes low enough power to allow the use of small batteries. Therefore replacing the off-chip components (quartz, crystals, ceramic filters, SAW resonators) with monolithically integrated versions, fabricated using the planar integrated circuit processing techniques of both CMOS and surface micromachining is crucial for many aspects mentioned above.

Mechanical elements are generally utilized as transducers when used in sensors. For example, an accelerometer uses a mechanical proof mass to sense acceleration in the mechanical domain and transduce it to voltage or charge in the electrical domain. If the accelerometer in question were a resonant accelerometer, then the quality factor of both the material and design would be a very important parameter. It is well known that the quality factor of mechanical resonators is generally orders of magnitude higher than achievable by discrete or integrated LCR tank circuits. For this reason, many of the high-Q filters and local oscillators required in communication systems are implemented using off-chip macroscopic mechanical components, which interface with the integrated amplifying and discriminating electronics on the board level. The use of off-chip components, although relatively inexpensive, makes production of such communications products cumbersome and prevents the realization of a truly compact product. Many study [2] has been done on this subject to solve the mentioned problems.

there is a great incentive to replace high-Q macroscopic (off-chip) elements with integrated versions, since this could potentially lead to a fully monolithic, batch fabricated transmitter or receiver systems. This theses aims to investigate the possibility of replacing the crystal, ceramic and SAW components currently used in today's communications equipment with equivalent miniaturized and integrable micromechanical versions.

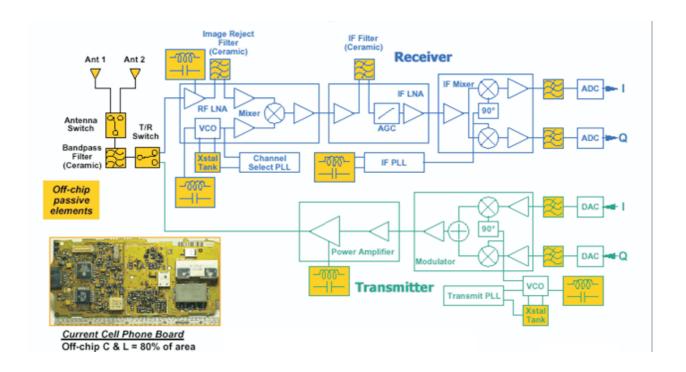

To get an idea of which components are replaceable we refer to Fig 1.1 which presents the simplified block diagram of a heterodyne receiver used in mobile communication systems. As it can be seen from the figure, off-chip components occupies 80% of the cellular phone board.

The target components which can potentially be replaced by micromechanics, then, include all off-chip high-Q components used in the IF amplifier, the local oscillator, and perhaps the RF filter (if micromechanical resonators can reach such frequencies) [5]. Whether such components are replaceable by micromechanics depends upon the specifications of the system and on the material and design properties of the micromechanical elements, in particular the quality factor. For example, poly silicon microresonator has Q in the range of over 30.000 at 30 MHz suggest that the broadcast FM receiver is feasible using micromachining technologies to replace off-chip components.

Once the off-chip components are miniaturized, a technology which then merges

Figure 1.1: Block diagram of a heterodyne receiver used in cellular phones and mobile communication systems

these devices with amplifying and discriminating electronics is all that is required to realize a fully monolithic receiver or transmitter.

## 1.1 Important Resonator Properties

Macroscopic mechanical resonators are extremely popular in the communications industry due to three basic properties: an extremely high quality factor, low temperature coefficient, and a very low aging rate. They are also quite inexpensive in large quantities. In addition, the electromechanical transduction mechanism and geometric vibration characteristics of quartz crystals make them easy to design with. For example, the low series resistance in the equivalent motional circuit for an AT-cut quartz crystal makes the design of sustaining amplifiers in oscillators much simpler, and it allows the design of crystal or mechanical filters much simpler in terms of filter termination. These are some of the properties that are desirable in the miniaturized integrated circuit mechanical resonators.

## 1.2 State-of-the-art Resonators

There are number of different types of resonators available to used in communication circuits. The most common ones are, Surface Acoustic Wave (SAW), LC, Crystal, Film Bulk Acoustic Resonator (FBAR) and MEMS resonator. SAW resonators are used in receiver front ends, fiber optic clock recovery, inductorless oscillators, VCOs etc. LC resonators is effective at low frequencies, since they have a great design and simulation flexibility and virtually no frequency limitation. Their sizes are substantially smaller than the other mechanical resonators. They can be integrated with ASICs. But LC resonators has poor quality factor at high frequencies. Crystal resonators are made of piezoelectric crystal, such as quartz, and exhibits electromechanical-resonance characteristics that are very stable (with time and temperature) and highly selective (having very high Q factors). They operate well until several hundred MHz. A basic FBAR device consists of a piezoelectric layer (ZnO) sandwiched between two electrodes above a via in a wafer. When a RF signal is applied across the device it produces a mechanical motion in the piezoelectric layer. The fundamental resonance is observed when the thickness of the film is equivalent to half the wavelength of the input signal. Currently ZnO is used as the piezoelectric material, however other materials such as AlN can also be used [1].

Tabular comparison of resonators is in the Table 1.2 [12].

Table 1.1: Comparison of some of the resonator technologies

|                     | MEMS                        | SAW                                  | Quartz                                        | FBAR                        | LC                               |

|---------------------|-----------------------------|--------------------------------------|-----------------------------------------------|-----------------------------|----------------------------------|

| Operation Principle | Capacitive                  | Piezoelectric                        | Piezoelectric                                 | Piezoelectric               | Electric                         |

| Quality Factor (Q)  | 500 (air)                   | 1500                                 | 100000                                        | 1000                        | 30-80                            |

| Frequency Range     | $< 100~\mathrm{MHz}$        | $50~\mathrm{MHz}$ - $2~\mathrm{GHz}$ | 50 kHz several 100 MHz $\mid$ 10 MHz - 10 GHz | 10 MHz - 10 GHz             | i 5 GHz                          |

| Typical Size        | $50~\mu m \times 50~\mu m$  | $1 \text{ cm} \times 1 \text{ cm}$   | $0.13 \times 0.08 \times 0.13 \ mm^2$         | $100~\mu m \times 50~\mu m$ | $\sim 100~\mu m \times 50~\mu m$ |

| Integration with IC | $\checkmark$                | ×                                    | ×                                             | ^                           | $\wedge$                         |

| Materials           | Silicon, Metals $LiTaO_3$ , | $LiTaO_3, LiNbO_3,$ Quartz           | $LiTaO_3$                                     | AIN, ZnO                    | Silicon                          |

## Chapter 2

### Design of MEMS resonator and its fabrication

In the past decade, the application of bulk and surface micromachining techniques greatly stimulated research in micromechanical structures and devices. Advancement in this field are motivated by potential applications in batch-fabricated integrated sensors and silicon microactuators.

MicroElctroMechanical (MEM) vibrating structures such as linear drive resonators can be used as driving components in signal processing applications. The applications are targeted for front-end transceivers and include oscillators and filters [4]- [8]. These devices promise new capabilities, as well as improved performance-to-cost ratio over conventional hybrid sensors. Micromachined transducers that can be fabricated compatibly with an integrated circuit process are the building blocks for integrated microsystems. Furthermore, miniaturized transducers are powerful tools for research in the micron-sized domain in the physical, chemical and biomedical fields.

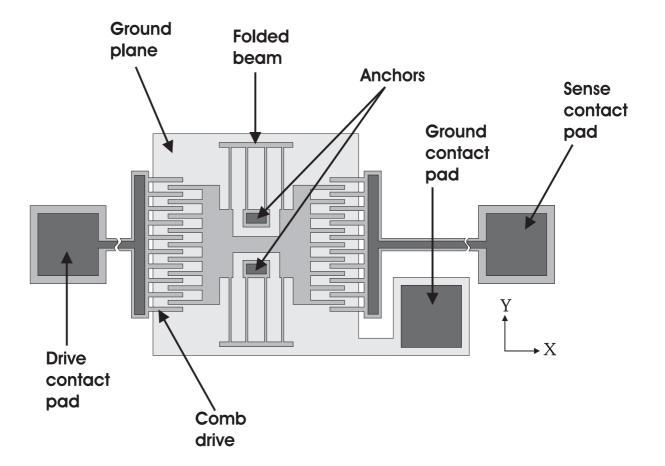

Integrated-sensor research is rigorously pursued because of the broad demand for low-cost, high-precision, and miniature replacements for existing hybrid sensors. In particular, resonant sensors are attractive for precision measurements because of their high sensitivity to physical or chemical parameters. These devices utilize the high sensitivity of the frequency of a mechanical resonator to physical or chemical parameters that affect its potential or kinetic vibrational energy. Electrostatic excitation combined with capacitive (electrostatic) detection is an attractive approach for silicon microstructures because of simplicity and compatibility with micromachining technology [14]. Figure 2 shows the layout of a linear resonant structure which can be driven electrostatically from one side and sensed capacitively at the

Figure 2.1: Layout of a linear lateral resonator

other side with interdigitated finger (comb) structures. Alternatively, the structure can be driven differentially (push-pull) using the two combs, with the motion sensed by the impedance shift at resonance [14].

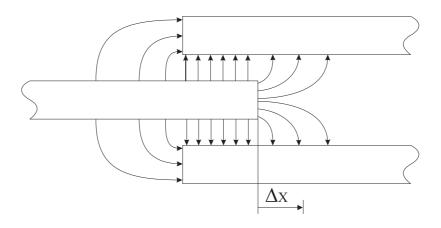

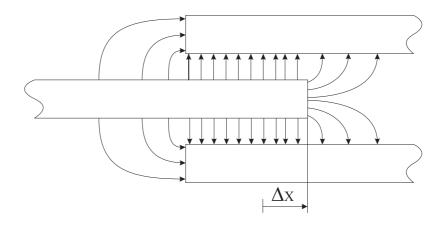

The electrostatic comb structure can be used either as a derive or a sense element. The induced driving force and the output sensitivity are both proportional to the variation of the comb capacitance C with the lateral displacement x of the structure,  $\partial C/\partial x$ . A key feature of the electrostatic comb derive is that  $\partial C/\partial x$  is a constant independent of the displacement  $\Delta x$ , as long as  $\Delta x$  is less than the overlap We can model the capacitance between the movable comb fingers and the stationary fingers as a parallel combination of two capacitors, one due to the fringing fields,  $C_f$ , and the other due to the normal fields,  $C_n$ . By considering the electric filed distribution difference between before and after the displacement of the finger as shown in Figure 2, it becomes obvious that  $C_f$  is independent of the displacement,  $\Delta x$ , while  $C_n$  is linearly proportional to  $\Delta x$ .

Figure 2.2: Electric Field distribution before and after the movable finger displaces by  $\Delta x$  into the slot

## 2.1 Transfer Function

In analyzing the electromechanical transfer function, we consider the resonator is driven electrostatically with the comb structure from one side and sensed capacitively at the other side as illustrated in Figure 2.1.

At the drive port, the induced electrostatic force in the x direction,  $F_x$  is found by Tang [14] and given by

$$F_x = \frac{1}{2} \frac{\partial C}{\partial x} v_D^2 \tag{2.1}$$

where  $v_D$  is the derive voltage across the structure and stationary drive electrode. For a drive voltage  $v_D(t) = V_P + v_d sin(\omega t)$ , where  $V_P$  is the DC bias at the derive port and  $v_d$  is the AC drive amplitude, Equation 2.1 becomes

$$F_{x} = \frac{1}{2} \frac{\partial C}{\partial x} \left[ V_{P}^{2} + \frac{1}{2} v_{d}^{2} + 2V_{P} v_{d} sin(\omega t) - \frac{1}{2} v_{d}^{2} cos(2\omega t) \right]$$

(2.2)

Figure 2.3: A linear resonator electrostatically driven from one side and sensed capacitively at the other side

Given the system spring constant in the x direction,  $k_x$ , and a damping factor, c, the equation of the motion is a second-order-differential equation given by

$$Mx'' + cx' + k_x x = F_x(t) (2.3)$$

where M is the effective mass of the structure. Therefore after tedious calculations the steady state response x is a simple harmonic function given by

$$x(t) = \frac{2(\partial C/\partial x)V_P v_d}{\sqrt{(k_x - M\omega^2)^2 + c^2\omega^2}} sin(\omega t - \phi_1)$$

(2.4)

the motion is sensed by detecting the short-circuit current through the time varying comb capacitor with a dc bias. At the sense port, harmonic motion of the structure results in a sense current,  $i_s$ , which is given by

$$i_s = V_S \frac{\partial C}{\partial x} \frac{\partial x}{\partial t} \tag{2.5}$$

where  $V_S$  is the bias voltage between the structure and the stationary sense electrode.

## 2.2 Mechanical Analysis

The design criteria for lateral resonator are two. First, the suspensions should provide freedom of travel along the direction of the comb-finger motions (x), while restraining the structure from moving sideways (y) to prevent the comb fingers from shorting to the drive electrodes. Therefore, the spring constant along the y direction must be much higher than that along the x direction, i.e.,  $k_y \gg k_x$ . Second, the suspensions should allow for the relief of the built-in stress of the structural poly silicon film as well as axial stress induced by large vibrational amplitudes. Folded beam suspension design fulfills these two criteria. This design allows large deflection in the x direction (perpendicular to the length of the beams) while providing stiffness in the y direction (along the length of the beams). Furthermore, the only anchor points for the whole structure are near the center, thus allowing the parallel beams to expand or contract in the y direction, relieving most of the built-in stress.

Spring constant in the x direction is with the resonant plate is statically displaced by a distance  $X_0$  under an applied force  $F_x$  in the positive x direction is given below. Each of the beams has a length L, width w, and thickness h.

$$k_x = \frac{F_x}{X_0} = \frac{24EI_z}{L^3} \tag{2.6}$$

where  $I_z$  is the moment of inertia with respect to the z axis and E is Young's modulus. For an ideal beam with rectangular cross section having a width w and a thickness h, the moment of inertia is

$$I_z = \frac{hW^3}{12} \tag{2.7}$$

### 2.2.1 Lateral Resonant Frequency

Using Rayleigh's energy method

$$K.E._{max} = P.E._{max} \tag{2.8}$$

and a mass of calculation as did by tang et all we can reach resonant frequency formula as in Equation 2.9 where  $K.E._{max}$  is the maximum kinetic energy during a

vibration cycle, and  $P.E._{max}$  is the maximum potential energy.

$$\omega = \left(\frac{k_x}{M_p + \frac{1}{4}M_t + \frac{12}{35}M_b}\right)^{\frac{1}{2}} \tag{2.9}$$

The denominator on the right-hand side of this equation can be lumped together as the effective mass of the system, M

$$M = M_p + \frac{1}{4}M_t + \frac{12}{35}M_b \tag{2.10}$$

such that

$$\omega = \left(\frac{k_x}{M}\right)^{\frac{1}{2}} \tag{2.11}$$

Substituting the Equations 2.7 and 2.6 in the above resonance frequency formula and more elegant and playing a little bit denominator more instructive and useful expression can be obtained as below [11].

$$f_r = \frac{1}{2\pi} \left[ \frac{2Eh(\frac{W}{L})^3}{M_n + 0.3714M} \right]^{\frac{1}{2}}$$

(2.12)

where  $M_p$  and M are the masses of the plate and of the supporting beams respectively.

### 2.2.2 Quality Factor

One of the advantages of laterally driven resonant structures is that the damping in the lateral direction is much lower than in vertical direction. Therefore when operated in air, undesired vertical motions are conveniently damped. There are a number of dissipative processes during lateral motion, all of them affecting the quality factor Q. The dominant influences include Coutte flow underneath the plate, air drag on the top surface, damping in the comb gaps and direct air resistance related to the thickness of the structure [11]. If we consider Coutte flow alone, then we can estimate the quality factor Q as

$$Q = \frac{d}{\mu A_p} \sqrt{Mk_x} \tag{2.13}$$

where  $\mu$ is the absolute viscosity of air, d is the offset between the plate and the substrate, and M is the effective mass of the resonator. when resonated in vacuum, vibrational energy is mostly dissipated to the substrate through the anchors, or polysilicon structure itself.

### 2.3 MicroResonator Fabrication

The fabrication process for the electrostatic-comb drives and associated lateral structures is a straightforward application of the surface-micromachining technology. The structures are fabricated with six-mask process illustrated in Figure 2.3. A significant advantage of this technology is that all the critical features are defined with one mask, eliminating errors due mask-to-mask misalignment. The process begins with metal deposition onto silicon wafer using teknoplasma sputter system, which defines DC plane of the microresonator. After this  $SiO_2$  deposited on top of the metal layer. Then contact windows to the metal layer opened using wet etching. The next steps involve the deposition of the second metal layer and patterning with Karl- Suss mask aligner. Sacrificial PSG layer deposited and patterned for dimple formation and anchor openings. Poly silicon structural layer is then deposited on top of the patterned PSG layer. After stripping the PSG layer the final microresonator structure is formed.

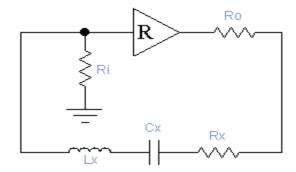

### 2.4 Small Signal Equivalent Circuits for Micromechanical Resonators

The equivalent circuit describing microresonator performance under AC electrostatic excitation can be derived through consideration of the electromechanical transduction mechanism and the details of resonator construction (i.e. geometry and structural material) [2]. For two port microresonator we can think of the whole system as a black box. Its behaviour as seen by its port can be modeled as a series RLC circuit. Nguyen found small signal model of the resonator in his theses [13]. where  $C_{o1}$  is the total DC capacitance (i.e. the value of capacitance for a motionless shuttle), Q is the quality factor, k is the system spring constant and  $V_P$  is the voltage difference between input comb drive and shuttle. Corresponding  $C_x$ ,  $L_x$ ,  $R_x$  values

are

$$C_x = \frac{\left[V_P \frac{\partial C}{\partial x}\right]^2}{k} \tag{2.14}$$

$$L_x = \frac{k}{\omega_r^2 [V_P \frac{\partial C}{\partial x}]^2}$$

(2.15)

$$R_x = \frac{k}{\omega_r^2 Q[V_P \frac{\partial C}{\partial x}]^2}$$

(2.16)

$$\frac{\partial C}{\partial x} \approx \frac{\xi N \epsilon_0 h}{d} \tag{2.17}$$

where h is the shuttle finger thickness, d is the gap between electrode and resonator fingers, and N is the number of finger gaps.  $\xi$  is a constant that models additional capacitance due to fringing electric fields. As it is seen from the formulas, the model parameters are strictly depend on the dimensions (Beam length/width, DC bias voltage, number of finger overlaps N, gap spacings between fingers etc.) and construction of the resonator. Therefore dimensions of the resonator must be carefully chosen to obtain desired results. Figure 2.4 shows all the critical dimensions of the comb drive that effects the resonance frequency, spring constant, model parameters, etc.

The resonance frequency of this micromechanical resonator is determined largely by W/L ratio of the folded beams. Therefore, by decreasing the length L of the beam and by keeping the other parameters in Equation 2.12 constant, the resonance frequency is tuned to the desired value. The variables as presented in Table 2.4 above, define critical parameters along with their values used in this study. The resonance frequency can be verified by using combined information of Table 2.4 and Equation 2.12.

### 2.5 Summary

In this chapter we have discussed basic operation principles and electrostatic characteristics of microresonator. Resonance frequency, Quality factor, important device dimensions were given. Small signal equivalent circuit of the microresonator is created in order to model the device and to make it ready for simulation in the electrical domain. Furthermore we have described the poly silicon surface-micromachining techniques for fabricating the laterally-driven microstructures.

Table 2.1: Critical dimensions of 459 kHz microresonator used in the design of oscillator

|           | Parameter                 | Value                        |  |

|-----------|---------------------------|------------------------------|--|

| E         | Young's modulus           | 150 GPa                      |  |

| $\mu$     | Absolute viscosity of air | $17.46x10^{-6}Ns/m^2$        |  |

| H         | Structure thickness       | $2~\mu m$                    |  |

| W         | Beam width $2 \mu m$      |                              |  |

| L         | Beam length               | $25\mu m$                    |  |

| M         | Mass (beam + truss)       | $1.791110^{-12} \text{ Kg}$  |  |

| $M_P$     | Shuttle mass              | $3.4333x10^{-11} \text{ Kg}$ |  |

| $k_{sys}$ | System spring constant    | $303.543~\mathrm{N/m}$       |  |

| Q         | Quality factor            | 1250.22                      |  |

| $f_r$     | Resonance frequency       | $459.017~\mathrm{kHz}$       |  |

Figure 2.4: Process Sequence of the Micro resonator

Figure 2.5: Block representation of the microresonator

Figure 2.6: Equivalent circuit model of the microresonator  $\,$

Figure 2.7: Critical Dimensions of a comb drive

# Chapter 3

# Design of CMOS Analog Integrated Circuits for MEMS Oscillator

This chapter concentrates on the design of analog integrated circuits. Op-amps and their performance characteristics are the main subject of this chapter. ICs are designed using AMS  $0.35\mu$  [26] CMOS technology. Two different op-amp architectures are applied namely, 1. Basic two stage op-amp 2. Folded cascode op-amp.

Oscillators need a sustaining amplifier to ensure oscillation. Amplifiers used in oscillators must be stable and broad band. High gain is the another attribute to construct a high quality oscillators. Therefore, amplifier design specifically op-amp design is a key issue when dealing with oscillators. There has been many research done on improving performance of the op-amps. These include increasing gain, broadening bandwidth and constructing more stable op-amps [19]- [23]. Before going to optimizing op-amp characteristics, It is useful to give some details about op-amps.

## 3.1 Two Stage CMOS Op-amp

Currently, the most widely used circuit approach for implementation of MOS operational amplifiers is the two-stage configuration shown in Figure 3.1. This circuit configuration provides good common mode range, output swing, voltage gain, and CMRR in a simple circuit that can be compensated with a single pole-splitting capacitor [27]. In this section, we will analyze the various performance parameters of the CMOS implementation of this circuit.

First stage of two stage op-amp is simple differential pair, therefore, it is instructive to begin with it. The Differential input stage consists of  $M_1, M_2, M_3$ , and  $M_4$ ,

Figure 3.1: Simplified basic two stage Op-amp

with  $M_1$  matching  $M_2$  and  $M_3$  matching  $M_4$  as shown in Figure 3.2. The small signal analysis of the differential input stage can be accomplished with the assistance of the model shown in Figure 3.1 which is only appropriate for differential analysis when both sides of the amplifier are assumed to be perfectly matched. If this condition is satisfied, then the point where the two sources of  $M_1$  and  $M_2$  are connected can be considered at AC ground.

$$C_1 \approx C_{gd1} + C_{gs3} + C_{gs4}$$

(3.1)

$$C_2 \approx C_{gd2} \tag{3.2}$$

$$C_3 \approx C_{gd4} \tag{3.3}$$

Therefore, the small signal gain of the differential pair is simply

$$V_{out}/V_{id} = g_m(r_{o2} \parallel r_{o4})$$

(3.4)

$$g_m(r_{o2} \parallel r_{o4}) \approx \frac{1}{\lambda I_{SS}}$$

$$g_m = \sqrt{k'(W/L)I_{SS}}$$

$$(3.5)$$

$$g_m = \sqrt{k'(W/L)I_{SS}} \tag{3.6}$$

$$A_v = \frac{V_{out}}{V_{id}} = \sqrt{k'} \sqrt{\frac{W_{1,2}}{L_{1,2}I_{SS}}} (\frac{1}{\lambda})$$

(3.7)

The expression of gain illustrates several key aspects of MOS devices used as analog amplifiers. First, for constant drain current decreasing either the channel length or

Figure 3.2: MOS differential pair

width results in a decrease in the gain. This fact, along with noise considerations, usually dictates the minimum size of the transistors that must be used in a given high-gain amplifier application. Usually, this is larger than the length and width used for digital circuits in the same technology. Second, if the device geometry is kept constant, the voltage gain is inversely proportional to the square root of the drain current [27]. To summarize, k' is a constant, uncontrollable by the designer and the effect of  $\lambda$  on the gain diminishes as L increases, such that  $1/\lambda$  is directly

Figure 3.3: The simplified equivalent model of differential pair

proportional to the channel length. Then proportionality can be established between  $W_{1,2}/L_{1,2}$  and the drain current versus the small signal gain such that:

$$A_v \propto \sqrt{\frac{W_{1,2}}{L_{1,2}I_{SS}}} \tag{3.8}$$

Conclusions:

- Increasing  $W_{1,2}, L_{1,2}$  or both increases the gain

- Decreasing the drain current through  $M_1$  and  $M_2$  increases the gain.

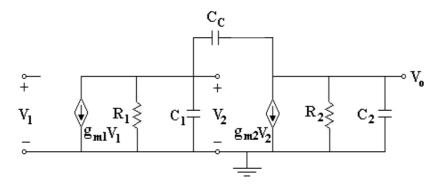

#### 3.1.1The Frequency Response, Compensation

Operational amplifier architectures are generally of two types: single-stage externally compensated or two stage internally compensated amplifiers, both of which can have a dominant two pole type frequency response [28]. Ignoring higher order poles, the small signal behaviour of the two stage amplifier can be modeled by the general two pole, one zero small signal equivalent circuit shown in Figure 3.7. Referring back to the model of the input stage Figure 3.1, we will work to find poles of the system. We have two poles these are

$$p_{1} = \frac{1}{C_{1} \frac{1}{g_{m3}}}$$

$$p_{2} = \frac{1}{C_{2}(r_{o2} \parallel r_{o4})}$$

(3.9)

$$p_2 = \frac{1}{C_2(r_{o2} \parallel r_{o4})} \tag{3.10}$$

Since  $p_1 \gg p_2$  we can approximate gain as

$$A_v = g_m(r_{o2} \parallel r_{o4}) \frac{1}{1 + \frac{s}{C_2(r_{o2} \parallel r_{o4})}}$$

(3.11)

The compensation of the two stage CMOS amplifier can be carried out using a pole splitting capacitor. The goal of the compensation task is to achieve a phase margin greater than 45°. The circuit can be approximately represented by the smallsignal equivalent circuit of Figure 3.7 if the nondominant poles which may exist on the circuit are neglected.

The overall transfer function that results from the addition of  $C_C$  is [29].

$$\frac{V_{o(s)}}{V_{in(s)}} = \frac{g_{m1}g_{m2}R_1R_2(1 - sC_C/g_{m2})}{1 + s[R_1(C_1 + C_C) + R_2(C_2 + C_C) + g_{m2}R_1R_2C_C] + s^2R_1R_2[C_1C_2 + C_C(C_1 + C_2)]}$$

(3.12)

The circuit displays two poles and a right half plane zero, which under the assumption that the poles are widely separated, can be shown to be approximately located at

$$p_1 = \frac{-1}{(1 + g_{m2}R_2)C_CR_1} (3.13)$$

$$p_{2} = \frac{-g_{m2}C_{C}}{C_{2}C_{1} + C_{2}C_{C} + C_{C}C_{1}}$$

$$z = \frac{g_{m2}}{C_{C}}$$

(3.14)

$$z = \frac{g_{m2}}{C_C} \tag{3.15}$$

Note that the pole due to the capacitive loading of the first stage by the second,  $p_1$ , has been pushed down to a very low frequency by the miller effect in the second stage, while the pole due to the capacitance at the output node of the second stage,  $p_2$ , has been pushed to a very high frequency due to the shunt feedback. For this reason, the compensation technique is called pole splitting.

Physically, the zero arises because the compensation capacitor provides a path for the signal to propagate directly through the circuit to the output at high frequencies. Since there is no inversion in that signal path as there is in the inverting path dominant at low frequencies, stability degraded. Fortunately two effective means have evolved for eliminating the effect of the right half-plane zero. One approach has been to insert a source follower in the path from the output back through the compensation capacitor. An even simpler approach is to insert a nulling resistor in series with the compensation capacitor as shown in Figure 3.4. Using an analysis

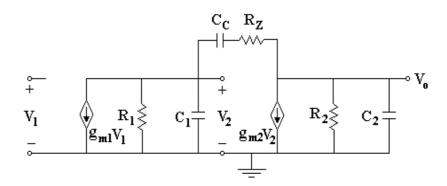

Figure 3.4: Simplified small signal model of the basic two stage Op-amp added with the nulling resistor

similar to that performed for the circuit of Figure 3.7, one obtains pole locations which are close to those for the original circuit, and a zero. This circuit has the fallowing node-voltage equations.

$$g_{m1}V_{in} + \frac{V_2}{R_1} + sC_1V_2 + \left(\frac{sC_C}{1 + sC_CR_Z}\right)(V_2 - V_O) = 0$$

(3.16)

$$g_{m2}V_2 + \frac{V_O}{R_2} + sC_2V_O + \left(\frac{sC_C}{1 + sC_CR_Z}\right)(V_O - V_2) = 0$$

(3.17)

These equations can be solved to give

$$\frac{V_{o(s)}}{V_{in(s)}} = \frac{a\{1 - s[(C_C/g_{m2}) - R_Z C_C]\}}{1 + bs + cs^2 + ds^3}$$

(3.18)

where

$$a = g_{m1}g_{m2}R_1R_2 (3.19)$$

$$b = R_2(C_2 + C_C) + R_1(C_1 + C_C) + g_{m2}R_1R_2C_C + R_ZC_C$$

(3.20)

$$c = [R_1 R_2 (C_1 C_2 + C_C C_1 + C_C C_2) + R_Z C_C (R_1 C_1 + R_2 C_2)]$$

(3.21)

$$d = R_1 R_2 R_Z C_1 C_2 C_C (3.22)$$

If  $R_Z$  is assumed to be less than  $R_1$  or  $R_2$  and the poles are widely spaced, then the roots of the above equation can be approximated as

$$p_1 = \frac{-1}{(1 + g_{m2}R_2)C_CR_1} \cong \frac{-1}{g_{m2}R_2R_1C_C}$$

(3.23)

$$p_2 = \frac{-g_{m2}C_C}{C_2C_1 + C_2C_C + C_CC_1} \cong \frac{-g_{m2}}{C_2}$$

(3.24)

$$p_3 = \frac{-1}{R_Z C_1} \tag{3.25}$$

and

$$z = \frac{-1}{C_C(\frac{1}{g_{m2} - R_Z})} \tag{3.26}$$

The resistor  $R_Z$  allows independent control over the placement of the zero. The zero vanishes when  $R_Z$  is made equal to  $1/g_{m2}$ . In fact, the resistor can be further increased to move the zero into the left half-plane and place it on top of  $p_2$  to improve the amplifier phase margin.  $R_Z$  can be realized by a MOS transistor in the triode region. The value of  $R_Z$  can be found as

$$R_Z = \left(\frac{C_2 + C_C}{C_C}\right) \frac{1}{g_{m2}} \tag{3.27}$$

#### 3.1.2 Open Circuit Voltage Gain

The voltage gain of the first stage was found (differential pair) in previous section to be given by

$$A_1 = -g_{m1}(r_{o2} \parallel r_{o4}) \tag{3.28}$$

where  $g_{m1}$  is the transconductance of each of the first stage that is  $M_1$  and  $M_2$ . The second stage is an actively loaded common-source amplifier whose voltage gain is given by

$$A_2 = -g_{m6}(r_{o6} \parallel r_{o7}) \tag{3.29}$$

The dc open loop gain of the op amp is the product of  $A_1$  and  $A_2$ .

$$A = g_{m1}g_{m6}(r_{o2} \parallel r_{o4})(r_{o6} \parallel r_{o7}) \tag{3.30}$$

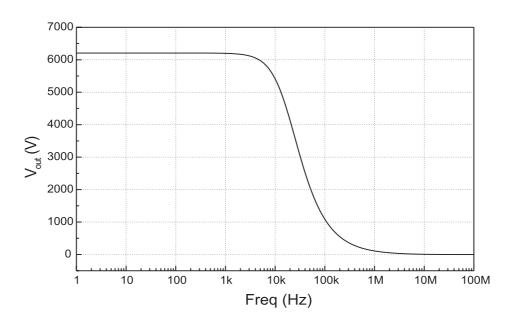

Figure 3.5: AC Frequency Simulation of the Op-Amp. DC gain of this Op-Amp is more than 6000 V/V.

#### 3.1.3 DC Offsets, DC Biasing

In MOS op amps, because of the relatively low gain per stage, the offset voltage of the differential to single-ended converter and the second stage can play an important role. In Figure 3.7, the operational amplifier has been split into two separate stages.

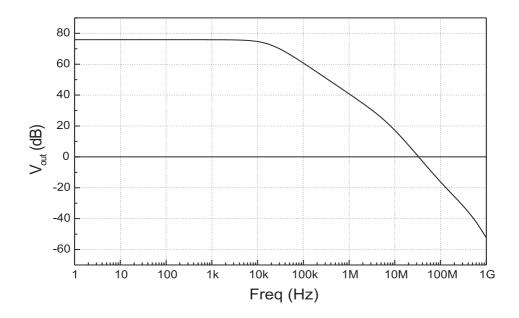

Figure 3.6: AC Frequency Response in terms of dB. DC gain is 75 dB

Assuming perfectly matched devices, if the inputs of the first stage are grounded, then the quiescent output voltage at the drain of  $M_4$  is equal to the voltage at the drain of  $M_3$  ( $M_3$  and  $M_4$  have the same drain current and gate-source voltage, and hence must have the same drain-source voltage). However, the value of the gate voltage of  $M_6$  which is required to force the amplifier output voltage to zero may be different from the quiescent output voltage of the first stage. For a first stage gain of 50, for example, each 50 mV difference in these voltages results in 1 mV of input-referred systematic offset. Thus, the W/L ratios of  $M_3$ ,  $M_4$ , and  $M_6$  must be chosen so that the current densities in these three devices are equal. For the simple circuit of Figure 3.1 this constraint would take the form

Figure 3.7: Simplified small signal model of the basic two stage Op-amp

$$\frac{(W/L)_3}{(W/L)_6} = \frac{(W/L)_4}{(W/L)_6} = \frac{1}{2} \frac{(W/L)_5}{(W/L)_7}$$

(3.31)

Systematic offset voltage is closely correlated with dc power supply rejection ratio. If a systematic offsets exists, it is likely to display dependence on power supply voltage, particularly if the bias reference source is such that the bias currents in the amplifier are not supply independent. Figure 3.8 shows input offset voltage of the basic two stage op-amp of our interest. Figure 3.9 shows input common mode range and output swing of the same circuit.

Figure 3.8: Simulation results showing the Input Offset voltage (484.6  $\mu V$  in this circuit)

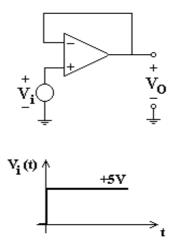

#### 3.1.4 Slew Rate

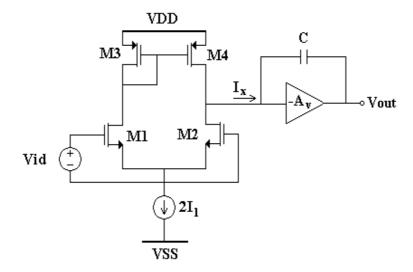

The rate of change of output voltage dVo/dt in response of a large step input is called slew rate and is usually specified in  $V/\mu s$ . Consider the circuit Figure 3.10and input step for testing the slew-rate performance. At t=0, the input voltage steps to +5 V, but the output voltage cannot respond instantaneously and is initially zero. Thus the op-amp differential input is  $V_{id} = 5V$ , which drives the input stage completely out of its linear range of operation. This can be seen by considering a two-stage op-amp, simplified schematics for CMOS op amp used in this analysis shown in Figure 3.11. The Miller compensation capacitor C connects around the

Figure 3.9: Simulation results showing the ICMR and output swing

high-gain second stage and causes this stage to act as an integrator. The large-signal transfer characteristic from the op-amp differential input voltage  $V_{id}$  to  $I_X$  is that of a differential pair, the maximum current available to charge C is  $2I_1$ , which is the tail current in the input stage. Consider a large input voltage applied to the circuit of Figure 3.11 so that  $I_X = 2I_1$ . Then the second stage acts as an integrator with an input current  $2I_1$ , and output voltage  $V_O$  can be written as

$$V_O = \frac{1}{C} \int 2I_1 dt \tag{3.32}$$

and thus

$$\frac{dV_O}{dt} = \frac{2I_1}{C} \tag{3.33}$$