# AN 8-BIT 100 MS/s TIME-INTERLEAVED SAR-ASSISTED PIPELINE ADC WITH IMPROVED RESIDUE AMPLIFIER

#

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Sabancı University July 2022

#### **ABSTRACT**

# AN 8-BIT 100 MS/s TIME-INTERLEAVED SAR-ASSISTED PIPELINE ADC WITH IMPROVED RESIDUE AMPLIFIER

#### CERIN NINAN KUNNATHARAYIL

EE, PhD Thesis, 2022

Dissertation Supervisor: Prof. Dr. Yaşar GÜRBÜZ

Keywords: High-speed SAR logic, Residue Amplifier, SAR-Assisted Pipeline ADC, Simultaneous-Switching Noise (SSN), Zero-Crossing Detector (ZCD)

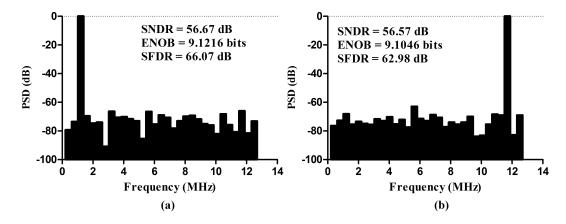

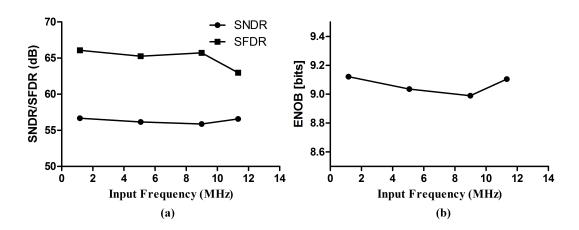

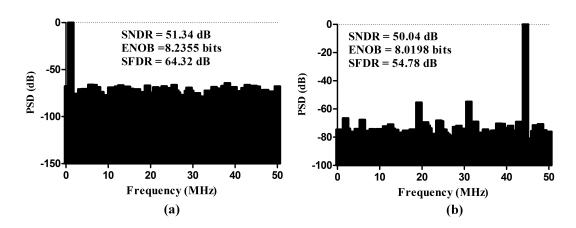

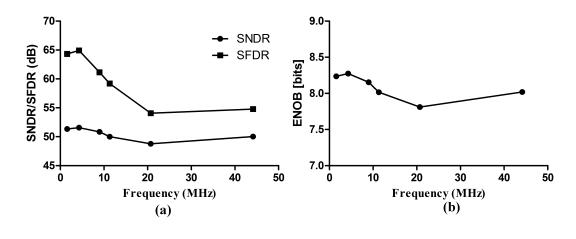

In a successive approximation register (SAR)-assisted pipeline analog-to-digital converters (ADC), SAR ADC and residue amplifier are the two blocks that determine the speed and power of the ADC. Among them, the residue amplifier is the most power-hungry. Traditionally, the residue amplifier uses a high-gain op-amp, but as the CMOS technology scales, the intrinsic gain of the transistor reduces. Hence, the residue amplifier is designed based on zero-crossing-based circuits (ZCBCs) as it is not affected by the scaling down of the CMOS technology. The limitation of the ZCBC-based residue amplifier is the overshoot voltage arising for technology nodes that have low f<sub>T</sub>. Hence, a novel overshoot reduction technique is introduced in the residue amplifier. The overshoot voltage and time were simulated for different corner cases. The final range of the overshoot voltage and time after implementing the novel overshoot reduction technique was attained from 0.584 mV to 1.59 mV and 124 ps to 423 ps, respectively. The percentage reduction in the overshoot time and voltage ranges w.r.t to the case when the overshoot reduction technique was not used ranges from 90.544% to 98.012% and 89.153% to 97.67%, respectively. The novel overshoot reduction technique was implemented in the 2-bit/cycle sub-radix  $V_{cm}$ -based SAR-assisted pipeline ADC. The post-layout simulation results show an SNDR, an SFDR, and an ENOB of 56.57 dB, 62.98 dB, and 9.1046 bits, respectively with a sampling speed of 25 MHz at a near Nyquist frequency of 11.328125 MHz, and the ADC consumes a power of 8.212 mW. The 2-bit/cycle sub-radix V<sub>cm</sub>-based SAR-assisted pipeline ADC was implemented in a 4-channel Time-Interleaved ADC. The post-layout SNDR, SFDR, and ENOB were attained as 50.04 dB, 54.78 dB, and 8.0198 bits, respectively with a sampling speed of 100 MHz at a near Nyquist frequency of 44.140625 MHz.

## ÖZET

# İYİLEŞTİRİLMİŞ ARTIK YÜKSELTEÇLİ 8-BIT 100 MS/S ZAMAN ARALIKLI SAR YARDIMLI BORU HATTI ADC

#### CERIN NINAN KUNNATHARAYIL

Elektronik Mühendisliği 2022

Tez Danışmanı: Prof. Dr. Yaşar GÜRBÜZ

Anahtar Kelimeler: Yüksek hızlı SAR mantığı, Artık Yükseltici, SAR Destekli Boru Hattı ADC, Eşzamanlı Anahtarlama Gürültüsü (SSN), Sıfır Geçiş Dedektörü (ZCD)

Ardışık bir yaklaşım kaydı (SAR) destekli boru hattı analogdan dijitale dönüştürücülerde (ADC), SAR ADC ve kalıntı yükseltici, ADC'nin hızını ve gücünü belirleyen iki bloktur. Bunlar arasında, kalıntı amplifikatörü güce en aç olanıdır. Geleneksel olarak, kalıntı yükseltici yüksek kazançlı bir op-amp kullanır, ancak CMOS teknolojisi ölçeklendikçe transistörün içsel kazancı azalır. Bu nedenle, kalıntı amplifikatörü, CMOS teknolojisinin ölçeğinin küçültülmesinden etkilenmediği için sıfır geçiş tabanlı devrelere (ZCBC'ler) dayalı olarak tasarlanmıştır. ZCBC tabanlı artık yükselticinin sınırlaması, düşük f<sub>T</sub>'ye sahip teknoloji düğümleri için ortaya çıkan aşırı gerilimdir. Bu nedenle, artık yükselticide yeni bir aşım azaltma tekniği tanıtılmıştır. Farklı köşe durumları için aşım voltajı ve süresi simüle edildi. Yeni aşım azaltma tekniğinin uygulanmasından sonra aşım voltajının son aralığı ve süre sırasıyla 0,584 mV ila 1,59 mV ve 124 ps ila 423 ps arasında elde edildi. Aşım süresi ve voltaj aralıklarındaki yüzde azalma, aşım azaltma tekniğinin kullanılmadığı duruma göre sırasıyla %90.544 ila %98.012 ve %89.153 ila %97.67 aralığındadır. Yeni aşma azaltma tekniği, 2 bit/döngü alt tabanı  $V_{cm}$  tabanlı SAR destekli ardışık düzen ADC'de uygulandı. Yerleşim sonrası simülasyon sonuçları, yaklaşık 11.328125 MHz Nyquist frekansında 25 MHz örnekleme hızıyla sırasıyla 56.57 dB, 62.98 dB ve 9.1046 bitlik bir SNDR, bir SFDR ve bir ENOB gösterir ve ADC bir güç tüketir. 8.212 mW. 2 bit/döngü alt tabanı  $V_{cm}$ -tabanlı SAR destekli ardışık düzen ADC, 4 kanallı Zaman Ara Eklemeli ADC'de uygulandı. Yerleşim sonrası SNDR, SFDR ve ENOB sırasıyla 50.04 dB, 54.78 dB ve 8.0198 bit olarak, 100 MHz örnekleme hızında 44.140625 MHz'e yakın Nyquist frekansında elde edildi.

#### ACKNOWLEDGEMENTS

Firstly, I would like to thank my advisor Prof. Yaşar Gürbüz for giving me the chance to join his lab and work in his group. I am also grateful to him for supporting and being patient with me when i got stuck with certain work in my Ph.D. and for helping me out whenever I had any problems. I would also like to thank Asst. Prof. Ömer Ceylan. I am grateful to Omer abi for mentoring, helping me analyze the problem, giving suggestions on how to solve the issue, reviewing my papers and giving suggestions to them, and guiding me in my work. I would also like to thank Asst. Prof. Melik Yazıcı. I am thankful to Melik for helping me with the tapeouts and giving me ideas on solving issues in my work. Moreover, I would like to thank the laboratory specialist, Ali Kasal. I am grateful to Ali abi for fabricating my boards which i know are tough. I am also grateful to him for helping me in finding ways to solve the issues on the board. I would also like my internal jury member Asst. Prof. Erdinç Öztürk for his guidance, support, and help. I would like to thank Prof. Selim Balcısoy for accepting to be a jury member at the last moment.

I would like to thank my thesis jury members Assoc. Prof. Dr. Tufan Çoşkun Karalar and Assoc. Prof. Dr. Mustafa Altun for their valuable time to spare in my thesis committee and for their precious comments, advice, and feedback.

I would like to thank my current lab members: Tahsin Alper Ozkan, Umut Barış Göğebakan, Ajten Fejzullahu, Cengizhan Kana, Erkut Gürol, Kutay Altıntaş, Nezih Kaan Veziroğlu, Serhan Özboz, Umut Barut, Ali Bahadır Özdöl and Deniz Anıl for their friendship which made the working environment comfortable for me and keep me motivated. I would also like to thank the former members of SUMER: Elif Gül Arsoy, Abdurrahman Burak, Mir Hassan Mahmud, Eşref Türkmen, Emre Can Durmaz, Alper Güner, Hamza Kandiş, Isik Berke Güngör, Ilker Kalyoncu, Shahbaz Abbasi and Can Çalışkan.

I would like to thank my parents, Annie K Ninan and K N Ninan, and my sister Ceri for their unconditional love and endless support. I would not have come this far without their support and the sacrifices they have made for me. I also thank my grandmother, uncle, aunts, and cousins for their support. I would like to thank my friends: Ali Rashed, Hossein Mahdavi, Arghavan Sharafi, Akshay Mann, Tanu Choudhary, and many others for their friendship throughout the years.

I would like to thank the Turkish Scientific and Technology Research Institution (TUBITAK) having the grant number 118E828 for supporting me with the scholar-ship throughout my studies.

And finally, I thank God.

$Aileme... \\ To \ my \ Parents...$

# TABLE OF CONTENTS

| LI | ST (                                                       | OF TA            | BLES                                                      | X  |  |

|----|------------------------------------------------------------|------------------|-----------------------------------------------------------|----|--|

| LI | ST (                                                       | OF FIG           | GURES                                                     | xi |  |

| 1. | Intr                                                       | oducti           | ion                                                       | 1  |  |

|    | 1.1.                                                       | Motiv            | ation                                                     | 1  |  |

|    | 1.2.                                                       | Techn            | ical Challenges and Solutions                             | 3  |  |

|    | 1.3.                                                       | Thesis           | S Outline                                                 | 3  |  |

| 2. | SAR-Assisted Pipeline ADC and Parameters to understand the |                  |                                                           |    |  |

|    | AD                                                         | C Peri           | formance                                                  | 6  |  |

|    | 2.1.                                                       | SAR-A            | Assisted Pipeline ADC                                     | 6  |  |

|    |                                                            | 2.1.1.           | SAR ADC                                                   | 6  |  |

|    |                                                            | 2.1.2.           | Pipeline ADC                                              | 9  |  |

|    |                                                            | 2.1.3.           | SAR-Assisted Pipeline ADC Architecture                    | 11 |  |

|    | 2.2.                                                       | Paran            | neters to understand the ADC Performance                  | 11 |  |

|    |                                                            | 2.2.1.           | Terms                                                     | 11 |  |

|    |                                                            | 2.2.2.           | Dynamic Characteristics                                   | 12 |  |

|    |                                                            | 2.2.3.           | Static Characteristics                                    | 13 |  |

|    |                                                            | 2.2.4.           | Figure-of-merit (FoM)                                     | 17 |  |

| 3. | Pro                                                        | $\mathbf{posed}$ | Asynchronous SAR logic                                    | 18 |  |

|    | 3.1.                                                       | SAR              | Logic Architecture                                        | 20 |  |

|    |                                                            | 3.1.1.           | Conventional SAR Logic                                    | 20 |  |

|    |                                                            | 3.1.2.           | Proposed Asynchronous SAR Logic                           | 21 |  |

|    | 3.2.                                                       | Simu             | Itaneous-Switching Noise (SSN)                            | 24 |  |

|    |                                                            | 3.2.1.           | Parameters defining Ground bounce and $V_{cc}$ bounce     | 26 |  |

|    |                                                            | 3.2.2.           | Factors influencing Ground bounce and $V_{\rm cc}$ bounce | 26 |  |

|    |                                                            |                  | 3.2.2.1. Effect of Capacitive load                        | 26 |  |

|    |                                                            |                  | 3.2.2.2. Effect of Output Slew rate                       | 27 |  |

|    |                                                            | 3.2.3.           | Techniques to overcome SSN                                | 27 |  |

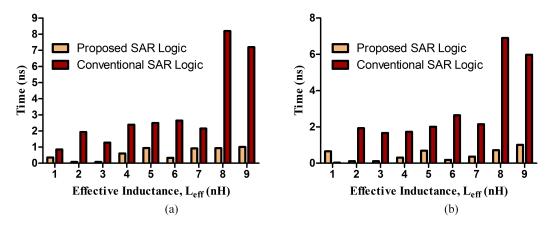

|    |                                                             | 3.2.4.  | Comparison of SSN on Conventional and Proposed SAR logic          | 29  |  |

|----|-------------------------------------------------------------|---------|-------------------------------------------------------------------|-----|--|

|    | 3.3.                                                        | Resul   | ts                                                                | 32  |  |

| 4. | Single Channel SAR-Assisted Pipeline ADC with a Novel Over- |         |                                                                   |     |  |

|    | shoo                                                        | ot Red  | uction Technique                                                  | 44  |  |

|    | 4.1.                                                        | A No    | vel Technique to Minimize Overshoot in ZCBC                       | 45  |  |

|    |                                                             | 4.1.1.  | Differential Zero-Crossing-Based Circuit                          | 45  |  |

|    |                                                             |         | 4.1.1.1. Conventional Zero-Crossing-Based Circuit (ZCBC) $\ldots$ | 45  |  |

|    |                                                             | 4.1.2.  | Proposed Differential Zero-Crossing-Based Circuit (ZCBC) $\dots$  | 47  |  |

|    |                                                             |         | 4.1.2.1. Proposed Zero-Crossing-Based Circuit (ZCBC)              | 47  |  |

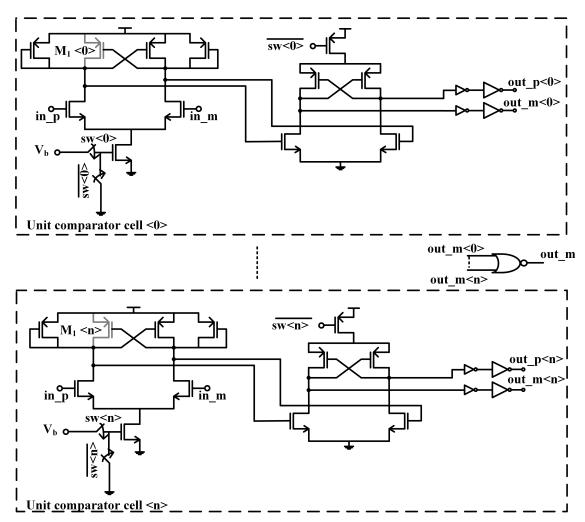

|    |                                                             |         | 4.1.2.2. Comparator Design                                        | 49  |  |

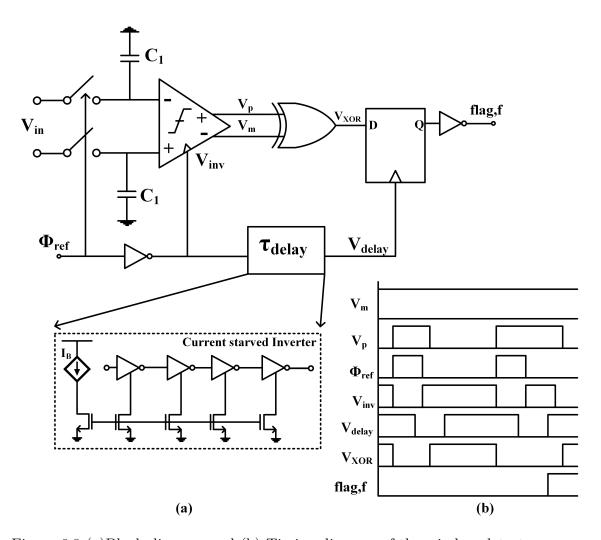

|    |                                                             |         | 4.1.2.3. Zero-Crossing Detector (ZCD)                             | 50  |  |

|    |                                                             |         | 4.1.2.4. Manual Current Calibration                               | 51  |  |

|    |                                                             | 4.1.3.  | Post-Layout Simulation Results                                    | 52  |  |

| 5. | 2-bi                                                        | t/cycle | e sub-radix SAR-Assisted Pipeline ADC with an Im-                 |     |  |

|    |                                                             | , -     | vershoot Reduction Technique                                      | 57  |  |

|    | _                                                           |         | cycle SAR ADC based on V <sub>cm</sub> technique                  | 57  |  |

|    |                                                             |         | Error Sources                                                     | 64  |  |

|    |                                                             |         | 5.1.1.1. Static Error                                             | 64  |  |

|    |                                                             |         | 5.1.1.2. Dynamic Error                                            | 66  |  |

|    |                                                             | 5.1.2.  | Architecture of the Single-Channel SAR-Assisted                   |     |  |

|    |                                                             |         | Pipeline ADC                                                      | 67  |  |

|    |                                                             | 5.1.3.  | Post-layout and Simulation Results                                | 68  |  |

|    | 5.2.                                                        | Impro   | oved Version of the Overshoot Reduction Technique                 | 70  |  |

|    |                                                             | 5.2.1.  | Overshoot Reduction Technique                                     | 70  |  |

|    |                                                             |         | 5.2.1.1. Coarse Threshold Tuning                                  | 71  |  |

|    |                                                             |         | 5.2.1.2. Fine Threshold Tuning                                    | 72  |  |

|    |                                                             | 5.2.2.  | Results                                                           | 74  |  |

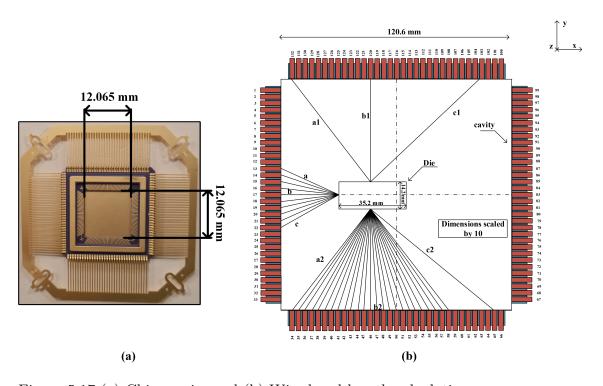

|    |                                                             | 5.2.3.  | Measurement Challenges                                            | 79  |  |

|    |                                                             |         | 5.2.3.1. Wire bond reduction techniques                           | 81  |  |

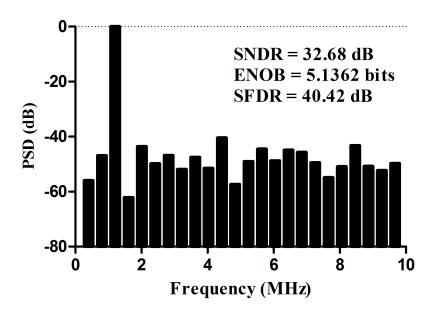

|    |                                                             | 5.2.4.  | Measurement Results                                               | 85  |  |

| 6. | 4-ch                                                        | annel   | Time-Interleaved SAR-Assisted Pipeline ADC                        | 92  |  |

|    | 6.1.                                                        | Time    | -Interleaving                                                     | 92  |  |

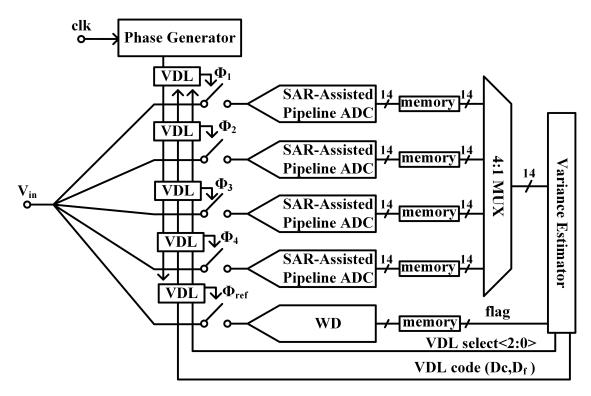

|    | 6.2.                                                        |         | tecture of the Time-Interleaved ADC                               | 98  |  |

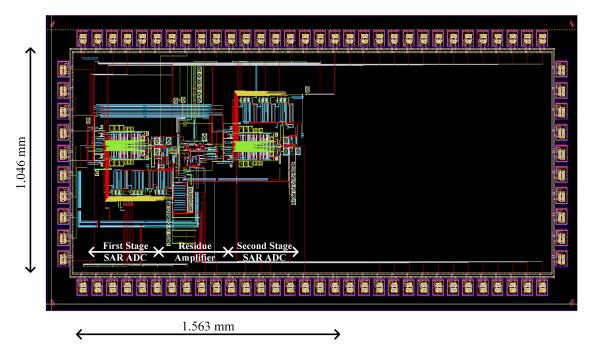

|    | 6.3.                                                        |         | Layout Results                                                    |     |  |

| 7. | CO                                                          | NCLU    | SION AND FUTURE WORK                                              | 104 |  |

| ΒI | BLI                                                         | OGR.A   | PHY                                                               | 108 |  |

# LIST OF TABLES

| Table 3.1.                                                                                                                        | Comparison of the SAR logic to recent works                     | 42  |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|

| Table 3.2.                                                                                                                        | Measured Performance Summary                                    | 43  |

| Table 4.1                                                                                                                         | Comparison of Overshoot voltage and Percentage Reduction of     |     |

|                                                                                                                                   | shoot Time after fine-tuning the threshold for different Corner |     |

|                                                                                                                                   | S                                                               | 54  |

|                                                                                                                                   | Post-Layout Performance Summary                                 | 55  |

|                                                                                                                                   | Performance Summary and Comparison                              | 56  |

|                                                                                                                                   | <u> </u>                                                        | -0  |

| Table 5.1.                                                                                                                        | Post-Layout Performance Summary                                 | 70  |

| Table 5.2.                                                                                                                        | Comparison of Overshoot Voltage and Time, and Percent-          |     |

| age R                                                                                                                             | Reduction of Overshoot Time and Voltage after fine-tuning the   |     |

| Table 5.2. Comparison of Overshoot Voltage and Time, and Percentage Reduction of Overshoot Time and Voltage after fine-tuning the |                                                                 | 76  |

| Table 5.3.                                                                                                                        | Post-layout Performance Summary                                 | 76  |

| Table 5.4.                                                                                                                        | Performance Summary and Comparison                              | 78  |

| Table 6.1.                                                                                                                        | Post-Layout Performance Summary                                 | 103 |

# LIST OF FIGURES

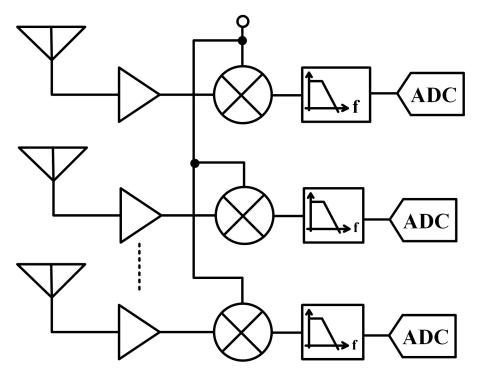

| Figure 1.1.                                   | Block Diagram of a Digital MIMO Receiver                           | 2  |

|-----------------------------------------------|--------------------------------------------------------------------|----|

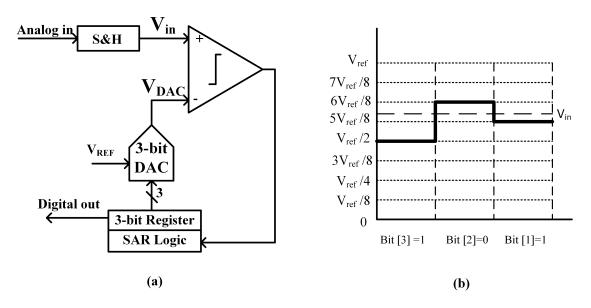

| Figure 2.1.                                   | 3-bit SAR ADC (a) Block Diagram (b) Working                        | 7  |

| Figure 2.2.                                   | 3-bit Vcm-based SAR ADC                                            | 7  |

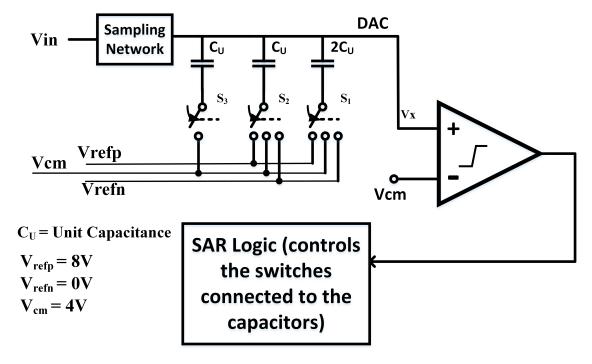

| Figure 2.3.                                   | (a) Architecture (b) Example of a 2-stage Pipeline ADC             | 10 |

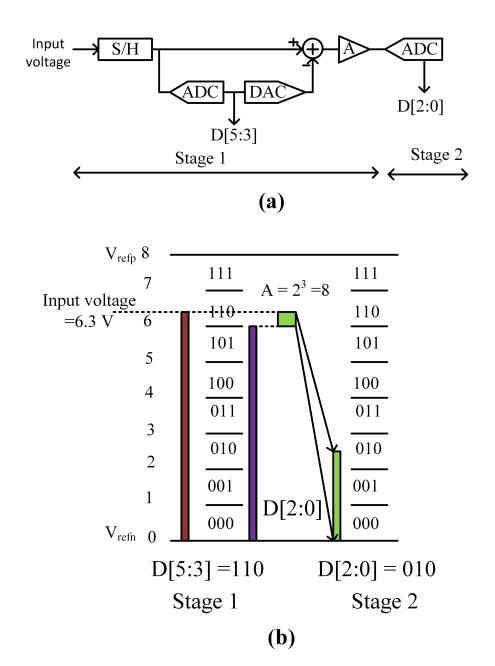

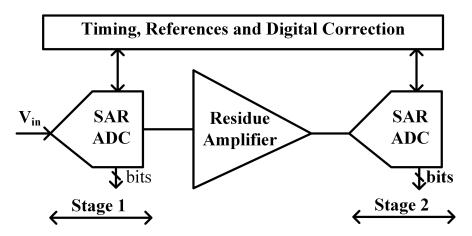

| Figure 2.4.                                   | Block diagram of a Two-stage SAR-Assisted Pipeline ADC $\dots$     | 11 |

| Figure 2.5.                                   | Compensated Ideal Transfer Function                                | 14 |

| Figure 2.6.                                   | Positive and Negative Offset error                                 | 14 |

| Figure 2.7.                                   | Positive and Negative Gain error                                   | 15 |

| Figure 2.8.                                   | ADC Transfer Function with DNL Error                               | 16 |

| Figure 2.9.                                   | ADC Transfer Function with INL Error                               | 16 |

| Figure 3.1.                                   | Block diagram of a N-bit SAR ADC                                   | 18 |

| Figure 3.2.                                   | (a) Block diagram (Sadollahi, Hamashita, Sobue & Temes             |    |

| (2018)                                        | ) and (b) Timing diagram of a conventional synchronous SAR         |    |

| Logic.                                        |                                                                    | 20 |

| Figure 3.3.                                   | Schematic of a 6-bit V <sub>cm</sub> -based SAR ADC                | 22 |

| Figure 3.4.                                   | (a) Block diagram and (b) Timing diagram of the proposed           |    |

| asynchronous SAR logic (c) Schematic of latch |                                                                    |    |

| Figure 3.5.                                   | An Inverter switching with Parasitic Inductance                    | 24 |

| Figure 3.6.                                   | $V_{cc}$ bounce plot based on the circuit in Fig. 3.5              | 25 |

| Figure 3.7.                                   | Ground bounce plot based on the circuit in Fig. 3.5                | 25 |

| Figure 3.8.                                   | Parameters defining Ground bounce and $V_{cc}$ bounce              | 26 |

| Figure 3.9.                                   | (a) Typical NMOS layout (b) Serpentine NMOS layout                 | 28 |

| Figure 3.10.                                  | Distributed transistor                                             | 28 |

| Figure 3.11.                                  | (a) Block diagram of the implemented conventional SAR Logic        |    |

| (b) Sch                                       | nematic of the positive edge triggered D Flip-flop with SET and    |    |

| RESE                                          | $\Gamma$ (c) Schematic of the NAND gate (d) Waveform for clock and |    |

| compa                                         | rator pulse                                                        | 29 |

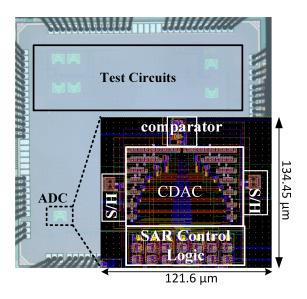

| Figure 3.12.                                  | Chip micrograph with zoomed-in layout view                         | 32 |

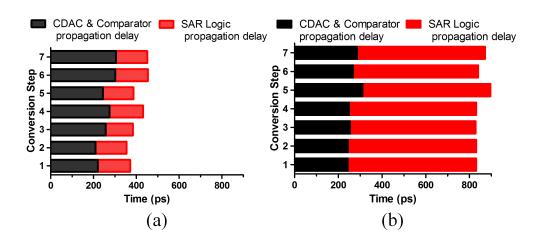

| Figure 3.13. Simulated propagation delay for the (a) Proposed and (b)                |    |

|--------------------------------------------------------------------------------------|----|

| Conventional SAR logic for every conversion cycle                                    | 32 |

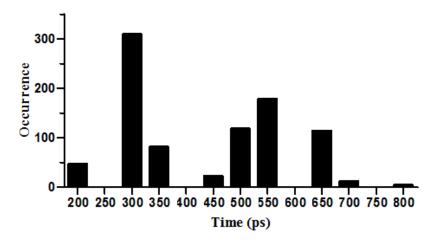

| Figure 3.14. Histogram plot showing the measured propagation delay for               |    |

| one conversion of the SAR ADC                                                        | 33 |

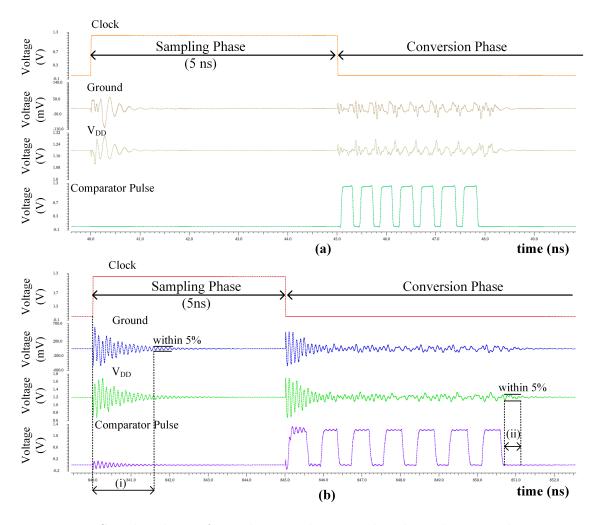

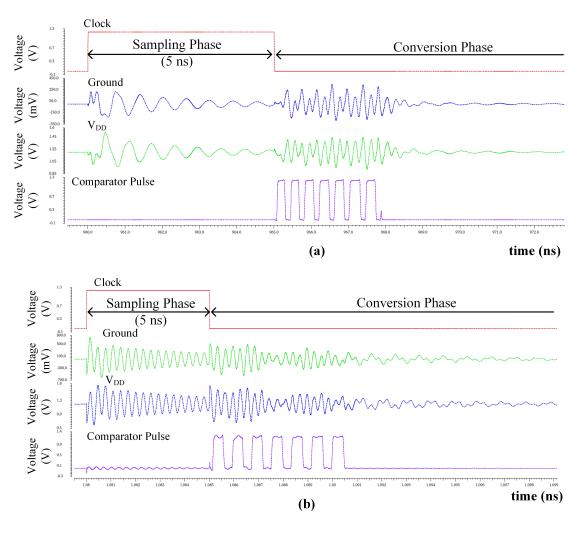

| Figure 3.15. Simulated waveform showing the ground and $V_{\rm cc}$ bounce when      |    |

| a 1 nH inductor is connected to the power and ground supply of the                   |    |

| SAR Logic for the (a) proposed and (b) conventional SAR logic                        | 34 |

| Figure 3.16. Simulated waveform showing the ground and $V_{cc}$ bounce when          |    |

| a 9 nH inductor is connected to the power and ground supply of the                   |    |

| SAR Logic for the (a) proposed and (b) conventional SAR logic                        | 35 |

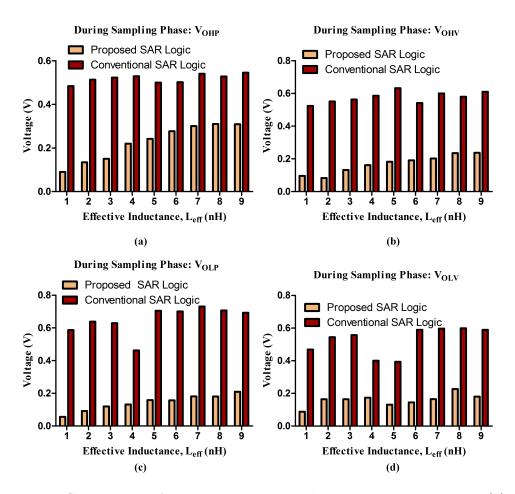

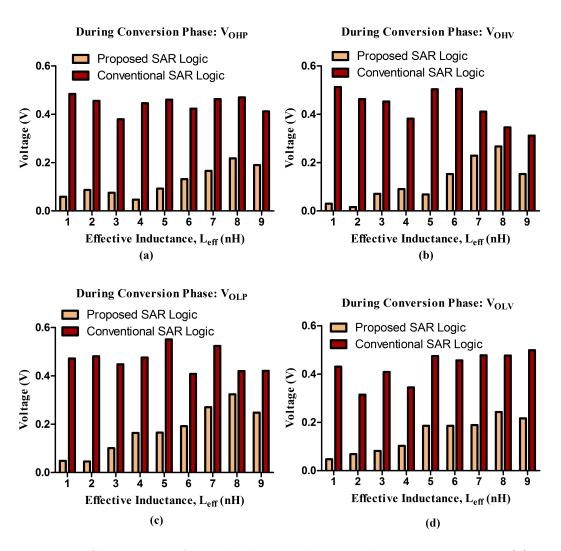

| Figure 3.17. Comparison of simulated ground and $V_{cc}$ bounce parameters:          |    |

| (a) $V_{OHP}$ and (b) $V_{OHV}$ (c) $V_{OLP}$ and (d) $V_{OLV}$ for conventional and |    |

| proposed SAR logic during the sampling phase                                         | 36 |

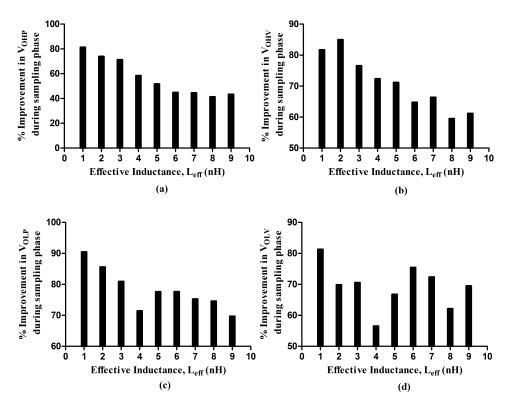

| Figure 3.18. Percentage improvement of the proposed SAR logic w.r.t the              |    |

| conventional SAR logic in terms of the SSN parameters during the                     |    |

| sampling phase                                                                       | 37 |

| Figure 3.19. Comparison of simulated ground and $V_{\rm cc}$ bounce parameters:      |    |

| (a) $V_{OHP}$ and (b) $V_{OHV}$ (c) $V_{OLP}$ and (d) $V_{OLV}$ for conventional and |    |

| proposed SAR logic during the conversion phase                                       | 38 |

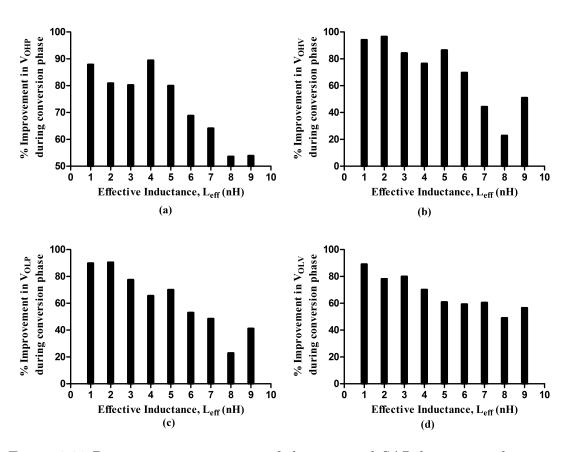

| Figure 3.20. Percentage improvement of the proposed SAR logic w.r.t the              |    |

| conventional SAR logic in terms of the SSN parameters during the                     |    |

| conversion phase                                                                     | 39 |

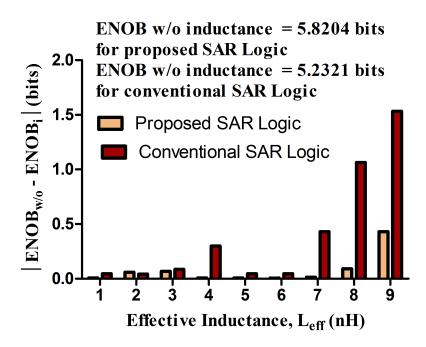

| Figure 3.21. Difference in ENOB for different effective inductance ( $L_{\rm eff}$ ) |    |

| values w.r.t to the ENOB without inductance for the proposed and                     |    |

| conventional SAR logic                                                               | 40 |

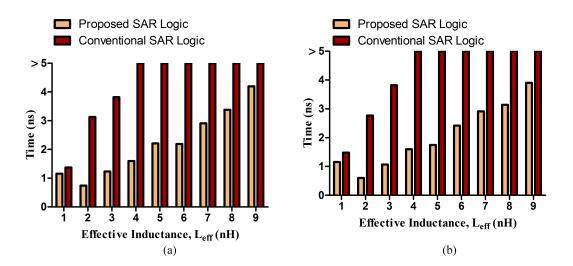

| Figure 3.22. Settling time for the (a) power supply and (b) ground during            |    |

| the sampling phase                                                                   | 41 |

| Figure 3.23. Settling time for the (a) power supply and (b) ground during            |    |

| the conversion phase                                                                 | 41 |

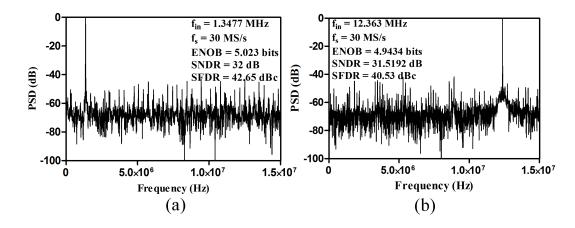

| Figure 3.24. Measured spectrum for an input frequency of (a) $1.3477~\mathrm{MHz}$   |    |

| and (b) 12.363 MHz sampled at 30 MS/s                                                | 42 |

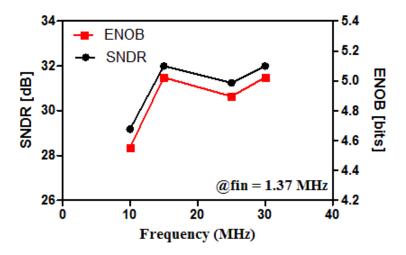

| Figure 3.25. Measured SNDR and ENOB versus sampling frequency $\ldots\ldots$         | 42 |

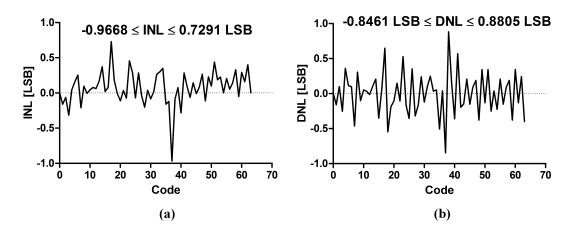

| Figure 3.26. Measured INL and DNL                                                    | 43 |

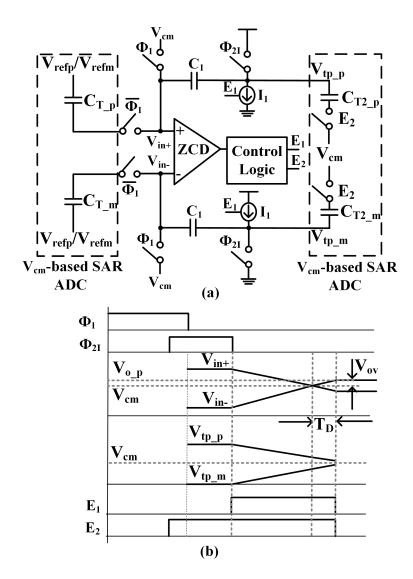

| Figure 4.1. (a) Block Diagram and (b) Timing diagram of a Conventional               |    |

| Zero-Crossing-Based Circuit (ZCBC)                                                   | 46 |

| Figure 4.2. (a) Block Diagram and (b) Timing Diagram of the Proposed                 |    |

| ZCBC                                                                                 | 47 |

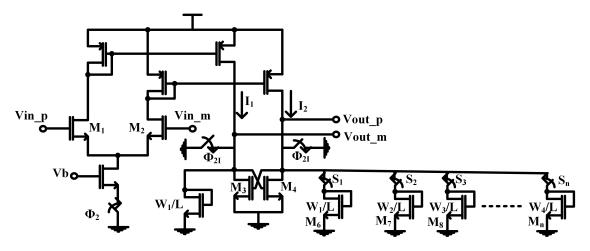

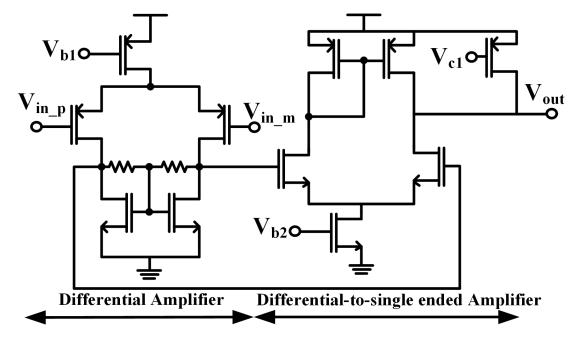

| Figure 4.3. Schematic of the Comparator (Comp1)                                      | 50 |

| Figure 4.4. Schematic of the ZCD                                                 | 5 |

|----------------------------------------------------------------------------------|---|

| Figure 4.5. Manual Current Calibration                                           | 5 |

| Figure 4.6. Layout of the 8b radix-1.793 $V_{cm}$ -based SAR-assisted two-       |   |

| stage pipeline ADC                                                               | 5 |

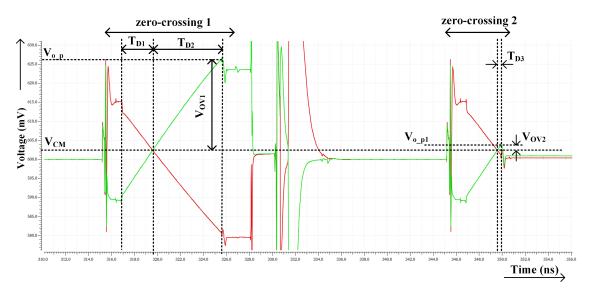

| Figure 4.7. (a) Simulation waveform of the proposed ZCD and (b) zoom-            |   |

| view of the zero-crossing detection in the tt corner case                        | 5 |

| Figure 4.8. Post-layout simulation at an input frequency of (a) 520.83 kHz       |   |

| and (b) at near Nyquist frequency of 7.5521 MHz                                  | 5 |

| Figure 4.9. Post-layout (a) SNDR and SFDR (b) and ENOB for different             |   |

| input frequencies at a sampling frequency of 16 MS/s                             | 5 |

| Figure 4.10. INL and DNL                                                         | 5 |

| Figure 5.1. Schematic of a 7-bit 2-bit/cycle SAR ADC based on $V_{\rm cm}$ tech- |   |

| nique                                                                            | 5 |

| Figure 5.2. (a) Schematic of the 7-bit 2-bit/cycle SAR ADC based on $V_{\rm cm}$ |   |

| technique (b) Conversion algorithm in terms of digital output (c) Im-            |   |

| plementation algorithm w.r.t $V_{inp}$ (d) Implementation algorithm w.r.t        |   |

| $V_{inm}$ (e) Switch connection to the positive DAC (f) Switch connection        |   |

| to the negative DAC based                                                        | 5 |

| Figure 5.3. (a) Block diagram of the comparator with calibration (b)             |   |

| Schematic of the comparator (c) Timing diagram of the comparator                 |   |

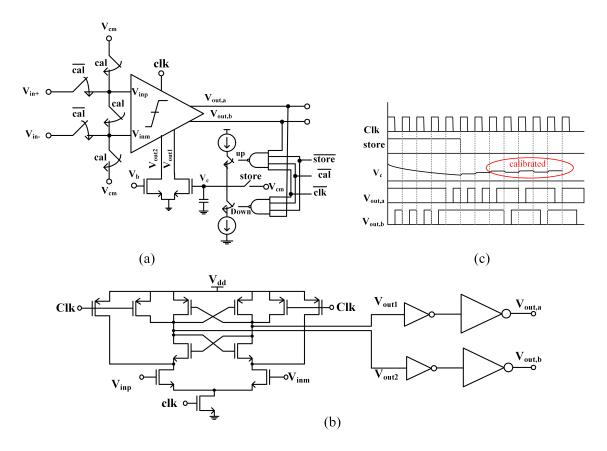

| with calibration                                                                 | 6 |

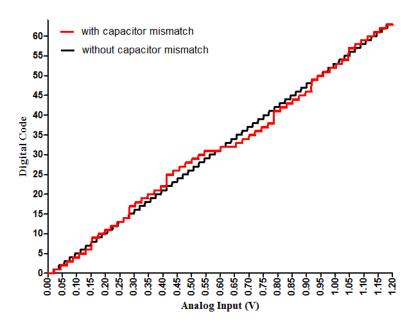

| Figure 5.4. Transfer curve showing with and without capacitor mismatch           | 6 |

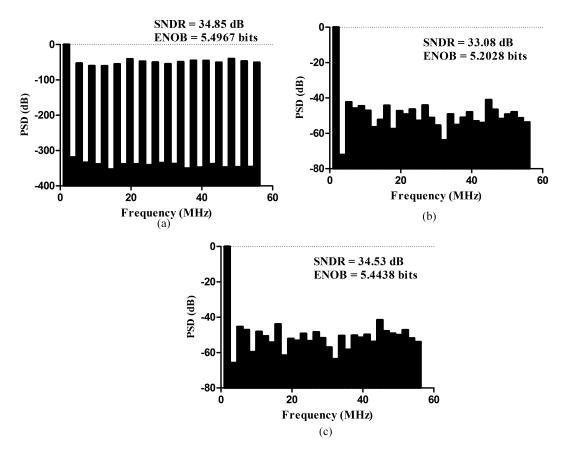

| Figure 5.5. FFT plot of (a) an ideal (b) with capacitor mismatch (c) cal-        |   |

| ibrated in the presence of capacitor mismatch for a $5.4967$ -bits $1.92$        |   |

| ${\rm radix}\ {\rm V_{cm}}\ {\rm based}\ {\rm SAR}\ {\rm ADC}$                   | 6 |

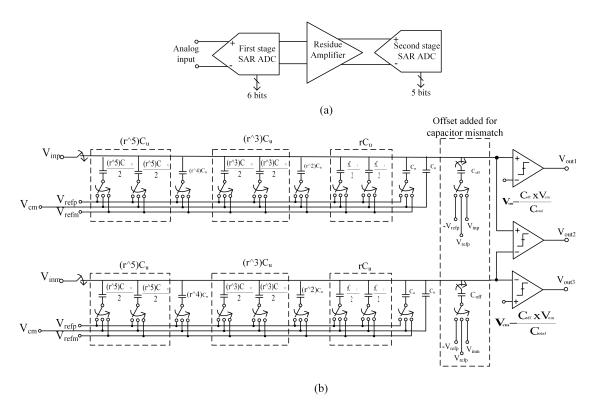

| Figure 5.6. (a) Block diagram of the Single-Channel SAR-Assisted                 |   |

| Pipeline ADC (b) Schematic of the SAR ADC                                        | 6 |

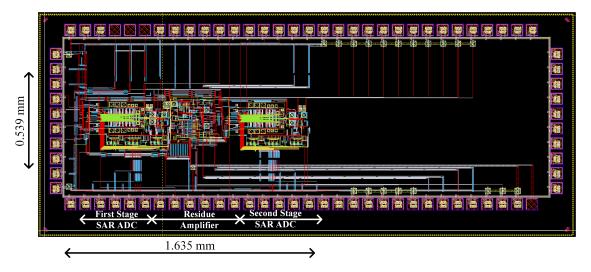

| Figure 5.7. Layout of the 10-bit radix 1.97 $V_{\rm cm}$ based SAR-assisted two- |   |

| stage pipeline ADC                                                               | 6 |

| Figure 5.8. Post-layout simulation at an input frequency of (a) 1.3393           |   |

| MHz and (b) at near Nyquist frequency of 10.268 MHz                              | 6 |

| Figure 5.9. Post-layout (a) SNDR and SFDR (b) and ENOB for different             |   |

| input frequencies at a sampling frequency of 28.571 MS/s                         | 6 |

| Figure 5.10. Post-layout INL and DNL                                             | 6 |

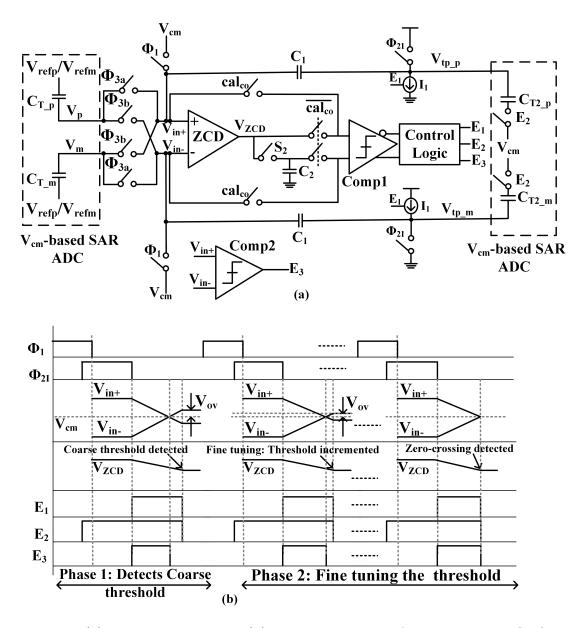

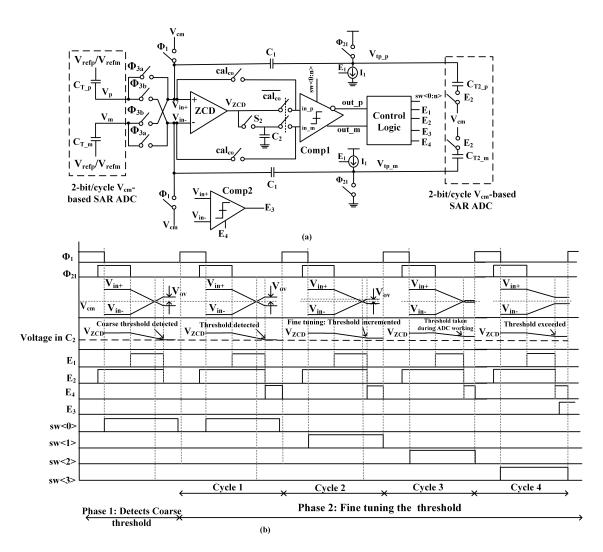

| Figure 5.11. (a) Block Diagram (b) Timing diagram of the Improved Over-          |   |

| shoot Reduction Technique                                                        | 7 |

| Figure 5.12. Schematic of the comparator (COMP1)                                 | 7 |

| Figure 5.13. Layout of the 10-bit sub-radix V <sub>cm</sub> based SAR-assisted two- | _ |

|-------------------------------------------------------------------------------------|---|

| stage pipeline ADC                                                                  | 7 |

| Figure 5.14. Simulation waveform of the improved overshoot reduction                | _ |

| technique in the tt corner case                                                     | 7 |

| Figure 5.15. Post-layout simulation at an input frequency of (a) 1.171875           | _ |

| MHz and (b) at near Nyquist frequency of 11.328125 MHz                              | 7 |

| Figure 5.16. Post-layout (a) SNDR and SFDR (b) and ENOB for different               | _ |

| input frequencies at a sampling frequency of 25 MS/s                                | 7 |

| Figure 5.17. (a) Chip carrier and (b) Wire bond length calculation                  | 7 |

| Figure 5.18. Post-layout simulation with the inductance connected to each           |   |

| I/O pad due to the wire bond                                                        | 8 |

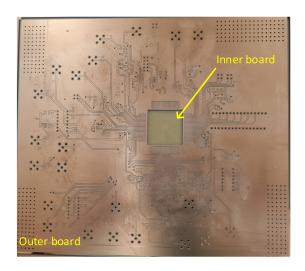

| Figure 5.19. 4-layer board fabricated for the single-channel ADC                    | 8 |

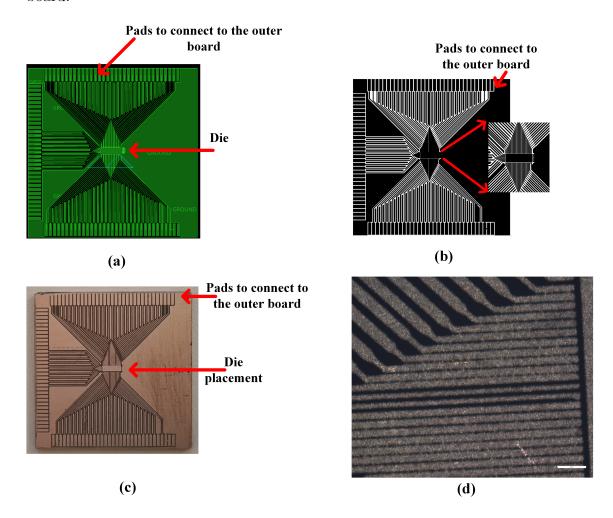

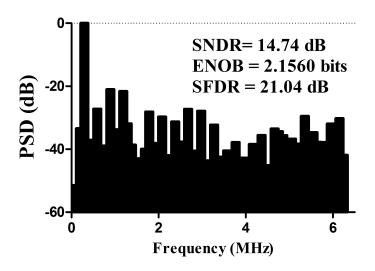

| Figure 5.20. (a) Mask of the inner board and (b) Board fabricated based             |   |

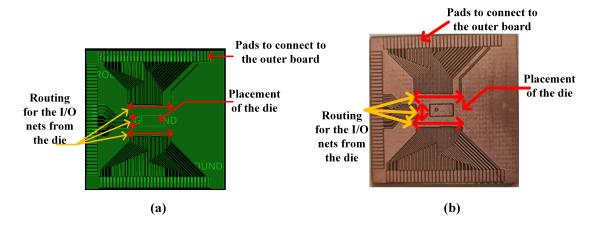

| on the mask                                                                         | 8 |

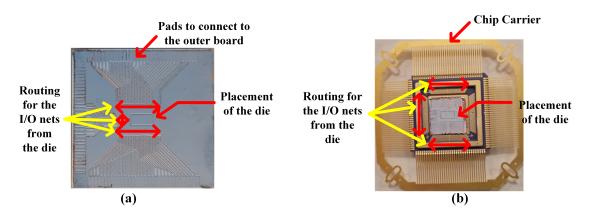

| Figure 5.21. Patterned Board after Al deposition (a) on the inner board             |   |

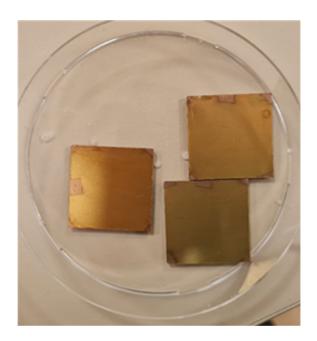

| and (b) inside the chip carrier                                                     | 8 |

| Figure 5.22. Sample coated initially with 20 nm Ni and then 200 nm of Au            | 8 |

| Figure 5.23. (a) Layout, (b) mask (c) patterned PCB and (d) zoomed-in               |   |

| view of the patterned PCB for the inner board using flip chip                       | 8 |

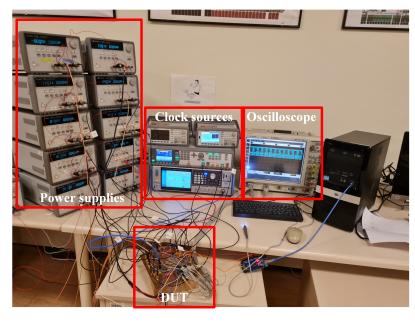

| Figure 5.24. (a) Measurement setup and (b) board for the Single-channel             |   |

| ADC                                                                                 | 8 |

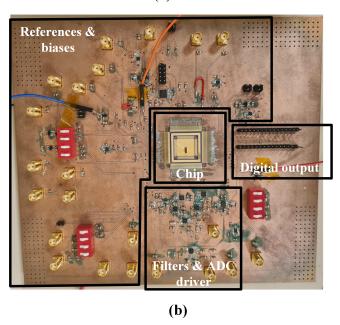

| Figure 5.25. FFT plot for the Single-channel ADC                                    | 8 |

| Figure 5.26. (a) VCM signal for the first stage and (b) its zoomed-view $\dots$     | 8 |

| Figure 5.27. (a) Vrefp signal for the first stage and (b) its zoomed-view $ \dots $ | 8 |

| Figure 5.28. (a) Vrefn signal for the first stage and (b) its zoomed-view $ \dots $ | 9 |

| Figure 5.29. FFT plot (a) without the effect from inductance and board,             |   |

| (b) with the effect of the inductance and (c) with the effect of the                |   |

| inductance and from the board                                                       | 9 |

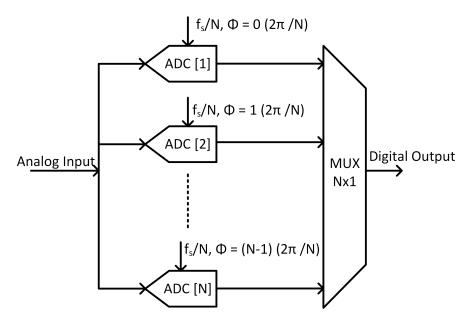

| Figure 6.1. Block Diagram of Time-interleaving                                      | 9 |

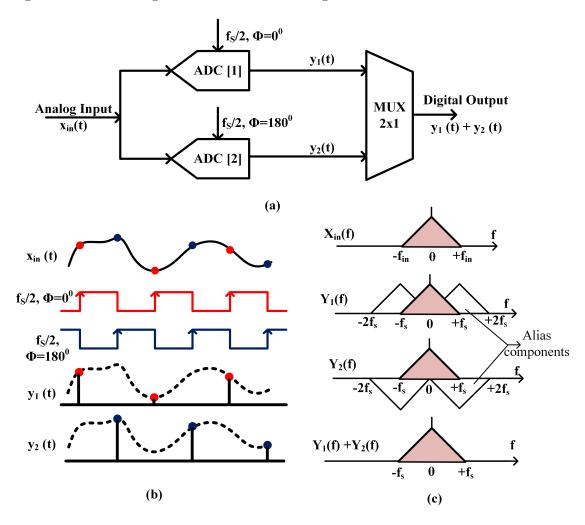

| Figure 6.2. (a) Block Diagram (b) Timing Diagram (c) Frequency Re-                  |   |

| sponse of 2-channel Time-interleaving                                               | 9 |

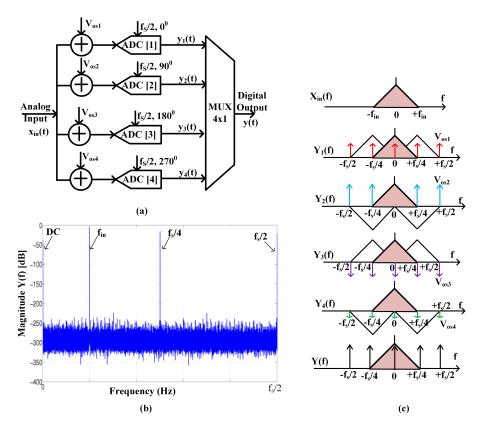

| Figure 6.3. (a) Block Diagram (b) Frequency Response (c) Output Spec-               | , |

| trum due to offset error in a 4-channel Time-interleaving                           | 9 |

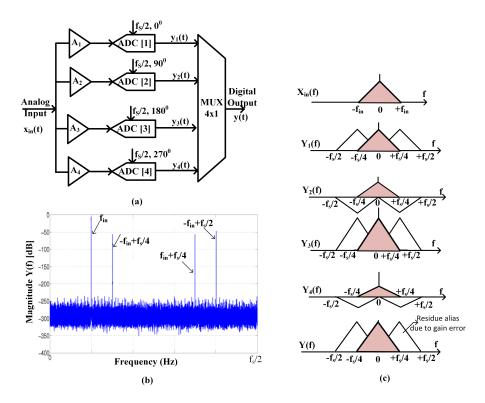

| Figure 6.4. (a) Block Diagram (b) Frequency Response (c) Output Spec-               | J |

| trum due to gain error in a 4-channel Time-interleaving                             | 9 |

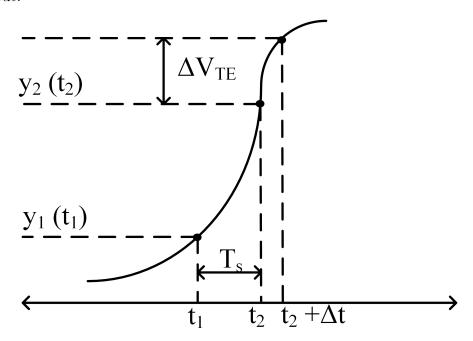

| Figure 6.5. Timing Error due to error in sampling the input signal                  | 9 |

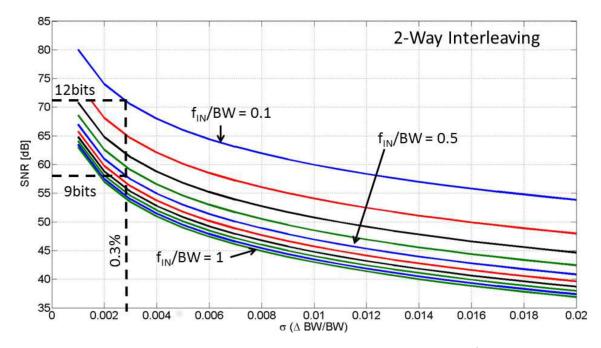

| Figure 6.6. SNR Vs Bandwidth Mismatch for 2-channel TI ADC (Kuro-                   | J |

| sawa, Kobayashi, Maruyama, Sugawara & Kobayashi (2001))                             | 9 |

| Sana, Itobarasin, managamia, Sagamana & Itobarasin (2001)                           | J |

| 98    |

|-------|

|       |

| 99    |

|       |

| 00    |

| 01    |

| 01    |

| 02    |

|       |

| .02   |

|       |

| .03   |

| . ( ) |

#### LIST OF ABBREVIATIONS

3GPP: Third Generation Partnership Project

ADC: Analog-to-Digital Converter

CDAC: Capacitive Digital-to-Analog

CMOS: Complementary Metal-Oxide Semiconductor

CML: Current Mode Logic

DAC: Digital-to-Analog Converter

DNL: Differential Non-linearity

DSPs — Digital Signal Processors

DVB-H: Digital Video Broadcasting - Handheld

DVB-T: Digital Video Broadcasting - Terrestrial

ENOB: Effective Number Of Bits

FFT: Fast Fourier Transform

FoM<sub>W</sub>: Walden Figure of Merit

FoM<sub>S</sub>: Schreier Figure of Merit

IEEE: Institute of Electrical and Electronics Engineers

IL: Interleaving Spurs

IMT-2020: International Mobile Telecommunication - 2020

INL: Integral Non-linearity

ITU-R: International Telecommunication Union Radiocommunication Sector

LNA: Low-Noise Amplifier

LSB: Least Significant Bit

MIMO: Multiple-Input Multiple-Output

MOSFET: Metal-Oxide-Semiconductor Field-Effect transistor

mmWave: Millimeter Wave MSB: Most Significant Bit

NR: New Radio

$\mathrm{OEC^{TM}}$ : Output Edge Control

OSR: Oversampling Ratio

PCB: Printed Circuit Board

PVT: Process Voltage Temperature

SAR: Successive Approximation Register

SFDR : Spurious Free Dynamic Range

SiGe: Silicon Germanium

SNDR : Signal to Noise and Distortion Ratio

SNR : Signal to Noise Ratio

SSN: Simultaneous-Switching Noise

THD: Total Harmonic Distortion

TI : Time Interleaved V2V: Vehicle-to-Vehicle

$\mathsf{VDL}:$  Variable Delay Line

VML : Voltage Mode Logic

WD : window Detector

${\it ZCBCs}: {\it Zero-Crossing-Based Circuits}$

${\sf ZCD}: {\sf Zero\text{-}Crossing\ Detector}$

#### 1. Introduction

#### 1.1 Motivation

The 5G requirements specified by the International Mobile Telecommunication - 2020 (IMT-2020) issued by the International Telecommunication Union Radio communication Sector (ITU-R) demand a downlink peak data rate of 20 Gbit/s, an uplink peak data rate of 10 Gbit/s, and a latency of 1 ms (ITU (2021)). The Third Generation Partnership Project (3GPP) has specified two frequency ranges for 5G New Radio (NR), which are sub-6 GHz and 24-100 GHz. In the millimeter wave (mmWave) communication system (i.e. in between 30 and 300 GHz), the overall loss in the mmWave system is larger than the microwave frequency band for a point-to-point link. mmWave multiple-input multiple- output (MIMO) provides a means to solve the attenuation loss by using large antenna array as the size of the antenna is inversely proportional to the frequency. Due to the large antenna array, higher throughput can be achieved by the use of spatial multiplexing. Moreover, due to the large spectrum in the mmWave band, this gives rise to a tremendous increase in the data rate paving the way for applications like WiGig, V2V communication and so on.

Fig.1.1 shows the architecture of a MIMO receiver that contains multiple antennas. The received signal is passed through the LNA and then down-converted by the mixer and passed through a low pass filter and finally, to the ADC to be converted to a digital format for the DSPs. The motivation of the Ph.D. thesis is to design the ADC system that will be integrated along with the RF block to form a single monolithic IC to function as the MIMO receiver that will improve the signal integrity between the blocks and hence, improve the performance of the complete system. The ADC specification attained for the system can be understood by the following example. For instance, for a full duplex WiFi radio, the bandwidth allocated is 80

Figure 1.1 Block Diagram of a Digital MIMO Receiver

MHz. The transmit power is 20 dBm with the receiver noise figure to be 5 dB. The noise floor can be calculated as  $-174 + 10\log(80 \times 10^6) = -90$  dBm. Hence, a 110 dB of overall self-interference cancellation is required to push it below the noise floor. If a 50 dB digital cancellation is considered then a 12-bit ( $\approx 70$  dB dynamic range) ADC can be used and the remaining 60 dB cancelled by the RF and antenna (Kalyoncu (2019)). By the use of a notch filter before the ADC (Golabighezelahmad, Klumperink & Nauta (2020); Kim, Joshi, Thomas, Ha, Larson & Cauwenberghs (2016); Moon, Kim, Kam, Jee, Choi & Lee (2019)), the dynamic range of the ADC can be reduced. Hence, the specification of the ADC is an 8-12 bit resolution ADC with a sampling rate of 100 MS/s is taken.

Data converters are divided into two categories: Oversampling converters and Nyquist-rate data converters. Nyquist-rate data converters operate for input signals close to the bandwidth of  $f_{\rm s}/2$ , and mostly operate at a speed that is limited by the architecture and process. The most commonly used Nyquist-rate converters are the flash ADC, SAR ADC, and pipeline ADC. Oversampling ADCs are used for a limited bandwidth signal with a high sampling rate and are defined by the oversampling ratio (OSR). OSR is defined as the ratio between sampling frequency to the Nyquist frequency i.e.  $f_{\rm s}/2f_{\rm b}$ , where  $f_{\rm b}$  is the highest input frequency, and  $f_{\rm s}$  is the sampling frequency. The advantage of oversampling ADC is that it attains high resolution by using noise shaping techniques along with oversampling. The disadvantage of oversampling ADCs is that it requires a high-frequency clock and

also for the DSPs thereby increasing the hardware complexity and making it cost-in-efficient. Based on the specification of the ADC required for the MIMO system, a medium-high resolution, medium speed, and low power ADC are required. Among the different Nyquist-rate converters, SAR ADC has the advantage of low power but low speed, pipeline ADCs have high speed but low power, and flash ADC has high speed but power-inefficient. Hence, combining the advantage of SAR ADC and pipeline ADC, this thesis starts the ADC design with a SAR-assisted pipeline ADC.

## 1.2 Technical Challenges and Solutions

The intention of the thesis is to design an 8-12 bit ADC with a sampling speed of 100 MS/s for the monolithic MIMO receiver IC. To achieve low power, the MOSFETs of the technology are used. However, the MOSFETs have lower  $f_T$  compared to the HBT of the technology. Hence, the intention of the ADC design is to increase the speed. For a given technology node, the power of the ADC increases with the sampling frequency until a certain point, based on the technology node. After this point, the power increases at a much faster rate as the sampling frequency increases, and the normalized power efficiency (P/ $f_s$ ) starts to degrade (Wei, Zhang, Datta Sahoo & Razavi (2013)). Hence, the single-channel ADC is designed until the point where the power and speed increase in a linear fashion. Then, time-interleaving will be used to increase the speed and keeps the transistor speed in the linear region of power and sampling speed.

## 1.3 Thesis Outline

The thesis intends to design an 8-12 bit resolution ADC with a speed of 100 MS/s with low power. Therefore, chapter 2 introduces SAR ADC and pipeline ADC. SAR ADC is used for its low power and pipeline ADC is used for its high speed. Combining the advantage of both of them gives the SAR-assisted pipeline architecture which is then explained in the chapter. Finally, the chapter concludes by illustrating the terms and parameters used to define the ADC.

Chapter 3 introduces a novel asynchronous SAR logic for the SAR ADC that was designed in the 8-metal CMOS process. The design was implemented by a former member of the group, and the analysis and measurements are done by the author of the thesis.

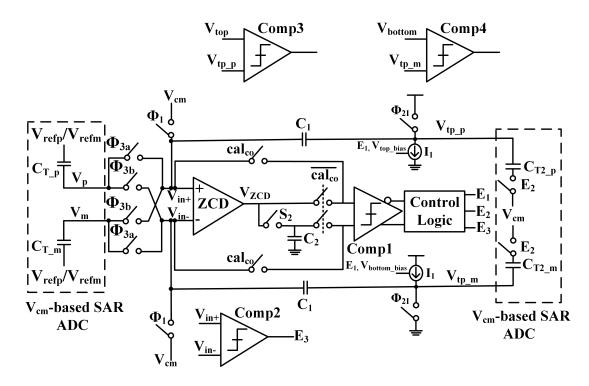

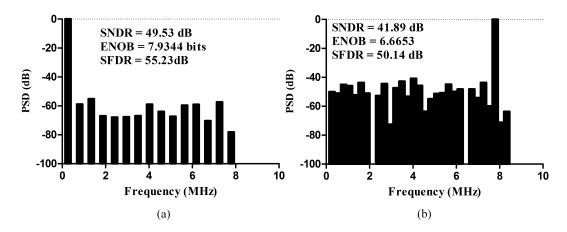

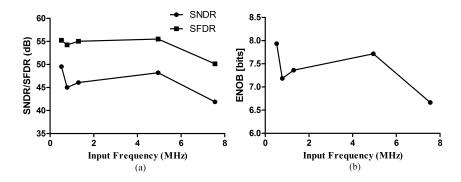

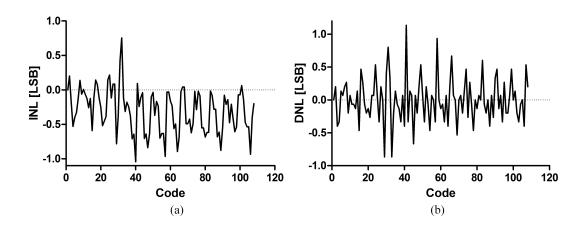

In chapter 4, the design of the single-channel  $V_{\rm cm}$ -based SAR-Assisted pipeline ADC is explained and designed in the 130 nm BiCMOS process. The SAR ADC uses the novel asynchronous SAR logic explained in chapter 3. In this chapter a novel overshoot reduction technique is described for the residue amplifier designed based on the zero-crossing-based circuit (ZCBC). The post-layout results of the SAR-assisted pipeline ADC achieves an ENOB of 7.9344 bits and 6.6653 bits that corresponds to an SNDR of 49.53 dB and 41.89 dB with an input frequency of 520.83 kHz and at a near Nyquist rate of 7.5521 MHz, respectively with a sampling frequency of 16 MS/s. The INL and DNL were attained as -1.043/0.75 LSB and -0.86/1.13 LSB, respectively. The Walden Figure of Merit (FOM<sub>W</sub>) at low frequency and at the Nyquist frequency was attained as 255 fJ/conversion-step and 615.77 fJ/conversion-step, respectively.

In chapter 4, the speed and resolution have not been met, hence, chapter 5 divides into two sections.

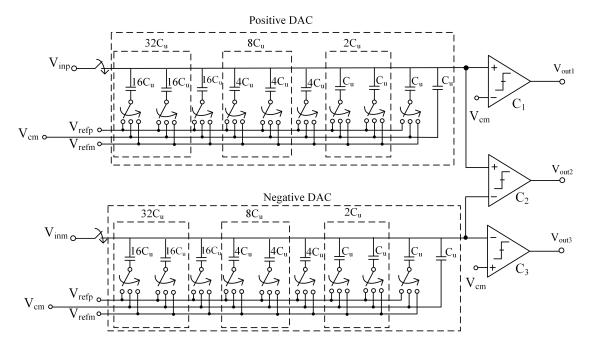

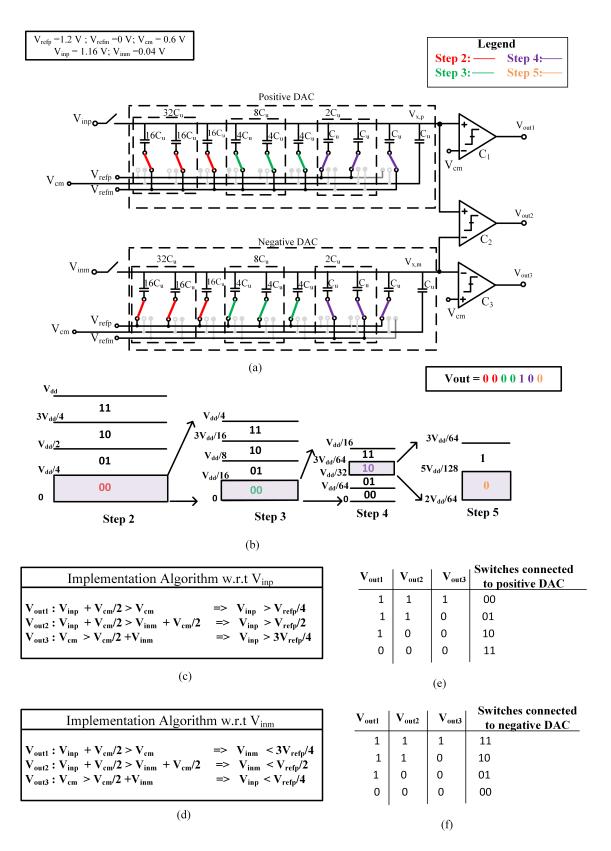

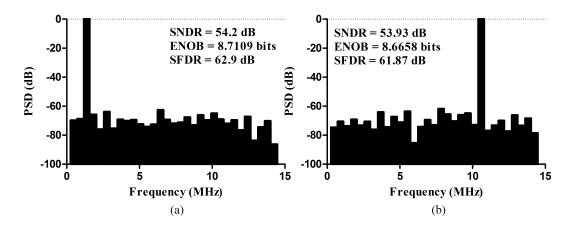

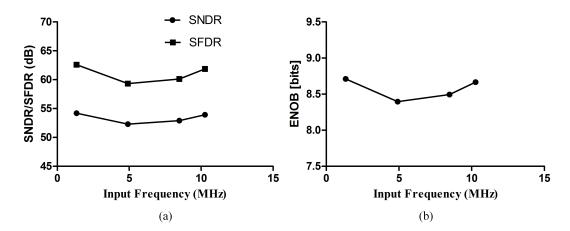

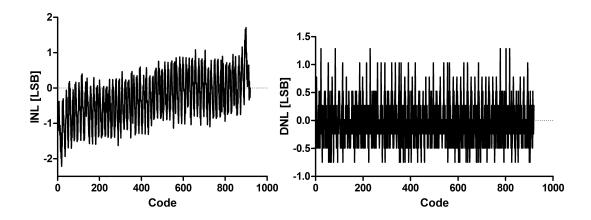

- Section 1: Section 1 describes the 2-bit/cycle SAR ADC and using the aforementioned architecture in the SAR ADC, a single-channel ADC is designed using a 2-bit/cycle sub-radix V<sub>cm</sub>-based SAR-assisted pipeline. The post-layout results of the SAR-assisted pipeline ADC achieves an ENOB of 8.7109 bits and 8.6658 bits that corresponds to an SNDR of 54.2 dB and 53.93 dB with an input frequency of 1.3393 MHz and at a near Nyquist rate of 10.268 MHz, respectively with a sampling frequency of 28.571 MS/s. The INL and DNL were attained as +1.7067/-2.2149 LSB and +1.2867/-0.7459 LSB, respectively. The Walden Figure of Merit (FOM<sub>W</sub>) at the Nyquist frequency was attained as 99.710 fJ/conversion-step.

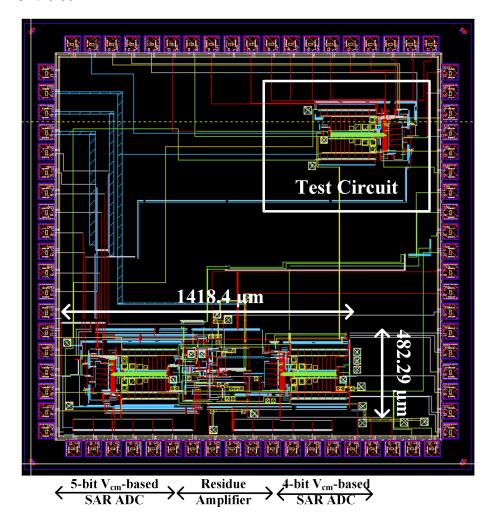

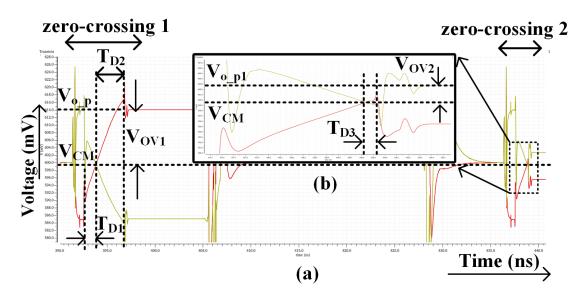

- Section 2: This section improves the overshoot reduction technique and is implemented in the 2-bit/cycle sub-radix V<sub>cm</sub>-based SAR-assisted pipeline. The post-layout results of the SAR-assisted pipeline ADC achieves an ENOB of 9.1216 bits and 9.1046 bits that corresponds to an SNDR of 56.67 dB and 56.57 dB with an input frequency of 1.171875 MHz and at a near Nyquist rate of 11.328125 MHz, respectively with a sampling frequency of 25 MS/s. The Walden Figure of Merit (FOM<sub>W</sub>) at the Nyquist frequency was attained as 589.7 fJ/conversion-step.

In chapter 5, to improve the speed, the single-channel SAR-assisted pipelined ADC was time-interleaved. A 4-channel TI architecture is presented in this chapter. The post-layout specification of the SAR-assisted pipeline ADC achieves an ENOB of 8.2355 bits and 8.0198 bits that corresponds to an SNDR of 51.34 dB and 50.04 dB with an input frequency of 1.5625 MHz and at a near Nyquist rate of 44.140625 MHz, respectively with a sampling frequency of 100 MS/s. The Walden Figure of Merit (FOM<sub>W</sub>) at the Nyquist frequency was attained as 2.4932 pJ/conversion-step.

Chapter 6 finally concludes the thesis with future works.

#### 2. SAR-Assisted Pipeline ADC and Parameters to understand the

#### **ADC** Performance

The most common Nyquist-rate date converters are the flash ADC, SAR ADC, and pipeline ADC. Flash ADC has high speed, however, it is less power efficient. In the case of SAR ADC, it is power-efficient but has slow speed, and pipeline ADC has high speed but is power hungry. Since, the ADC requirement is low power with a resolution of 8-12 with a sampling speed of 100 MS/s, the design of the ADC is based on a SAR-assisted pipeline ADC. This architecture uses the advantage of low power from SAR ADC and high speed from pipeline ADC. Hence, this chapter introduces the SAR ADC and then the pipeline ADC followed by which the SAR-assisted pipeline ADC is discussed. Finally, the parameters used to define the ADC are explained.

## 2.1 SAR-Assisted Pipeline ADC

#### 2.1.1 SAR ADC

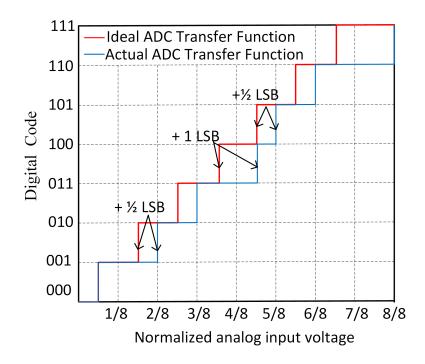

Successive-approximation register (SAR) ADC became a popular choice for the design of ADCs because of its capability to scale with technology and its low power. Fig. 2.1(a) and (b) shows the block diagram and working of a 3-bit SAR ADC, respectively. SAR ADC works on the principle of the binary search algorithm. The operation begins with the analog input sampled by the S&H. Consider an input voltage of  $5.5V_{\rm ref}/8$ , where  $V_{\rm ref}$  is the reference voltage of the DAC as shown in Fig. 2.1(a). The 3-bit register initializes the MSB bit to 1 and the remaining bits to 0. The DAC output will correspond to  $V_{\rm ref}/2$ . Since,  $5.5V_{\rm ref}/8$  ( $V_{\rm in}$ ) >  $V_{\rm ref}/2$  then

the comparator output is set to logic 1. Then the next bit (MSB-1) is set to logic 1. The DAC output will correspond to  $(V_{ref}/2 + V_{ref}/4) = 6V_{ref}/8$ . Then,  $6V_{ref}/8$  is compared with  $V_{in}$ . Since,  $V_{in} < 6V_{ref}/8$ , therefore, (MSB-1) bit is set to 0 and then (MSB-2) bit is set to 1. The DAC output will corresponds to  $(V_{ref}/2 + V_{ref}/8) = 5V_{ref}/8$ . Since,  $V_{in} > 5V_{ref}/8$ , therefore, (MSB-2) bit is set to 1. Therefore, the digital word corresponding to the input voltage of  $5.5V_{ref}/8$  is 101.

Figure 2.1 3-bit SAR ADC (a) Block Diagram (b) Working

Figure 2.2 3-bit Vcm-based SAR ADC

With the understanding of the binary search algorithm, the working of Vcm-based differential SAR ADC is explained in Fig. 2.2. Considering the same example as in

Fig.2.1. The  $V_{\rm in}$  is taken as  $5.5V_{\rm ref}/8$ . Let  $V_{\rm ref}$  be 8V, then  $V_{\rm refp}=8V$ ,  $V_{\rm refn}=0V$  and  $V_{\rm cm}=4V$ . Therefore, the  $V_{\rm in}=5.5V$ . The working of the SAR ADC starts when the sampling network samples  $V_{\rm in}$  on the top plate of the capacitors and all the bottom plates of the capacitors are connected to  $V_{\rm cm}$ . Therefore, the charge stored in the capacitor is given by (2.1).

$$Q_{\rm in} = (V_{\rm in} - V_{\rm cm}) 4C_{\rm u} \tag{2.1}$$

Then,  $V_{in}$  is disconnected and the top-plates of the capacitors are kept floating. The charge in the capacitors is given by (2.2).

$$Q_1 = (V_{\rm x} - V_{\rm cm}) 4C_{\rm u} \tag{2.2}$$

By charge conservation rule equation (2.1) and (2.2) are equal.

$$(V_{\rm in} - V_{\rm cm})4C_{\rm u} = (V_{\rm x} - V_{\rm cm})4C_{\rm u}$$

$V_{\rm in} = V_{\rm x} = 5.5V$  (2.3)

Since,  $V_x$  (5.5 V) >  $V_{cm}$  (4V). Therefore, the comparator is set to logic 1 i.e. the MSB bit is 1. Since, comparator is set to logic 1, the  $S_1$  is connected to  $V_{refn}$  (0V) and the remaining switches are still connected to  $V_{cm}$ . Now, the charge in capacitors is given by equation (2.4).

$$Q_2 = (V_x - V_{cm})2C_u + (V_x - V_{refn})2C_u$$

(2.4)

By charge conservation rule, equation (2.2) and (2.4) are equal.

$$(V_{\rm in} - V_{\rm cm})4C_{\rm u} = (V_{\rm x} - V_{\rm cm})2C_{\rm u} + (V_{\rm x} - V_{\rm refn})2C_{\rm u}$$

$$V_{\rm x} = 3.5V \tag{2.5}$$

Since,  $V_x$  (3.5 V) <  $V_{cm}$  (4V). Therefore, the comparator is set to logic 0 i.e. the (MSB-1) bit is 0. Since, comparator is set to logic 0, the  $S_2$  is connected to  $V_{refp}$  (8V) and the  $S_3$  is still connected to  $V_{cm}$ . Now, the charge in capacitors is given by equation (2.6).

$$Q_3 = (V_x - V_{cm})C_u + (V_x - V_{refn})2C_u + (V_x - V_{refp})C_u$$

(2.6)

Again by charge conservation rule, equation (2.4) and (2.6) are equal.

$$(3.5 - V_{\rm cm})2C_{\rm u} + (3.5 - V_{\rm refn})2C_{\rm u} = (V_{\rm x} - V_{\rm cm})C_{\rm u} + (V_{\rm x} - V_{\rm refn})2C_{\rm u} + (V_{\rm x} - V_{\rm refp})C_{\rm u}$$

$$(2.7)$$

$$V_{\rm x} = 4.5V$$

Since,  $V_x$  (4.5 V) >  $V_{cm}$  (4V). Therefore, the comparator is set to logic 1 i.e. the (MSB-2) bit is 1. Therefore, the digital word corresponding to the input voltage of 5.5V is 101.

#### 2.1.2 Pipeline ADC

Pipeline architecture has the advantage of increasing the speed of the ADC. Fig. 2.3(a) illustrates the architecture of a 2-stage pipeline ADC. The sampled voltage is passed to a 3b ADC and then to a 3b DAC. The output of the 3b DAC is subtracted from the sampled voltage. The residue voltage is then amplified and then passed as input to the second stage of the pipeline ADC. Fig. 2.3(b) illustrates an example of the 2-stage pipeline ADC and shows the minimum and maximum input range is 0V and 8V, respectively. Let 6.3V be the sampled voltage by the sample and hold circuit in the first stage. Since each stage consists of 3b. Therefore, the LSB is 1V.

Since, 1 LSB = 1V, therefore, to amplify 1V for an input range of 0-8V for the 2nd stage, the gain of the amplifier must be  $2^3 = 8$ . When 6.3V is the input to the first stage, the digital output of the first stage (D[5:3]) is 110. The residue voltage for the first stage is defined as the difference between the analog input and digital value. The residual voltage attained is 0.3 and is amplified by 8 and becomes the analog input for the second stage of the pipeline ADC. The resultant analog voltage for the second stage is 2.4 V. For an input voltage of 2.4, the digital value corresponds to 010. Hence the digital word corresponding to an input of 6.3 V is 110010.

Figure 2.3 (a) Architecture (b) Example of a 2-stage Pipeline ADC

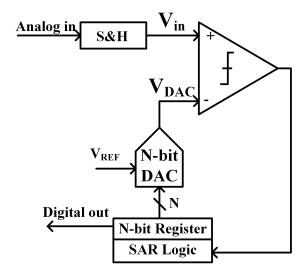

## 2.1.3 SAR-Assisted Pipeline ADC Architecture

Figure 2.4 Block diagram of a Two-stage SAR-Assisted Pipeline ADC

Fig. 2.4 shows the block diagram of a two-stage SAR-assisted pipeline ADC. This architecture combines the advantage of low power from SAR ADC and speed from pipeline ADC.

#### 2.2 Parameters to understand the ADC Performance

## 2.2.1 Terms

• Full-Scale Range (FSR): It is defined as the difference between the positive reference input (V<sub>ref+</sub>) and the negative reference input (V<sub>ref-</sub>). It can also be defined as the difference between the maximum and minimum input voltage applied to the ADC and is expressed as (2.8).

$$FSR = V_{ref+} - V_{ref-} \tag{2.8}$$

- Resolution (N): It is defined as the number of bits an ADC can convert an analog signal.

- Least Significant bit (LSB): It is as the ratio between FSR and  $2^{N}$ , and is expressed as (2.9).

$$LSB = \frac{V_{\text{ref+}} - V_{\text{ref-}}}{2^{N}} \tag{2.9}$$

- Static test: A static test is defined when a slowly varying signal like is ramp signal is applied to the ADC under test. The output results are similar to the results attained when a constant input is given to the ADC under test.

- Dynamic test: Dynamic test is performed to understand the dynamic errors in an ADC. The input given to the ADC is normally a sine waveform.

#### 2.2.2 Dynamic Characteristics

• Signal-to-Noise and Distortion Ratio: Signal-to-Noise and Distortion Ratio (SNDR) is the fundamental frequency signal power level ( $P_s$ ) to the noise plus distortion power level ( $P_{N+D}$ ) ratio and is expressed as (2.10) in terms of dB. SNDR is usually expressed in terms of dB,  $V_{rms}$ , or %.

$$SNDR = 10log \frac{Ps}{P_{N+D}}$$

(2.10)

• Effective Number of Bits: The effective number of bits (ENOB) is the number of bits when both noise and distortion are considered. It is expressed as (2.11).

ENOB =

$$10log \frac{SNDR - 1.76}{6.02}$$

(2.11)

• Total Harmonic Distortion (THD): Total Harmonic Distortion (THD) gives information regarding the total amount of harmonic energy in the FFT plot for a given input frequency, and is expressed as (2.12). The range of the FFT plot is until the Nyquist frequency. It is usually expressed in terms of dB or %.

$$THD = \frac{Summation of harmonic energy}{Fundamental Input Energy}$$

(2.12)

• Signal-to-Noise Ratio (SNR): Signal-to-Noise Ratio (SNR) is defined as the ratio of the fundamental input energy to the noise energy in the spectrum excluding the harmonic energy and the fundamental energy for the given input

signal, and is expressed as (2.13). The spectrum is defined until the Nyquist frequency. In practice, only the first five harmonics are excluded as they are dominant. It is usually expressed in term of dB,  $V_{rms}$ , or %.

$$SNR = \frac{Fundamental Input Energy}{Summation of noise energy}$$

(2.13)

• Spurious Free Dynamic Range (SFDR): It is defined as the ratio of the signal in terms of rms to the rms value of the worst spurious signal in the frequency spectrum. It is usually expressed in dB, and is expressed in dB as (2.14).

$$SFDR = Fundamental\ Input\ Energy - Max(all\ frequency\ except\ fundamental)$$

(2.14)

#### 2.2.3 Static Characteristics

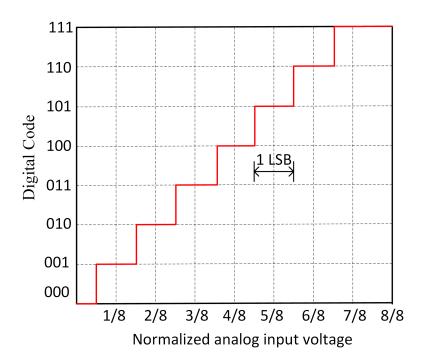

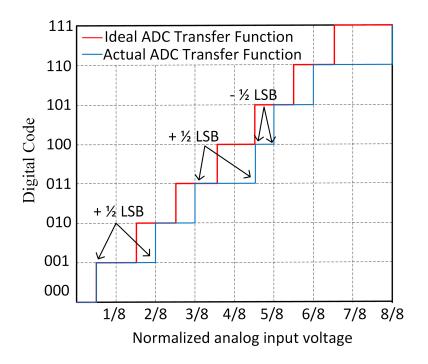

- Ideal Transfer Function: A transfer function is a plot between the normalized analog input voltage with respect to the FSR and the digital code from the ADC. Fig. 2.5 illustrates a  $+\frac{1}{2}$  LSB compensated ideal transfer function of a 3-bit ADC. In this transfer function, the first code (000) is only  $+\frac{1}{2}$  LSB wide and the last code (111) is  $1\frac{1}{2}$  LSB wide. The y-axis represents the digital code, and the x-axis represents the normalized analog input voltage with respect to the FSR.

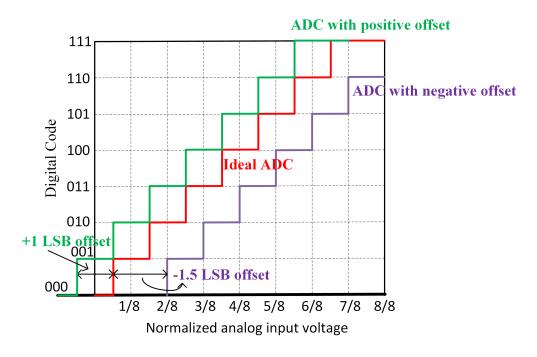

- Offset Error: It is defined as the difference between the ideal offset point (0.5 LSB) and the actual offset point measured in LSB. An offset can be positive or negative. Fig. 2.6 shows the positive and negative offset. The offset voltage is converted to Volts as (2.15).

Offset Voltage (V) = Error in LSB(

$$\frac{\text{Max Input}}{2^{\text{N}}}$$

) (2.15)

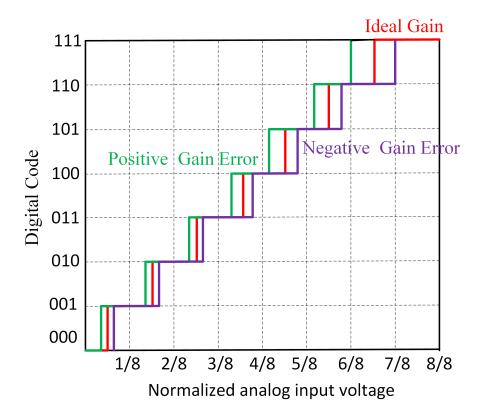

• Gain Error: The gain error is done after the offset error is calibrated. Gain error is defined as the difference between the midpoint of the last step of the ideal transfer function and the actual transfer function. Gain error is calibrated by scaling the output. Fig. 2.7 shows the positive and negative gain error.

Figure 2.5 Compensated Ideal Transfer Function

Figure 2.6 Positive and Negative Offset error

Figure 2.7 Positive and Negative Gain error

• Differential Non-Linearity (DNL): It is defined as the deviation of the actual code width from the ideal code width (1 LSB). Fig. 2.8 represents the DNL error in the ADC. As observed in code 001, the actual code width is  $1\frac{1}{2}$  LSB wide. This is  $+\frac{1}{2}$  LSB greater than the ideal code width (1 LSB).

It can be observed that the lowest code width can be 0, which corresponds to a DNL of -1 LSB and the maximum code width can be greater than 2, which corresponds to a DNL of >+1 LSB. The two mentioned cases correspond to missing codes in an ADC. Hence, for an ideal ADC without any missing digital must have a DNL between -1 LSB and +1 LSB.

• Integral Non-Linearity (INL): INL is the deviation of the actual transfer characteristics from the ideal transfer characteristics. Fig. 2.9 represents the INL error in the ADC. As observed in the 001 code, the deviation of the actual transfer function from ideal transfer function is  $+\frac{1}{2}$  LSB. Moreover, the shape of the INL give an idea of the harmonic present in the ADC. If the shape of the INL is quadratic, it means that even order harmonics are present, and if the shape is cubic, the presents of odd harmonics can be detected. A thumb rule between INL and SFDR is expressed as (2.16).

Figure 2.8 ADC Transfer Function with DNL Error

Figure 2.9 ADC Transfer Function with INL Error

$$SFDR \approx 20log(\frac{2^{B}}{INL})$$

(2.16)

## 2.2.4 Figure-of-merit (FoM)

The figure-of-merit (FoM) is used to assess the power efficiency of the ADC. The two widely used FoMs in literature are Walden FoM and Schreier FoM.

• The Walden FoM ( $FoM_W$ ) is defined as the energy used per conversion step in an ADC and is given by the equation (2.17).

$$FoM_{W} = \frac{P_{ADC}}{2^{ENOB} * f_{s}} \qquad [J/Conversion - steps] \qquad (2.17)$$

where  $P_{\rm ADC}$  is the power consumed by the ADC and  $f_{\rm s}$  is the frequency at which the ADC is sampled.

• The Schreier FoM (FoM<sub>S</sub>) is denoted in terms of decibels and is calculated from SNDR, power consumed by the ADC, and sampling frequency. FoM<sub>S</sub> is expressed as (2.18).

$$FoM_S = SNDR + 10log \frac{f_s/2}{P_{ADC}}$$

(2.18)

#### 3. Proposed Asynchronous SAR logic

Successive Approximation Register (SAR) Analog-to-Digital Converters (ADC) have become a common choice in conjunction with high-speed ADCs because of their lowpower and digital-friendly architecture. However, as the resolution of the SAR ADC increases, the number of conversion cycles increases which reduces the speed of the SAR ADC. Fig. 3.1 shows the block diagram of an N-bit SAR ADC. As shown in Fig. 3.1, a SAR ADC comprises three blocks: the digital-to-analog converter (DAC), the comparator, and the SAR logic. Many architectures have been proposed to solve issues arising from the DAC and the comparator (Chan, Zhu, Sin, Murmann, Seng-Pan & Martins (2017); Roh (2020)), but a few architectures focus on the SAR logic. From articles (Hong, Kim, Kang, Park, Choi, Park & Ryu (2015); Kunnatharayil, Abbasi, Ceylan, Arslan, Zirtiloglu & Gurbuz (2020); Shah & Sahoo (2017)), it can be observed that for technology nodes  $\geq$  65 nm, the SAR logic propagation delay is dominant. However, for technology nodes  $\leq 45$  nm, the SAR logic delay is not dominant. However, while increasing the speed of the SAR logic, simultaneousswitching noise (SSN) increases due to a large number of digital switches switching at the same time.

Figure 3.1 Block diagram of a N-bit SAR ADC

Substrate noise becomes an issue with feature size  $\leq 250$  nm (Wang, Murgai & Roychowdhury (2004)). Substrate noise is generated due to three mechanisms (Briaire & Krisch (2000)): 1) capacitive coupling of the source/drain and the substrate when reversed biased, 2) impact ionization, and 3) noise generated in the ground and power lines mainly due to Ldi/dt arising from the wire bond and package inductance. Among the three mechanisms, the noise generated in the power/ground line is the dominant compared to the impact ionization and the capacitive coupling from the source/drain and substrate (Badaroglu, Wambacq, Van der Plas, Donnay, Gielen & De Man (2006)). Many solutions are proposed to reduce the noise in the power/ground line like improving the packaging techniques that reduce the inductance (Diaz-Olavarrieta (1991)), increasing the number of ground/power pins to reduce the inductance, separating the analog and digital power lines. A better solution would be designing the circuit that reduces the SSN of the digital blocks which thereby reduces the noise in the power/ground line.

This chapter investigates a proposed asynchronous SAR logic with improved speed and better simultaneous-switching noise (SSN) compared to the conventional SAR logic. The proposed asynchronous SAR logic was designed by a former member of the group, and the measurement and analysis is done by the author of the thesis. Initially, Section I introduces the conventional SAR logic and the proposed asynchronous SAR logic based on handshake architecture. This section also compares the speed of the conventional and proposed SAR logic, and shows mathematically that the proposed SAR logic is faster than the conventional. The Section II introduces SSN and compares it with the conventional and proposed SAR logic, and proves mathematically that the proposed SAR logic has lower SSN compared to conventional SAR logic. Finally, Section III shows the measurement results of the 6-bit SAR ADC. This section also shows the simulation results comparing the speed of conventional and proposed SAR logic. Moreover, the SSN is simulated for the conventional, and proposed SAR logic and their performance was compared in terms of ENOB.

### 3.1 SAR Logic Architecture

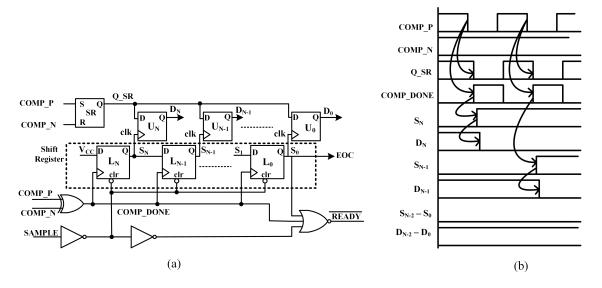

### 3.1.1 Conventional SAR Logic

A conventional SAR logic consists of a serial to parallel shift register ( $L_N$  -  $L_0$ ) which activates the flip-flop from  $U_N$  to  $U_0$ , as shown in Fig. 3.2(a), based on the outputs of the shift register. Fig. 3.2(b) shows the timing diagram of the conventional SAR logic. The SAR logic is activated when one of the outputs of the comparator (COMP\_P or COMP\_N) is activated. For instance, COMP\_P is activated by setting it to '0', as shown in Fig. 3.2(b). This activates Q\_SR and COMP\_DONE signals to '0' and '1', respectively. Hence,  $S_N$  is asserted to '1', and this activates D flip-flop  $U_N$ .

Figure 3.2 (a) Block diagram (Sadollahi et al. (2018)) and (b) Timing diagram of a conventional synchronous SAR Logic

With the knowledge of the working of the conventional synchronous SAR logic, the propagation delay of the SAR logic ( $T_{delay}$ ) can be analyzed when the interconnect delay is ignored.  $T_{prop\_D}$  is defined as the propagation delay from the output of the comparator connected to the SR latch to the input D of the D flip-flops ( $U_N$ - $U_0$ ), and is expressed as in 3.1.  $T_{prop\_clk}$  is the propagation delay from the output of the comparator connected to the XOR gate to the input clk of the D flip-flops ( $U_N$ - $U_0$ ), and is expressed as in 3.2.  $T_{SR}$  defines the propagation delay of the SR latch,  $T_{XOR}$  is the propagation delay of the XOR gate,  $T_{SU,DFF\_L}$  and  $T_{DFF\_L}$  are the setup

time and clk-to-q delay of the D flip-flop  $(L_N)$ , respectively. Based on 3.1 and 3.2, the critical path  $(T_{critical})$  is defined by  $T_{prop\_clk}$ . Hence,  $T_{delay}$  is the sum of the critical time  $(T_{critical})$ , the setup time and the clk-to-q delay of the D flip-flop  $(U_N)$ , and is expressed as in 3.4.

$$T_{\text{prop D}} = T_{\text{SR}}$$

(3.1)

$$T_{\text{prop clk}} = T_{\text{XOR}} + T_{\text{SU,DFF L}} + T_{\text{DFF L}}$$

(3.2)

$$T_{\rm critical} = max(T_{\rm prop\_D}, T_{\rm prop\_clk}) = T_{\rm prop\_clk} \tag{3.3}$$

$$T_{\text{delay}} = T_{\text{critical}} + T_{\text{SU,DFF\_U}} + T_{\text{DFF\_U}} \tag{3.4}$$

However, the interconnect delay also contributes to the propagation delay of the SAR logic. The interconnect delay from the Q\_SR and COMP\_DONE will be dominant compared to the other interconnects because these signals are connected to 'n' D flip-flops, where 'n' is the number of conversions in a SAR ADC. If  $T_{max\_Q\_SR}$  and  $T_{max\_COMP\_DONE}$  are the maximum interconnect delay from signals Q\_SR and COMP\_DONE, respectively, then the maximum propagation of  $T_{prop\_D}$  and  $T_{prop\_clk}$  are expressed as 3.5 and 3.6, respectively.

$$T_{\text{prop D max}} = T_{\text{SR}} + T_{\text{max Q SR}}$$

(3.5)

$$T_{\text{prop\_clk\_max}} = T_{\text{XOR}} + T_{\text{SU,DFF\_L}} + T_{\text{DFF\_L}} + T_{\text{max\_COMP\_DONE}}$$

(3.6)

Hence, the maximum critical delay ( $T_{critical\_max}$ ) is defined by  $T_{prop\_clk\_max}$ , and the maximum propagation delay ( $T_{delay\_max}$ ) is defined as 3.8.

$$T_{\text{critical\_max}} = T_{\text{prop\_clk\_max}}$$

(3.7)

$$T_{\text{delay\_max}} = T_{\text{critical\_max}} + T_{\text{SU,DFF\_U}} + T_{\text{DFF\_U}}$$

(3.8)

# 3.1.2 Proposed Asynchronous SAR Logic

The proposed asynchronous SAR logic (Kunnatharayil et al. (2020)) is designed based on a handshake architecture and implemented in a 6-bit  $V_{cm}$  based SAR

ADC, as shown in Fig. 3.3. The SAR ADC comprises a capacitive digital-to-analog (CDAC) converter, a comparator based on StrongArm latch, and an asynchronous SAR logic.

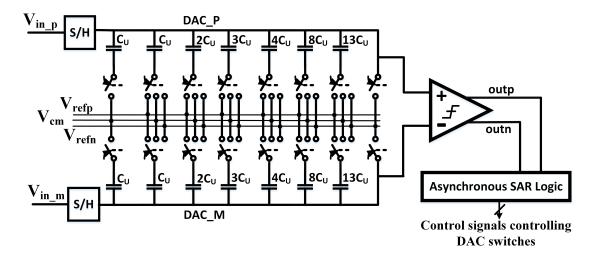

Figure 3.3 Schematic of a 6-bit  $V_{cm}$ -based SAR ADC

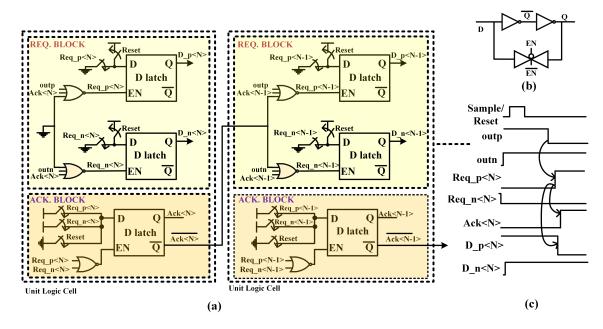

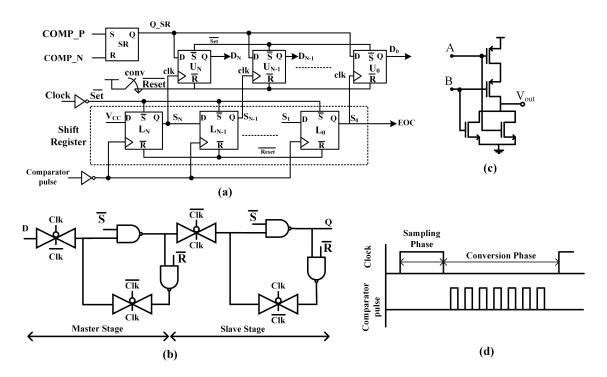

Figure 3.4 (a) Block diagram and (b) Timing diagram of the proposed asynchronous SAR logic (c) Schematic of latch

Fig. 3.4(a) and Fig. 3.4(c) show the block diagram and timing diagram of the proposed asynchronous SAR logic based on handshake protocol, respectively, and Fig. 3.4(b) shows the schematic of the positive level-sensitive D latch. The asynchronous SAR logic based on the handshake protocol comprises two blocks: a Request block and an Acknowledgement block. The Request block sends a Req signal to the Acknowledgement block which respond using an Ack signal. Once, the Ack signal is received, the unit logic cell, which comprises of Request block and Acknowledgement

block, stores the controls for the switches to the differential CDAC and activates the next unit logic cell.

The working of the SAR logic commences with the output of the comparator (outp and outn). Based on the decision of the comparator, one of its outputs will be activated. For instance, outp is activated by asserting to '0' as shown in Fig. 3.4(a) and then, Req\_p<N> is set to '1'. This activates the Ack<N> signal and stores the control signals to the differential CDAC (D\_p<N> and D\_n<N>) in the D latches of the Request block and then, activates the next unit logic cell using  $\overline{Ack} < N >$ .

The propagation delay ( $T_{delay,p}$ ) for the proposed SAR logic architecture is expressed as (3.11) when the interconnect delay is ignored, where  $T_{delay,sw}$  is the propagation delay from the comparator outputs connected to the NOR gates of the Request block to  $D_p < N > / D_n < N >$  (to activate the switches of the CDAC), and  $T_{delay,next \ blocks}$  is the propagation delay from the comparator outputs connected to the NOR gate of the Request block to  $\overline{Ack} < N >$  (activates the next unit logic cell).  $T_{NOR,Req}$  and  $T_{NOR,Ack}$  are the propagation delay from the NOR gate of the Request and Acknowledgment block, respectively.  $T_{D \ latch,Req}$  and  $T_{D \ latch,Ack}$  are the propagation delay of the D latch of the Request and Acknowledgment block, respectively.

$$T_{\text{delay,sw}} = T_{\text{NOR,Req}} + T_{\text{D latch,Req}}$$

(3.9)

$$T_{\text{delay,next blocks}} = T_{\text{NOR,Req}} + T_{\text{NOR,Ack}} + T_{\text{D latch,Ack}}$$

(3.10)

$$T_{\text{delay,p}} = max(T_{\text{delay,sw}}, T_{\text{delay,next blocks}})$$

(3.11)

When the interconnect delay is considered, the interconnect of the output of the comparator will dominate all other interconnects. If the max interconnect delay of the output of the comparator (outp/outn) is  $T_{max\_out}$ , then the maximum propagation delay of the proposed SAR logic is expressed as (3.12).

$$T_{\text{delay,p,max}} = max(T_{\text{delay,sw}}, T_{\text{delay,next blocks}}) + T_{\text{max\_out}}$$

(3.12)

On comparing 3.8 and 3.12, it is evident that the propagation delay for the proposed SAR logic architecture is less compared to the conventional architecture because the critical path of the conventional SAR logic contains two D flip-flops and a logic gate, whereas the proposed SAR logic has a latch and two logic gates in its critical path.

### 3.2 Simultaneous-Switching Noise (SSN)

In high-speed, high-density integrated circuits (ICs) simultaneous-switching noise (SSN) has become of great concern. This is due to the fact that when many output drivers switch at the same time, a large current is drawn from the power supply which creates a power/ground noise called simultaneous-switching noise (SSN). The two noise parameters that define SSN are ground bounce and  $V_{cc}$  bounce. When the ground potential shifts to a non-zero value due to the simultaneous switching, it is called the ground bounce. Similarly, when the supply voltage changes from its reference value, it is called  $V_{cc}$  bounce. A ground bounce occurs when the I/O pins switch from 1 to 0, while  $V_{cc}$  bounce occurs mainly when the I/O pins switch from 0 to 1.

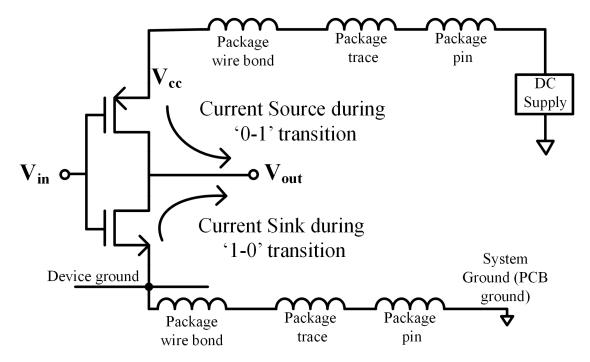

Figure 3.5 An Inverter switching with Parasitic Inductance

Let us consider the circuit in Fig. 3.5, where the inverter undergoes switching. As shown in Fig. 3.5, the device ground is connected to the system ground (PCB ground) through a series of inductance. The inductance arises from the wire bond of the package, the package trace, and then from the package pin. Hence, the effective inductance ( $L_{\rm eff}$ ) is expressed as (3.13).

$$L_{\text{eff}} = L_{\text{wire bond}} + L_{\text{trace}} + L_{\text{pin}} \tag{3.13}$$

where,  $L_{\text{wire bond}}$ ,  $L_{\text{trace}}$ ,  $L_{\text{pin}}$  are the inductance arising from the wire bond of the package, package trace, and package pin, respectively.

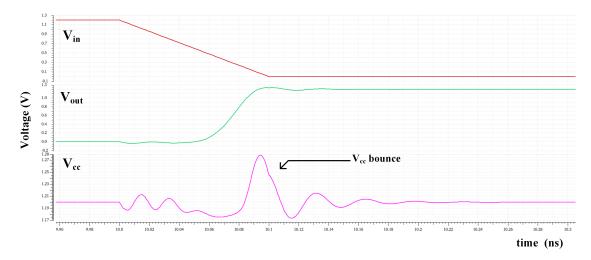

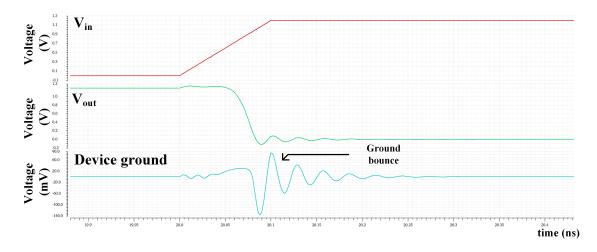

Figure 3.6  $V_{cc}$  bounce plot based on the circuit in Fig. 3.5

Figure 3.7 Ground bounce plot based on the circuit in Fig. 3.5

Suppose the output of the inverter switches from 0-1, a current is sourced from the supply creating a  $V_{cc}$  bounce, as shown in Fig. 3.6, and when the output of the inverter switches from 1-0, a current sink occurs creating a ground bounce, as shown in Fig. 3.7. The amount of current sourced or sunk from the output node depends on 3.14.

$$V = L_{\text{eff}} \frac{di}{dt} \tag{3.14}$$

Based on 3.14, the amplitude of the  $V_{cc}$  bounce and ground bounce is directly proportional to the effective inductance ( $L_{eff}$ ). The problem arises if the ground bounce or  $V_{cc}$  is transferred to the circuits in the design. Suppose the ground bounce is transferred to the circuits in the design and the ground bounce is higher

than  $V_{\rm IL}$  threshold of the input, then the input will be considered as logic "1", and hence, creates a glitch. Similarly, this phenomenon is also applied to  $V_{\rm cc}$  bounce.

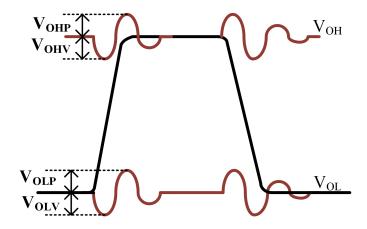

# 3.2.1 Parameters defining Ground bounce and $V_{cc}$ bounce

The parameters that define ground bounce and  $V_{cc}$  bounce are as follows.  $V_{OLP}$  (peak) and  $V_{OLV}$  (valley) define the ground bounce parameters, and  $V_{OHP}$  (peak) and  $V_{OHV}$  (valley) define the  $V_{cc}$  bounce, as shown in Fig. 3.8. Moreover, the width of the pulse is also an important parameter. For instance, if an input buffer has a minimum recognizable pulse width of 5 ns at 1.2 V then any pulse width less than 5 ns will not be detected by the input buffer even if the amplitude is greater than 1.2 V (Microsemi (2008)).

Figure 3.8 Parameters defining Ground bounce and  $V_{cc}$  bounce

## 3.2.2 Factors influencing Ground bounce and $V_{cc}$ bounce

## 3.2.2.1 Effect of Capacitive load

As the capacitive load changes, the amplitude of the  $V_{cc}$  bounce and ground bounce also changes. If the capacitance increases for the same amount of current, the rate of change of voltage across the capacitor will change slowly based on 3.15. Hence, the amplitude of the bounce reduces, however, the pulse width increases.

$$\frac{I}{C} = \frac{dV}{dt} \tag{3.15}$$

## 3.2.2.2 Effect of Output Slew rate

The output slew rate (dV/dt) also affects the ground bounce and  $V_{cc}$  bounce. As the slew rate slows down, the amplitude of the ground bounce and  $V_{cc}$  bounce will be smaller. However, this will affect the performance such as the speed of the circuit.

### 3.2.3 Techniques to overcome SSN

#### i. Package Inductance Reduction

Based on 3.14, the amplitude of the ground bounce and  $V_{cc}$  depends on the effective inductance ( $L_{eff}$ ) arising from the wire bond of the package, the trace of the package, and the pin. If the inductance was reduced then the amplitude of the bounce will also reduce (Swaminathan, Kim, Novak & Libous (2004)). Hence, flip chip becomes an attractive option to reduce the effective inductance ( $L_{eff}$ ).

## ii. Multiple V<sub>cc</sub> pins and GND pins

Another method to reduce the effective inductance (Leff), when the die is wire bonded to the package, is to place multiple GND and  $V_{cc}$  pins. Suppose there were four GND pins and they are wire bonded. The total inductance (L<sub>T</sub>) arising from the wire bond from the GND pin will be the parallel combination of all the inductance arising from the wire bond from all the GND pins, which can be expressed as 3.16.

$$\frac{1}{L_{\rm T}} = \frac{1}{L_1} + \frac{1}{L_2} + \frac{1}{L_3} + \frac{1}{L_4} \tag{3.16}$$

where,  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$  are the inductance arising from the wire bond from first, second, third and fourth GND pins, respectively. If  $L_1 = L_2 = L_3 = L_4 = L$ , then

$$L_{\rm T} = \frac{L}{4} \tag{3.17}$$

Hence, the total inductance arising from the wire bond of the GND pin will be L/4 as expressed in 3.17. Thereby, reducing the effective inductance ( $L_{\rm eff}$ ).

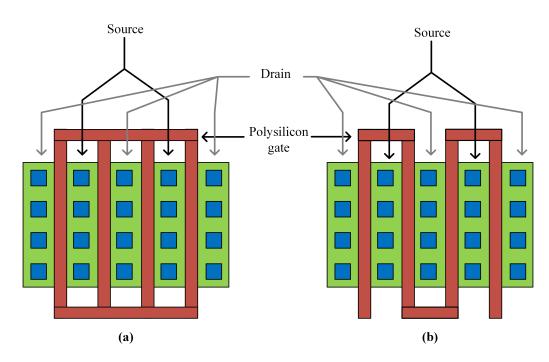

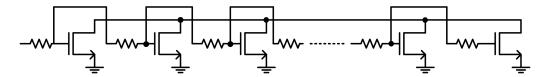

# iii. Output Edge Control ( $OEC^{TM}$ ) Technique

Output Edge Control (OEC<sup>TM</sup>) technique (Instruments (1998); Madani (1996)) is a trademark of Texas Instruments Incorporated. The idea behind OEC<sup>TM</sup> is to slow down the output falling and rising time of the output transistor while maintaining the total propagation delay. In Fig. 3.9(a) shows the typical layout of an NMOS and 3.9(b) shows the serpentine fashion of the polysilicon gate. Based on Fig. 3.9(b), the resistance due to the polysilicon and the capacitance from the gate creates a distributed RC network that slows down the turnon of the next segment, hence, the rise time and fall time are slowed. Fig. 3.10 shows the equivalent circuit of Fig. 3.9(b).

Figure 3.9 (a) Typical NMOS layout (b) Serpentine NMOS layout

Figure 3.10 Distributed transistor

### iv. Separate Analog and Digital GND

A very common technique used is to separate the analog and digital GND so that noisy digital ground does not affect the analog ground.

#### v. Wire bond on to the substrate

Rather than using a chip carrier, the die can be wire bonded on the substrate, thereby reducing the inductance arising from the package frame and pin. Hence, the effective inductance  $(L_{\rm eff})$  is reduced.

### 3.2.4 Comparison of SSN on Conventional and Proposed SAR logic

Figure 3.11 (a) Block diagram of the implemented conventional SAR Logic (b) Schematic of the positive edge triggered D Flip-flop with SET and RESET (c) Schematic of the NAND gate (d) Waveform for clock and comparator pulse

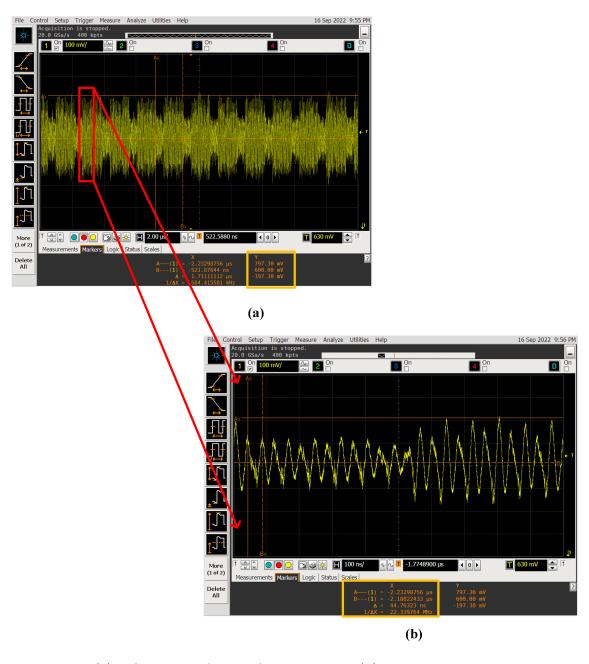

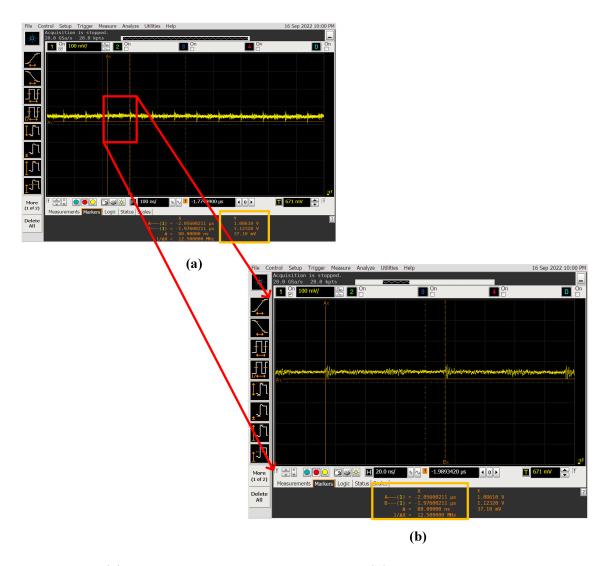

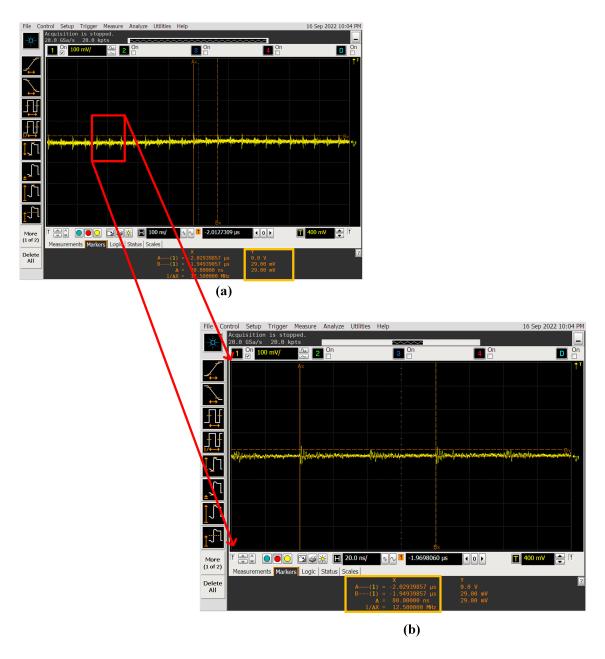

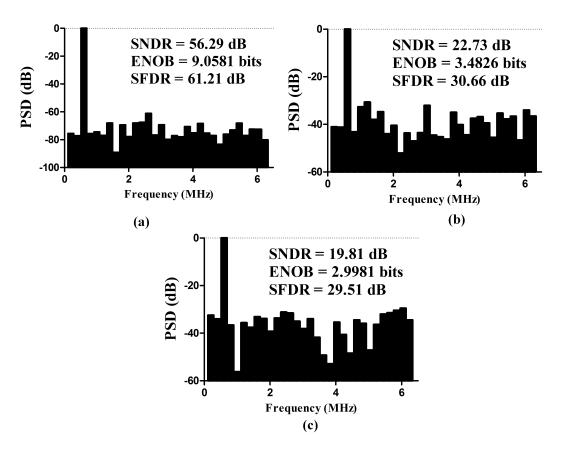

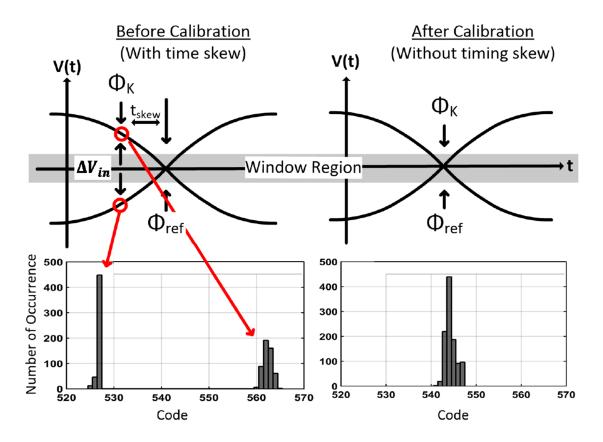

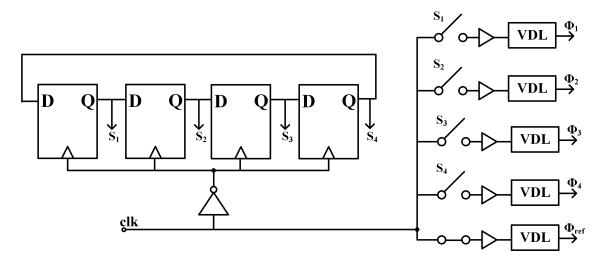

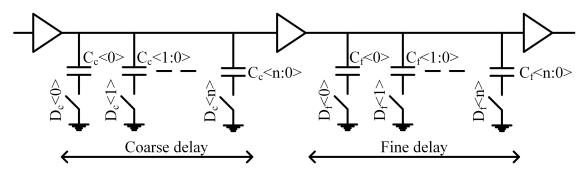

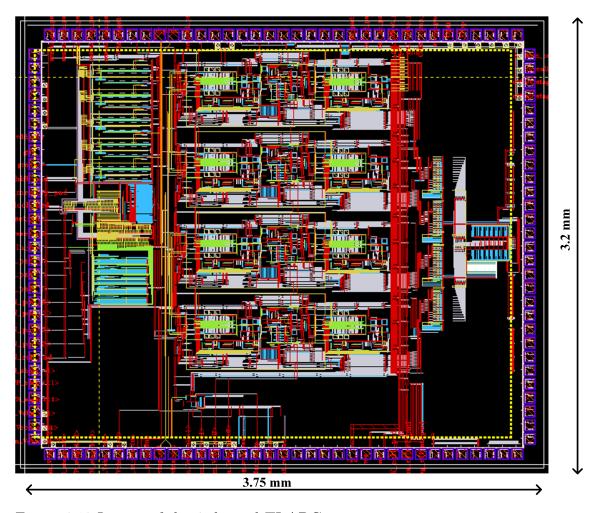

Based on the discussion of the conventional and proposed SAR logic, this section would like to analyze them in terms of  $V_{cc}$  bounce and ground bounce. The schematic of a conventional SAR logic is described in Fig. 3.11(a). A positive edge-triggered D FF with set and reset was used and the schematic is shown in Fig. 3.11(b), and the schematic of the NAND gate is shown in Fig. 3.11(c), and Fig. 3.11(d) shows the waveform for the clock and comparator pulse signal. During the reset phase of the SAR ADC, the reset pin  $(\overline{R})$  of the flip-flop is activated by the  $\overline{Reset}$  signal, and the set pin  $(\overline{S})$  in the flip-flop is activated by the clock signal of the ADC after the reset phase. After the reset phase, the conv signal shown in Fig. 3.11(a) is activated always. During the sampling phase, the set signal  $(\overline{Set})$  is activated to activate only the required switches in the CDAC, and during the conversion