## PROCESS INTEGRATION AND TECHNOLOGY DEVELOPMENT FOR LOW-COST, ACCESSIBLE HIGH DENSITY INTERCONNECT (HDI) PRINTED CIRCUIT BOARDS (PCBs)

|      | by   |      |

|------|------|------|

| EKIN | ASIM | ÖZEK |

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabancı University

December 2021

# PROCESS INTEGRATION AND TECHNOLOGY DEVELOPMENT FOR LOW-COST, ACCESSIBLE HIGH DENSITY INTERCONNECT (HDI) PRINTED CIRCUIT BOARDS (PCBs)

| Approved by:  |                                                      |

|---------------|------------------------------------------------------|

|               | Asst. Prof. Murat Kaya Yapıcı<br>(Thesis Supervisor) |

|               | Prof. Dr. Yasar Gürbüz                               |

|               | Asst. Prof. Dr. Sinan Kazan                          |

| Approval Date | e: December 17, 2021                                 |

Ekin Asım Özek 2021 ©

All Rights Reserved

#### **ABSTRACT**

## PROCESS INTEGRATION AND TECHNOLOGY DEVELOPMENT FOR LOW-COST, ACCESSIBLE HIGH DENSITY INTERCONNECT (HDI) PRINTED CIRCUIT BOARDS (PCBs)

#### EKIN ASIM ÖZEK

Electronics Engineering, M.Sc. Thesis, December 2021

Thesis Advisor: Asst. Prof. Dr. Murat Kaya Yapici

Keywords: high-density interconnect, printed circuit board, HDI-PCB, multilayer, process technology, fabrication

With the growing demand towards 5G and beyond mobile communications, multilayer printed circuit boards utilizing microvias and populated network of electrical wiring to enable highly dense three-dimensional circuit assemblies; otherwise known as high-density interconnect printed circuit boards (HDI-PCB), are becoming a critical enabler for next generation electronic equipment. Although the fundamental difference between HDI-PCBs and traditional PCBs is essentially in the density of electrical interconnects, such difference calls for a paradigm shift in the printed circuit board architecture requiring multilayer stack-up with laser-drilled microvias, buried and blind vias for layer-to-layer electrical interfacing as well as linewidths with resolutions far below typical PCBs.

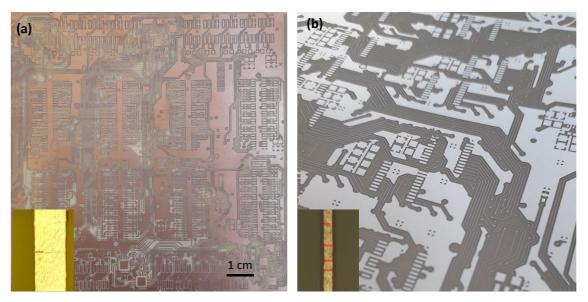

All in all, HDI-PCBs require new fabrication strategies, optimized unit processes (e.g. lithograpy, etching, via drilling and plating) and integration thereof with stringent process control to achieve the specifications set-forth by different HDI-PCB classifications, which understandably comes at a cost and requires special infrastructure. The intention of this thesis is therefore to provide an accessible and low-cost process flow to realize HDI-PCBs by leveraging the capabilities of mechanical drilling to their extent along with basic lab equipment to achieve Type-III-based, 2-N-2 HDI-PCB architecture.

A detailed and optimized fabrication flow is developed in order to establish a reliable and repeatable process flow starting from stacking of the "base" materials (prepreg/core/Cu laminates) up to the final solder mask level. In the developed HDI-PCB process technology, each unit process is experimentally verified and optimized, after which all the unit processes are sequentially performed to achieve an integrated process flow.

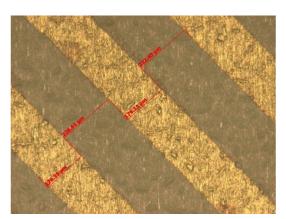

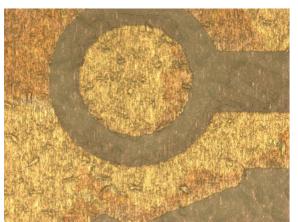

Specifically, the developed and optimized unit processes include: prepreg/copper lamination, mechanical microvia (100  $\mu$ m) drilling, microvia metallization (electroless and electroplating of copper, reverse-etch of overfilled vias), high-density fine line lithography and low-undercut etching.

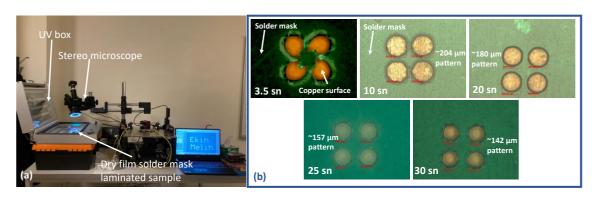

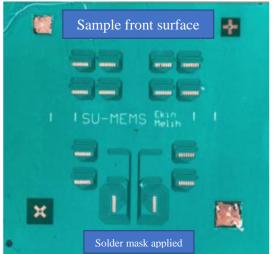

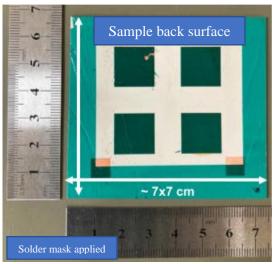

Accordingly, based on the developed process technology, prepreg/Cu lamination was achieved with a 5.93% height difference for sequential build-up architecture. Drilling of 100  $\mu m$  vias in 175  $\mu m$  via pads with center-to-center spacing of 250  $\mu m$  was achieved within a 10% error margin throughout  $10\times10$  cm active HDI board area. Dry and liquid photoresists systems for patterning of copper layers with 50  $\mu m$  line width and 50  $\mu m$  line gap is achieved on 18  $\mu m$  copper foils. Electroless copper plating for the metallization of holes and selective copper electroplating for via filling process flow is developed and realized. Dry film solder mask (75  $\mu m$ ) application was achieved by streo-microscope assisted manual alignment and UV-box flood exposure system, overcoming the limits of typical mask aligner system for thick materials requiring large depth-of-focus microscopes for alignment.

#### ÖZET

### DÜŞÜK MALİYETLİ, ERİŞİLEBİLİR YÜKSEK YOĞUNLUKLU ARA BAĞLANTILI(HDI) BASKI DEVRE KARTLARI (PCB) İÇİN SÜREÇ ENTEGRASYONU VE TEKNOLOJİ GELİŞTİRİLMESİ

#### EKİN ASIM ÖZEK

Elektronik Mühendisliği, Yüksek Lisans Tezi, Aralık 2021

Tez Danışmanı: Dr. Öğr. Üyesi Murat Kaya Yapıcı

Anahtar Kelimeler: yüksek yoğunluklu bağlantı, baskı devre kartı, HDI-PCB, çok katlı, süreç teknolojisi, üretim

5G ve ötesi mobil iletişime yönelik artan taleple birlikte, son derece yüksek yoğunluklu devre yapılarını oluşturmak için mikro vialardan ve yoğun elektrik bağlantılarından yararlanan çok katmanlı devre kartları, yüksek yoğunluklu ara bağlantılı baskı devre kartları (HDI-PCB) olarak bilinen teknoloji, yeni nesil elektronik ekipmanlar için kritik bir etkinleştirici teknoloji haline geliyor. HDI PCB'ler ve geleneksel PCB'ler arasındaki temel fark esasen elektrik ara bağlantılarının yoğunluğunda olmasına rağmen, bu fark devre yığını oluşturmada yaklaşım farklılığı gerektirir. HDI-PCB'lerde lazerle delinmiş mikrovialar, gömülü ve kör vialar ile katmandan katmana elektrik bağlantısı sağlanır ve geleneksel PCB'lere göre oldukça yüksek çözünürlük ile daha dar hat genişlikleri gerekir.

Sonuç olarak, HDI-PCB'ler yeni üretim stratejileri, optimize edilmiş birim süreçleri (ışıklandırma, aşındırma, via delme ve bakır kaplama, vb.) ve bunların farklı HDI-PCB sınıflandırmaları tarafından ortaya konan spesifikasyonları elde etmek için maliyetli ve yüksek süreç kontrolü gerektiren entegrasyonu gerektirir. Bu nedenle, bu tezin amacı, Tip-III tabanlı 2-N-2 HDI-PCB yapısını elde etmek için temel laboratuvar ekipmanı ile birlikte mekanik delme yeteneklerinden yararlanarak HDI-PCB'leri gerçekleştirmek için erişilebilir ve düşük maliyetli bir süreç akışı sağlamaktır.

"Temel" malzemelerin (prepreg/core/Cu laminatlar) istiflenmesinden başlayarak nihai lehim maskesi seviyesine kadar güvenilir ve tekrarlanabilir bir süreç akışı oluşturmak için ayrıntılı ve optimize edilmiş bir üretim akışı geliştirilmiştir. Gelişmiş HDI-PCB süreç teknolojisinde, her birim süreç deneysel olarak doğrulanmış ve optimize edilmiş,

ardından tüm birim süreçlerin entegre edildiği bir süreç akışı elde etmek için sırayla gerçekleştirilmiştir. Spesifik olarak, geliştirilmiş ve optimize edilmiş ünite süreçleri şunları içerir: prepreg/bakır laminasyonu, mekanik mikro via(100 µm) delme, mikro via metalizasyonu (elektrotsuz bakır kaplaması, akımlı bakır kaplaması, aşırı doldurulmuş yolların tersine aşındırılması), yüksek yoğunluklu ince çizgi litografisi ve düşük desen altı aşınmalı bakır aşındırması.

Buna göre, geliştirilen proses teknolojisine dayalı olarak, sıralı yapı mimarisi için %5,93 yükseklik farkı ile prepreg/Cu laminasyonu elde edilmiştir. Merkezden merkeze 250 μm aralıklı 175 μm via pad'leri içinde 100 μm viaların delinmesi, 10×10 cm aktif HDI PCB alanı üzerinde %10'luk bir hata payıyla 18 μm bakır folyolar üzerinde 50 μm çizgi genişliği ve 50 μm çizgi aralığı ile bakır tabakaların şekillendirilmesi kuru ve sıvı fotorezist sistemleri ile sağlandı. Deliklerin metalizasyonu için akımsız bakır kaplama ve doldurma işlemi akışı için seçici akımlı bakır kaplama geliştirildi ve gerçekleştirildi. Kuru film lehim maskesi (75 μm) uygulaması, hizalama için geniş odak derinliği mikroskopları gerektiren kalın malzemeler için tipik maske hizalama sisteminin sınırlarını aşarak, streomikroskop destekli manuel hizalama ve UV-kutu sistemi ile sağlandı.

#### ACKNOWLEDGEMENTS

Without the support and help of many people, this thesis and its underlying contents would not have been possible. First, I would like to thank my advisor, Professor Murat Kaya Yapıcı, for accepting me into his research group, Microelectromechanical Research Group (SUMEMS) at Sabancı University for 2 year and helping me achieve my fabrication goals which are the most part of this thesis. He has been always there when I need help either professionally or personally. Without his presence and patience, I would have never been able to complete this research. I am also grateful to Professor Yaşar Gürbüz for project sponsorship for funding this work and providing feedback. I also would like to thank to technical staff of SUNUM and FENS facilities in Sabancı University, for sharing their knowledge on fabrication that lies at the fabrication parts of this research. I want to thank Professor Yaşar Gürbüz and Professor Sinan Kazan, for participating in my Ms. thesis committe and evaluating my work. Additionally, I would like to thank Ali Kasal for his effort in implementing our discussions on mechanical drilling processes that are conducted at SUMER Lab in Sabancı University. I would like to thank Osman Şahin for his help in SEM experiments. I am deeply thankful to my colleagues at SUMEMS whose help and presence have been one of the most important support of this work during my Ms. studies. I have had the pleasure to share my last 2 years together with them. I thank them all. I would like to thank my colleague, Heba Saleh, for being an amazing teacher introducing me to cleanroom environment when I first arrive at Sabancı University. I would like to thank my colleague, Melih Can Taşdelen, for supporting the experiments and accompanying the studies performed in this thesis study. My special thanks go to Meriç Melike Softa, Özberk Öztürk, Dr. Mustafa Yılmaz, Merve Mil, Farid Sayar Irani, Poyraz Gülebakan, Umurcan Kocaman, Beyza Melis Hazır, Irmak Cemre Kayalan and many more for being there when I needed a friend most.

#### TABLE OF CONTENTS

| 1. | IN   | NTROI  | DUCTION                                                    | 1  |

|----|------|--------|------------------------------------------------------------|----|

|    | 1.1. | Evolu  | ntion of Electronics                                       | 2  |

|    | 1.2. | The T  | Fraditional Multilayer                                     | 3  |

|    | 1.3. | Multi  | layer Problems                                             | 4  |

|    | 1.4. | High-  | Density Interconnect Multilayer Platform                   | 4  |

|    | 1.5. | Basic  | s of High-Density Interconnect Technology                  | 5  |

|    | 1.   | 5.1.   | Interconnect Density                                       | 5  |

|    | 1.   | 5.2.   | High-Density Interconnect Specifications                   | 6  |

|    | 1.   | 5.3.   | Basic High-Density Interconnect Structures                 | 7  |

|    | 1.   | 5.4.   | Seven Most Common High-Density Interconnect Stack-Ups      | 8  |

|    | 1.6. | The I  | Layer Stack-Up Alternatives                                | 11 |

|    | 1.7. | Stack  | ed Vias                                                    | 12 |

| 2. | O    | VERA   | LL PROCESS FLOW AND RELATED FABRICATION PROCESSES          | 13 |

|    | 2.1. | Mate   | rials for High-Density Interconnect                        | 13 |

|    | 2.   | 1.1.   | Dry Photo Film Dielectric                                  | 13 |

|    | 2.   | 1.2.   | Photo Sensitive Liquid Dielectric                          | 14 |

|    | 2.   | 1.3.   | Copper Foil                                                | 14 |

|    |      | 2.1.3. | 1. Electroplated Copper                                    | 14 |

|    |      | 2.1.3. | 2. Electrodeposited Copper                                 | 14 |

|    | 2.   | 1.4.   | Core and Prepreg Materials                                 | 15 |

|    | 2.2. | Com    | mon Fabrication Technologies for High-Density Interconnect | 15 |

|    | 2.   | 2.1.   | Fabrication Processes for High-Density Interconnect        | 15 |

|    | 2.   | 2.2.   | Metallization Processes and Procedures                     | 19 |

|    | 2.   | 2.3.   | Mechanical Drilling Via Technology                         | 19 |

|    | 2    | 2.4    | Desmear and Metallization                                  | 21 |

|    | 2.2.4    | 1. The Alkaline Permanganate Process                                 | 22  |

|----|----------|----------------------------------------------------------------------|-----|

|    | 2.2.4    | 2. Electroless plating                                               | 23  |

|    | 2.2.4    | 3. Metallization with Electroless Copper for Microvias and High Aspe | ect |

|    | Ratio    | Through-Holes                                                        | 24  |

|    | 2.2.5.   | Direct Current Plating Theory                                        | 26  |

| 2  | .3. Fine | Line Imaging and Etching.                                            | 27  |

|    | 2.3.1.   | The Process of Image Transfer                                        | 27  |

|    | 2.3.2.   | The Typical Image Transfer Procedure                                 | 27  |

|    | 2.3.3.   | Fine-line Adhesion Resist                                            | 27  |

|    | 2.3.4.   | Lamination of Dry Film Photoresist                                   | 28  |

|    | 2.3.5.   | Spin Coating of Liquid Photoresist                                   | 28  |

|    | 2.3.6.   | Etching                                                              | 28  |

|    | 2.3.6    | 1. Etch Undercut                                                     | 29  |

| 3. | DEVEL    | LOPMENT AND OPTIMIZATION OF PREPREG COPPER                           |     |

| LA | MINATI   | ON PROCESS                                                           | 30  |

| 4. | DEVEL    | OPMENT AND OPTIMIZATION OF MECHANICAL VIA                            |     |

| FO | RMATIO   | ON PROCESS                                                           | 36  |

| 5. | DEVEL    | LOPMENT AND OPTIMIZATION OF THROUGH HOLE                             |     |

| ME | ETALLIZ  | ATION PROCESS                                                        | 41  |

| 6. | DEVEL    | OPMENT AND OPTIMIZATION OF LITHOGRAPHY AND ETCH                      | ING |

| PR | OCESS (  | ON PREPREG-COPPER LAMINATES                                          | 52  |

| 7. | PROCE    | SS INTEGRATION FOR 2N2                                               | 58  |

#### LIST OF FIGURES

| Figure 1 Most common stack-ups: Sequential buildup (top) and any-layer structure                                       |

|------------------------------------------------------------------------------------------------------------------------|

| (bottom)                                                                                                               |

| <b>Figure 2</b> IPC-2226 six types of HDI structures. 11                                                               |

| $\textbf{Figure 3} \ \textbf{Surface layer alternatives for the most common stack-up architectures.} \ \dots \dots 12$ |

| Figure 4 Stacked microvia configuration: Microvia placed on top of the filled and                                      |

| capped buried via (left), and microvia stacked sequenctially on eachother (right) 12                                   |

| Figure 5 Schematic representation of developed fabrication process for 2-N-2 structre                                  |

| within this thesis                                                                                                     |

| Figure 6 Cross-sectional schematic representation of fabrication process for 2-N-2                                     |

| stack-up within this thesis                                                                                            |

| Figure 7 Four common processes for the metallization of vias                                                           |

| Figure 8 Mechanical drilling of blind vias: (a) controlled depth drilling, and (b)                                     |

| sequential lamination                                                                                                  |

| Figure 9 Schematic representation of electroless plating                                                               |

| Figure 10 Schematic representation of direct current plating setup                                                     |

| Figure 11 Typical multilayer press process setup                                                                       |

| Figure 12 Press profile: Temperature and pressure over time                                                            |

| Figure 13 Preliminary press experiments carried out for bare cores and prepreg                                         |

| interleaved sample                                                                                                     |

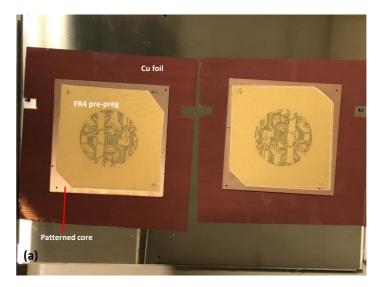

| Figure 14 Lamination setup on press plates for layer 1 and layer n: Cu foul of layer n,                                |

| prepreg, patterened core, prepreg from bottom to top (left) and full stack-up before                                   |

| lamination is shown (right)                                                                                            |

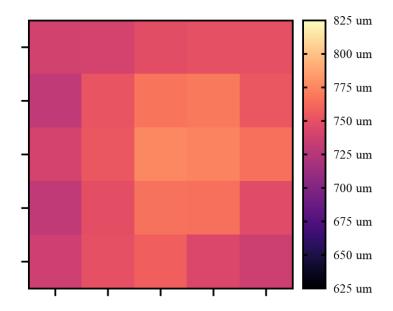

| Figure 15 Stack-up thickness measurements after lamination                                                             |

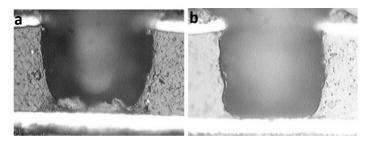

| Figure 16 Scanning electron microscope (SEM) images of two micro vias (a) after                                        |

| drilling and (b) after plasma desmear treatment                                                                        |

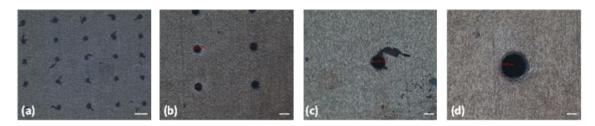

| Figure 17 $$ 100 $\mu m$ via drilling process: (a) Exit surface microscope image for 500 $\mu m$                       |

| thick core samples with $100\ \mu m$ drill bit, (b) Entry surface microscope image for $500$                           |

| $\mu m$ thick core samples with 100 $\mu m$ drill bit, (c) Copper chips left on the exit surface,                      |

| measured via exit side diameter is 113 $\mu$ m, (d) via entry surface, measured diameter of                            |

| entry side is 124 $\mu$ m                                                                                              |

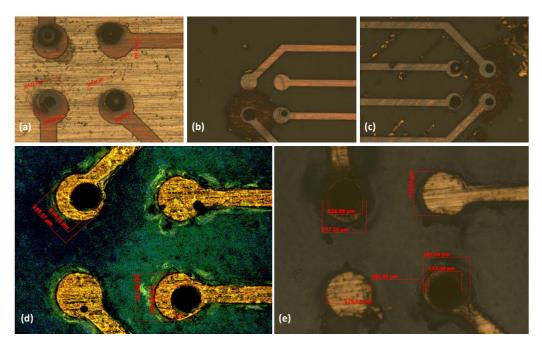

| Figure 18 Mechanical vias opened through via pads: (a) Via drilled on patterned PR on                                  |

| Cu foil, (b,c,d,e) Via drilled on patterened Cu foil                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

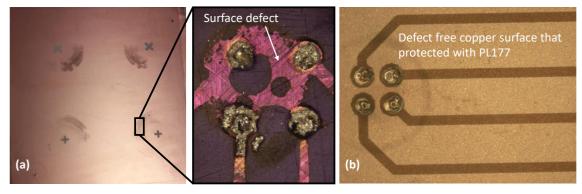

| Figure 19 Surface defects due to mechanical drilling: (a)alignment marks and surface                                                                                                                                                                                                                                                                                                                                                                   |

| defects occurred on Cu foil during alingment marker creation, (b) elimination of surface                                                                                                                                                                                                                                                                                                                                                               |

| defects with protective PR application prior to drilling                                                                                                                                                                                                                                                                                                                                                                                               |

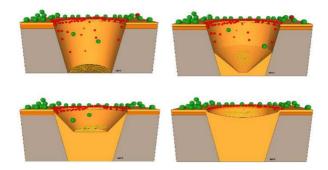

| Figure 20 Functioning mechanism of suppressor, straightener and brightener, green, red                                                                                                                                                                                                                                                                                                                                                                 |

| and yellow, respectively                                                                                                                                                                                                                                                                                                                                                                                                                               |

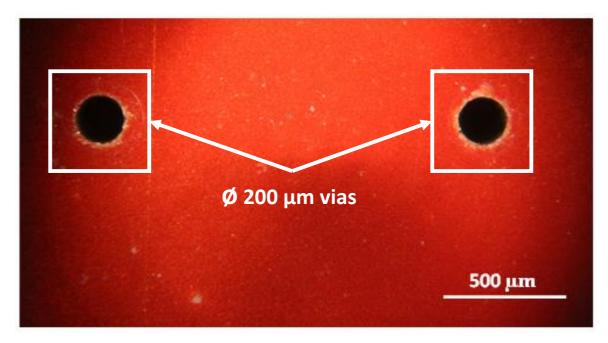

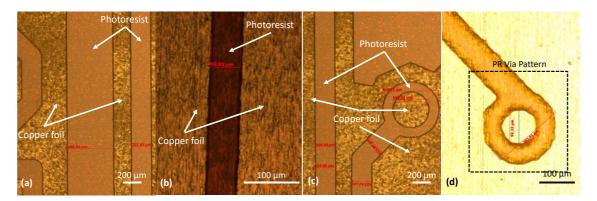

| <b>Figure 21</b> 200 μm throughholes drilled on PR coated prepreg/Cu laminate                                                                                                                                                                                                                                                                                                                                                                          |

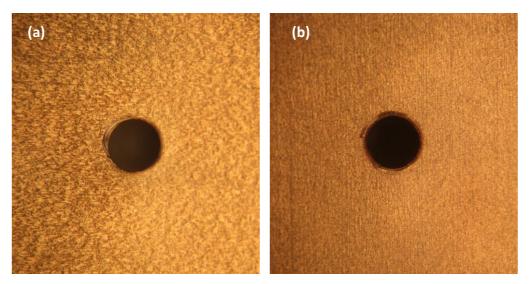

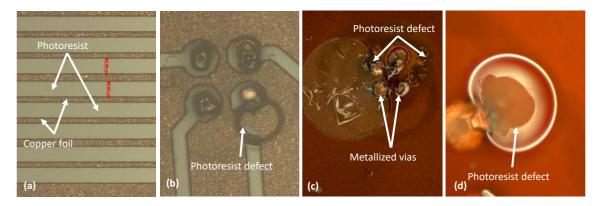

| Figure 22 Cleaning and surface preparation after drilling: (a) before the chemical                                                                                                                                                                                                                                                                                                                                                                     |

| cleaning procedure, (b) after the chemical cleaning procedure described above 46                                                                                                                                                                                                                                                                                                                                                                       |

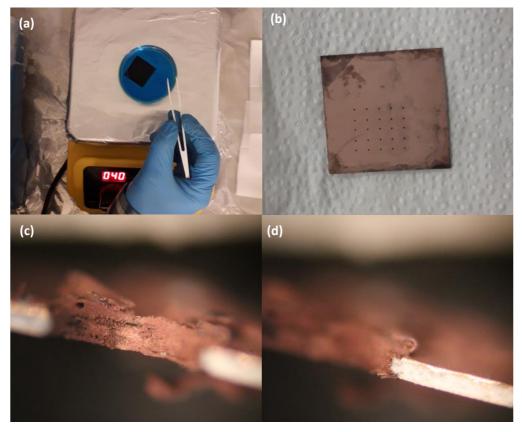

| Figure 23 Electroless Cu plating: (a)lectroless Cu deposition bath, (b) sample after Cu                                                                                                                                                                                                                                                                                                                                                                |

| deposition bath immersion, pink Cu color is achieved, (c, d) Crosssectional microscope                                                                                                                                                                                                                                                                                                                                                                 |

| image of plated vias                                                                                                                                                                                                                                                                                                                                                                                                                                   |

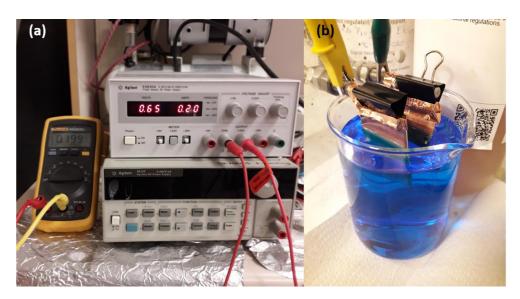

| Figure 24 Electro plating setup: (a) power supply current monitor, (b) electroplating                                                                                                                                                                                                                                                                                                                                                                  |

| bath                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

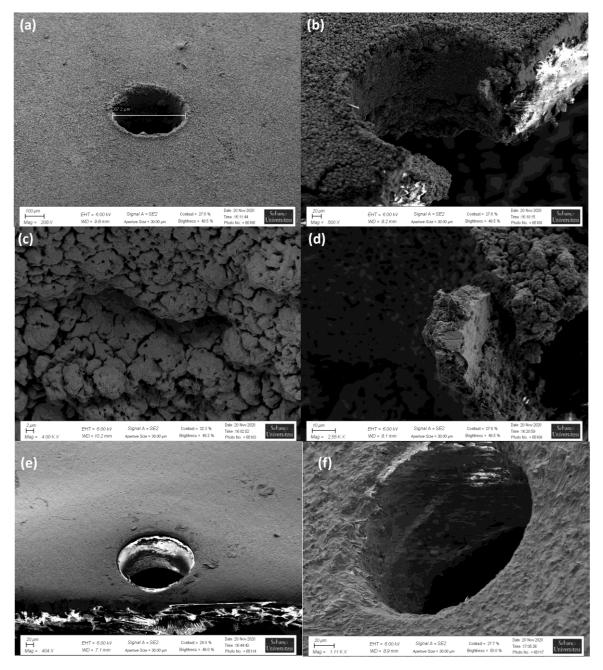

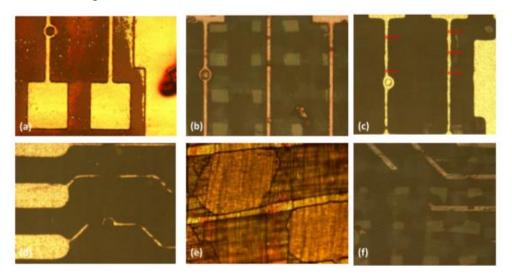

| Figure 25 SEM images of electroplating result; (a) MT77 sample, (b) MT77 wall cross-                                                                                                                                                                                                                                                                                                                                                                   |

| sectional view, (c) MT77 plated in-hole wall surface, (d) MT77 inner-hole wall copper                                                                                                                                                                                                                                                                                                                                                                  |

| thickness (a) unsuccessful electroless plating resulted in unmetallized via well and (f)                                                                                                                                                                                                                                                                                                                                                               |

| thickness, (e) unsuccessful electroless plating resulted in unmetallized via wall and, (f)                                                                                                                                                                                                                                                                                                                                                             |

| partially plated via                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| partially plated via                                                                                                                                                                                                                                                                                                                                                                                                                                   |

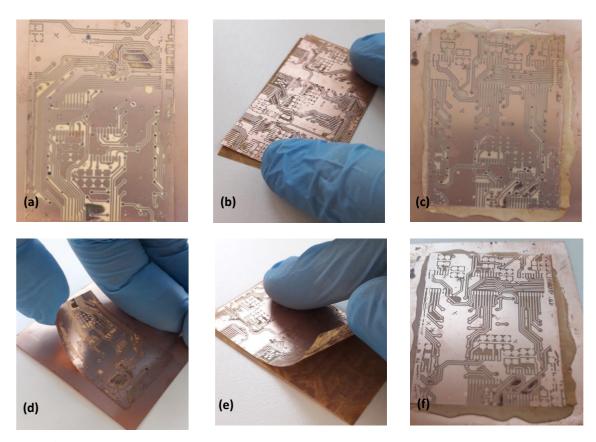

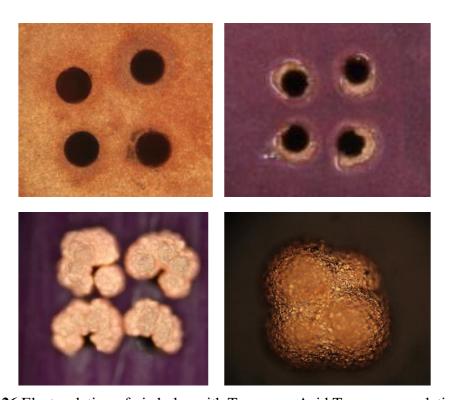

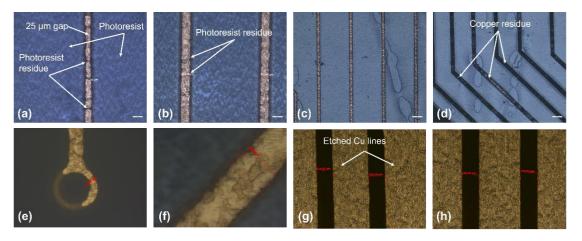

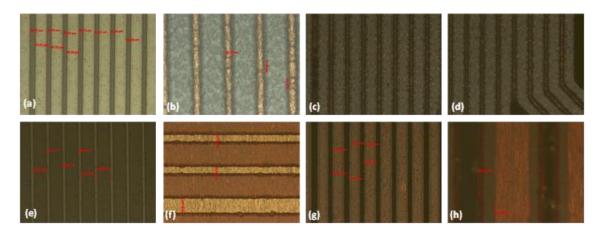

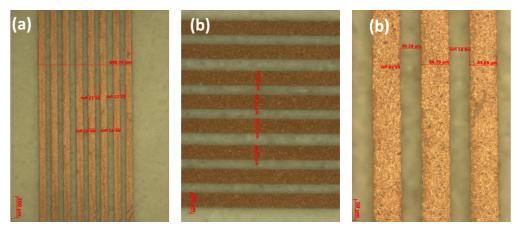

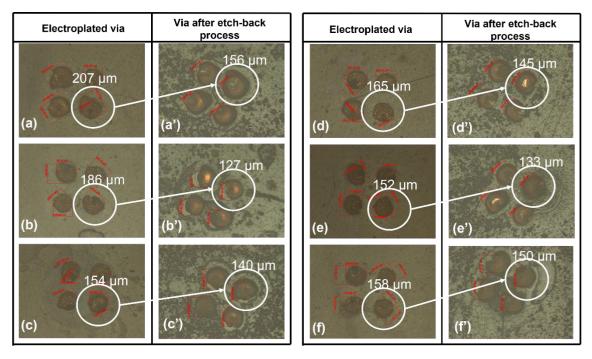

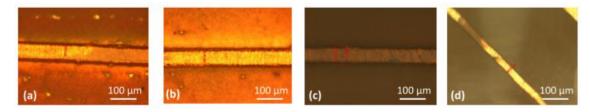

| Figure 26 Electroplating of via holes with Transcene Acid Type copper plating bath. 49 Figure 27 Microvia filling with optimized, additive enhanced plating acid type bath 50 Figure 28 Dry film resist lithography and etching experiments: (a,b,c) 25 μm line opening in dry film photoresist, (d) copper residue after etching,(e,f) dry film residues after development, and (g,h) residue-free etching profile after plasma PR residue ablation   |

| Figure 26 Electroplating of via holes with Transcene Acid Type copper plating bath. 49  Figure 27 Microvia filling with optimized, additive enhanced plating acid type bath 50  Figure 28 Dry film resist lithography and etching experiments: (a,b,c) 25 μm line opening in dry film photoresist, (d) copper residue after etching,(e,f) dry film residues after development, and (g,h) residue-free etching profile after plasma PR residue ablation |

| Figure 26 Electroplating of via holes with Transcene Acid Type copper plating bath. 49  Figure 27 Microvia filling with optimized, additive enhanced plating acid type bath 50  Figure 28 Dry film resist lithography and etching experiments: (a,b,c) 25 μm line opening in dry film photoresist, (d) copper residue after etching,(e,f) dry film residues after development, and (g,h) residue-free etching profile after plasma PR residue ablation |

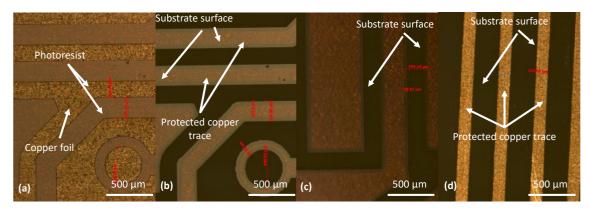

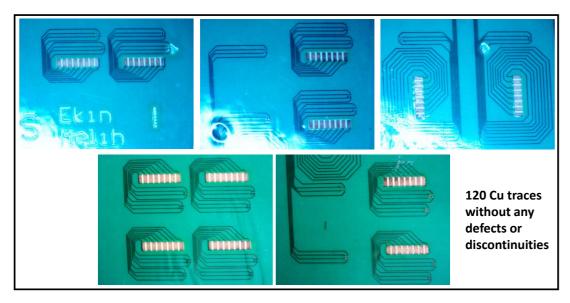

| Figure 34 Etchback process development with AZ4620.                                | . 59 |

|------------------------------------------------------------------------------------|------|

| Figure 35 Etchback process with AZ5214.                                            | . 60 |

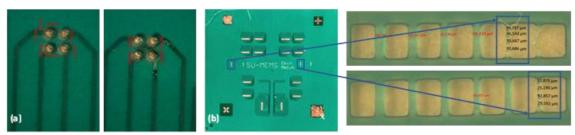

| Figure 36 Realized copper traces with 50 μm line width and 50 μm trace gap under   |      |

| patterened solder mask                                                             | . 60 |

| Figure 37 Solder mask lihography experiments: in-house build solder mask lithogpra | ıhy  |

| setup (a), dose tests for dry film solder mask(b)                                  | . 61 |

| Figure 38 Solder mask lithography: (a) developed solder mask pattern and,          |      |

| (b)developed solder mask bridges.                                                  | . 62 |

#### LIST OF TABLES

| Table 1 Press profile values for each of the five stages of lamination.           | 32    |

|-----------------------------------------------------------------------------------|-------|

| Table 2 Plasma desmear proses parameters for RF power, O2 flow, CF4 flow, dur     | ation |

| and pressure.                                                                     | 38    |

| Table 3 Ideal electroplating bath composition for void-free via filling.          | 42    |

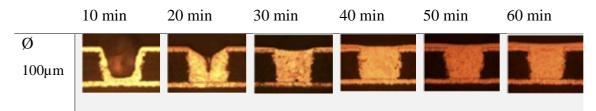

| Table 4 Cross-sectional images of the samples taken from the coating bath at ten- |       |

| minute intervals are given.                                                       | 43    |

| Table 5 Optimized via filling bath composition                                    | 49    |

#### LIST OF ABBREVIATIONS

| IC: Integrated circuit                           |

|--------------------------------------------------|

| BGA: Ball grid array                             |

| HDI: High density interconnect                   |

| PWB: Printed wiring board                        |

| PCB: Printed circuit board                       |

| CTE: Coefficient of thermal expansion            |

| RCF: Resin-coated copper foil                    |

| BUM: Buildup multilayer                          |

| BV: Buried via                                   |

| PS: Power supply                                 |

| OEM: Original equipment manufacturer             |

| MEMS: Microelectromechanical systems             |

| ED: Electrodeposited                             |

| PTV: Plated through via                          |

| AR: Aspect ratio                                 |

| DC: Direct current                               |

| PR: Photoresist                                  |

| CEAC: Curvature enhanced accelerator coverage 43 |

#### 1. INTRODUCTION

Since the dawn of the modern electronic age, printed circuit technology has been the primary enabler for modern electronic devices. It was unavoidable that the unique property of multiple connections at a single solder step, resulting in vast numbers of connections, would become important, and it would continue to be so. Furthermore, printed circuit technology has demonstrated its technological value as it has improved and evolved in response to designers' needs, constraints and advancements in packaging technology, and market demands for smaller, lighter, and less expensive products.

Advances in printed circuit technology have been a series of revolutions that have been required to keep up with the smaller and denser component architecture's massive interconnection needs, resulting in evolutionary eras when new generations of printed circuit technologies are suggested and adapted. Planar non-conductive boards with conductive patterns establishing connections between circular rings around holes that component leads sit through were the first generation of printed circuits. The ability to embed a conductive surface into a hole in a non-conductive material was the next major breakthrough that emphasized the importance of printed circuit technology and laid the foundation for what we see today. The plated through-hole was conceived as a result of this revolution, enabling integrated circuitry on two sides and across multiple layers. We would not have the ubiquitous electronic items that have become essential in our life without the invention of the plated through-hole.

Board technology progressed reliably and slowly as long as the components had leads that penetrated the circuit board. Surface mount technology, on the other hand, ushered in a new era of technological advancement. Surface mount is more environmentally friendly because component leads do not penetrate the substrate board. Component sizes

were no longer limited by the necessity for relatively large through-hole leads, board technology had to adapt to accommodate this change. These next-generation boards have ability to shrink down to the size of a chip. Furthermore, inner layers might be used without leaving any space for holes through the board, resulting in full three-dimensional electrical interconnects. Leads can now escape from any location on the package because they are no longer needed to pass through the package's boundary. To accommodate more board connections, board designers and manufacturers were compelled to invent ways to access these ever-smaller connection points. Instead of using lead connections, this was usually accomplished by penetrating the board with vias whose primary function was circuit continuity rather than lead connection. Board feature dimensions began to shrink from fractions of an inch to thousandths of an inch as a result of the introduction of the Ball Grid Array (BGA), where traditional manufacturing technologies could no longer keep up with this demand.

A new revolution in technology had begun, called the Density Revolution, which is still going on. The term "high-density interconnect" (HDI) has been officially coined. At first glance, HDI appeared to present a challenge in the form of smaller vias due to the near impossibility of mechanical drilling. As a result, HDI immediately raised key challenges in printed circuit technology, including materials, imaging, metallization (including gold plating), testing, assembly, and design (which is particularly important due to the complex geometries involved, but also due to the electrical properties of printed circuit boards). The board has progressed from a simple interface device to an essential component of the overall product design.

#### 1.1. Evolution of Electronics

Electronics is a very new industry, having only been around for almost 60 years. The invention of communications, radar, and ammunition fusion (particularly the radar-altimeter electronic fusion for the first atomic bomb) spurred electronics to become the world's greatest industry, surpassing all others, during World War II. To produce a functional unit, all electronic components must be integrated and assembled. In recent

years, the design and fabrication of these linkages have evolved into a distinct field known as electronic packaging. The printed wire board has been the basic building block of electronic packaging since the 1940s (PWB). To produce the most sophisticated prototypes of these printed wire boards, the high-density interconnect (HDI) printed circuit boards (PCBs), this thesis delves into advanced design principles and fabrication techniques in depth.

The fundamental principles, key benefits, and potential stumbling blocks that must be considered when selecting high-density interconnection methods for electronic systems, as well as the currently available choices, are discussed in this chapter.

#### 1.2. The Traditional Multilayer

The conventional multilayer PWB has been around for more than 50 years. The design guidelines have been evolving with minor differences. In 1968, the ROM for the Hewlett-Packard HP-9100 desktop programmable computer was built from a 16-layer FR-4 multilayer with sheets of PTFE interleaved between the prepreg layers. The 512 64-bit words of the basic operating system were created by etching 1s and 0s onto 0.150 mm traces and gaps, which were subsequently read by high-speed pulses through coupling. The 100-step programmes, as well as the variables, were stored in the ferrite memory. The computer was turned from a million-dollar, air-conditioned office behemoth to a desktop computer for "everyman" thanks to this concept. The ROM PWB was necessary because integrated circuits (ICs) had only 12 gates per chip at the time, which was significantly less than the 32,768 bits (131,072 gates) required for the operating system ROM. Consider how, three years later, in 1971, Hewlett-Packard introduced the HP-35 calculator, which reduced the desktop to the size of a pocket-sized portable calculator. This progress in the device level signaled the start of the modern era of portable electronics.[1]

#### 1.3. Multilayer Problems

Multilayer PWB design flow has not changed in 50 years and still conventional layer structures of signal, power, and ground are present. Copper traces, spaces, and via holes have gotten smaller over the years, but not significantly so that new products from component vendors (particularly IC) rely on HDI. Current and future integrated circuits technologies that show the trend of increasing clock rates and operating frequencies are sensitive to multilayer TH capacitance and inductances. The adoption of HDI in mobile devices has led the high-performance, volume, and cost-sensitive market segments such as automotive, telecom, consumer electronics, to abandon multilayer in favour of HDI-enabled technologies. Classical multilayer PWB offers reduced functionality and design flexibility with greater cost as compared to HDI so that HDI design flow adoption becomes unavoidable for advanced products.

#### 1.4. High-Density Interconnect Multilayer Platform

Fabrication has established itself as the most important link between the base materials and the final value presenting product. In order to produce essentially comparable HDI structures, industry around the world is currently using more than twenty different process flows. Microvia fabrication and small (100 µm) through-holes are straightforward outcomes of advances in lasers, CNC tooling, etching, and processable materials. Alignment, fine-line lithography, metallization, and plating are only a few examples of fundamental problems. This thesis provides a hybrid methodology of alignment and fabrication process flow linking cleanroom processes with industry standards of HDI. On the HDIs, they all have to perform at a very high level. Although this is a time-consuming process to develop and maintain, it is valuable technology to attain and utilize in all printed circuit board manufacturing processes.

#### 1.5. Basics of High-Density Interconnect Technology

#### 1.5.1. Interconnect Density

Three interconnected performance measurements or metrics for the HDI process must be considered when creating an HDI design. Complexity of Assembly measures the difficulty of surface-mounted component assembly. Component Density  $(C_d)$ , which is measured in components per square inch (or per square centimeter), and Assembly Density  $(A_d)$ , which is measured in leads per square inch (or per square centimeter), are two key metrics in electrical design.

$$C_d = {}^p/_a,$$

$$A_d = \frac{1}{a}$$

Component Complexity ( $C_c$ ) is a measure of the degree of sophistication of components, as measured by the average number of leads (I/Os) per part. The component lead pitch is a second metric to consider.

$$C_C = \frac{1}{p}$$

The density (or complexity) of a printed circuit ( $W_d$ ) is determined by the average length of traces on that board per square inch, including all signal layers. Inches per square inch or centimetres per square centimetre are the metric units. A second parameter is the number of traces per linear inch or centimetre. The PWB density was calculated assuming that each net had an average of three electrical nodes and that each component lead was a net node. As a result, an equation [2] is derived that states that the PWB density is equal to  $\beta$  times the square root of the parts per square inch multiplied by the average number of leads per part.  $\beta$  is 2.5 for high analog/discrete, 3.0 for analog/digital, and 3.5 for digital/ASIC:

PWB Density

$$(W_d) = \beta \sqrt{[C_d]}C_c =$$

$$\beta \sqrt{[parts \ per \ sq. \ cm]} (ave. leads \ per \ part)$$

4

Where p denotes the number of components (parts), l denotes the total number of leads on all components, and a denotes the area of the board's top surface (square inches).

#### 1.5.2. High-Density Interconnect Specifications

When it comes to HDI design, the International Product Code Guidelines, Standards, and Specifications can be used as a starting reference point (www.ipc.org). Four of these standards are critical in HDI design [3]:

- IPC-2226, Sectional Design Standard for High-density Interconnect (HDI)

Printed Boards

- IPC/JPCA-2315, Design Guide for High-density Interconnect Structures and Microvias

- IPC/JPCA-4104, Dielectric Materials for High-density Interconnect Structures: Qualification and Performance Specification (HDI)

- IPC-6016, High-density Interconnect (HDI) Structures Qualification and Performance Specification

As a review, these standard-setting documents are briefly discussed in relation to specific HDI design techniques.

IPC-2226 standard covers microvia formation, wiring density selection, design principles selection, interconnecting structures, and material characterisation. Microvia printed circuit boards must meet the specifications outlined in this document.

IPC-4104 standard identifies high-density interconnect structure materials. The slash sheets that define many of the thin materials used for HDI can be found in the IPC-4104 HDI Materials Specifications. In high-performance multilayers, material properties are the most important factor. The selection of materials, which will determine performance and fabrication technology, is still the most important step in HDI design. There are an increasing number of new materials available for HDI design that are not available for conventional multilayers. Dielectric Insulators (*IN*), Conductors (*CD*), and Conductor and Insulators (*CI*) are the three main material types represented in the slash sheets of material

characteristics.

These insulator materials come in four varieties:

- Copper clad resins (RCF, polyimide film, etc)

- Laminates (reinforced epoxy, Cyanate Ester, etc.)

- Liquids (epoxies, photosensitive, BCBs, etc.)

- Films (un-reinforced epoxy, liquid crystal polymers, etc.)

Reinforced and non-reinforced laminates and prepregs are two types of materials that can be classified mechanically. Non-reinforced materials have a lower dielectric constant (Dk), they are thinner than reinforced laminates, and they may be photo-imageable, while reinforced materials have better dimensional stability, a lower coefficient of thermal expansion (CTE), and they are less sensitive to thermal cracking. The most common HDI materials are glass reinforced laminates and resin-coated copper foils (RCF), in this thesis glass reinforced laminates and glass reinforced prepreg-Cu pairs are used in stackup fabrication.

IPC-6016 document contains general specifications for high-density substrates not covered by other IPC documents such as IPC-6011, the generic PWB qualification, and performance specifications.

#### 1.5.3. Basic High-Density Interconnect Structures

A new technology is needed to efficiently fabricate high performance, high frequency interconnect array packages with large number of I/Os. The true usefulness of HDI may be recognised when it comes to extremely small holes known as microvias, despite the recent development of concepts such as sequential multilayer and Buildup Multilayer (BUM). The HDI Design Committee of the IPC defines a microvia as any hole with a diameter of less than 150 um.

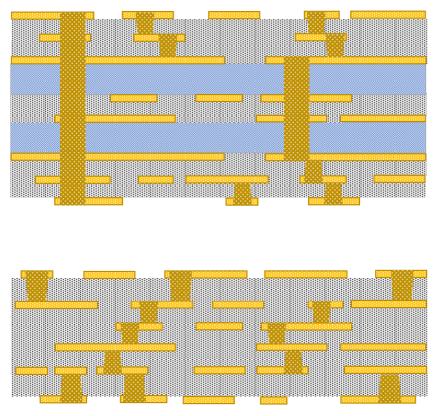

**Figure 1** Most common stack-ups: Sequential buildup (top) and any-layer structure (bottom).

#### 1.5.4. Seven Most Common High-Density Interconnect Stack-Ups

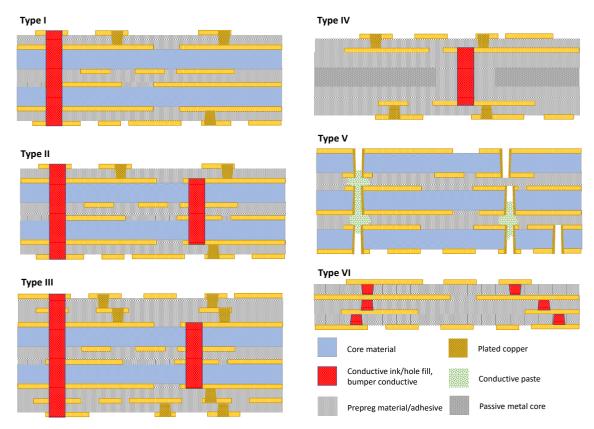

Micron (micrometre) ranges are becoming more relevant in packaging technology as package sizes shrink. The two most fundamental HDI structures that are widely available are "buildup" or "sequence buildup" structures and "any-layer" structures. As shown in Figure 1, these two can bear a striking resemblance to one another. IPC-2226 Design Standard for HDI Printed Boards has a type-based organisational structure. Type I, Type II, Type III, Type IV, Type V, and Type VI are the six distinct types of characteristics. It is important to remember that the extra microvia structure could be present on a different sort of structure rather than as categorized in IPC-2226. Furthermore, this classification is based on microvia appearance, blind vias may exist in all types. As a result, the following definitions apply to all forms of HDI boards:

TYPE I 1 [C] 0 or 1 [C] 1 – with through vias connecting the outer layers. A high-density interconnect substrate with interconnected plated microvias and plated through-holes for

connectivity is specified in this construction. A single microvia layer is fabricated on one or both 1[C]0 or 1[C]1 side of a PWB substrate core in Type 1 topologies. A single microvia layer is fabricated on one or both sides 1[C]0 or 1[C]1 of an underlined PWB substrate core in Type 1 architectures. Conventional PWB building processes are typically used to create the PWB core substrate. This substrate could be either rigid or flexible. The substrate might be as basic as a single circuit layer or as complex as a premade multilayer PWB with buried vias (BV), depending on the purpose. A single layer of dielectric material is then applied to the top of the core substrate to complete the construction. Microvias appear in the dielectric between layers 1 and 2, as well as between layers n and n-1. The structure's layers 1 through n are then connected by through-holes. Depending on the device's intended purpose, the microvias and through-holes are then metallized or filled with conductive material. The fabrication, as well as the circuitry for layers 1 and n, is finished.

TYPE II 1 [C] 0 or 1 [C] 1 – with buried vias in the core and may have through vias connecting the outer layers. Except for Type I, Type II contains all of the HDIs layers present in Type I. The differentiating feature of the distinction is in the core layer [C], where through-via containing core exists in Type II structure. It is feasible to fabricate through-vias in the core before laminating the HDI layers using Type II of the design. The only difference is that the core through-vias are drilled and metallized before the HDI layers are laminated.

Type III  $\geq 2$  [C]  $\geq 0$  — may have buried vias in the core and may have through vias connecting the outer layers. An HDI substrate with interconnected plated microvias and plated through-holes for connectivity is specified in this construction. The development of two microvia layers on either one 2[C]0 or both 2[C]2 sides of an undrilled PWB substrate core is classified as a Type III construction. Conventional PWB building processes are typically used to create the PWB core substrate. This substrate could be either rigid or flexible. The substrate might be as basic as a single circuit layer or as complex as a premade multilayer PWB with buried vias, depending on the purpose. A layer of dielectric material is then applied to the top of the core substrate to complete the construction. Microvias connect layers 2 and 3, and layers n-1 and n-2 of the dielectric. It's critical to metallize or fill the initial microvia layer with a conductive material before circuitizing the device. After that, the second layer of dielectric material is applied to the

circuitized layer, and microvias are fabricated for layers 1 and 2, as well as layers n and n-1, as shown in Figure 2. Then, to connect layers 1 and n, through-holes are drilled. The microvias and through-holes are metallized or filled with a conductive substance to complete the design. The fabrication, as well as the circuitry for layers 1 and n, is completed.

TYPE IV  $\geq 1$  [P]  $\geq 0$  – where P is a passive substrate with no electrical connection. This concept proposes a high-density interconnect substrate in which microvia layers serve as redistribution layers on top of an existing drilled and metallized passive substrate. Typically, the PWB or metal core substrate is created using standard PWB processes. This substrate might be rigid or flexible.

TYPE V – Coreless constructions using layer pairs. This construction depicts a high-density interconnect substrate in which the microvias may appear in any layer. Cores are drilled, metallized, and pattered before lamination in this architecture. Pre-patterned cores are then laminated and vias are filled with conductive material to complete the design. A rigid or flexible substrate may be used for this purpose.

TYPE VI - Alternate constructions. This construction proposes a high-density interconnect substrate in which core structure does not appear. Prepreg/Cu layers are laminated, patterned, and metallized sequentially to achieve any-layer structure.

Figure 2 IPC-2226 six types of HDI structures.

#### 1.6. The Layer Stack-Up Alternatives

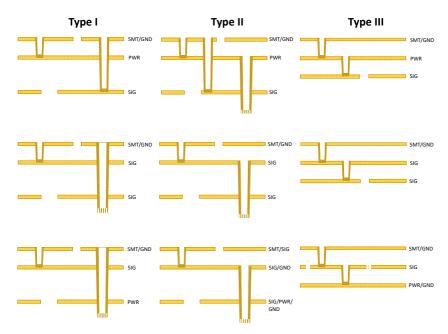

Many of the more typical HDI stack-ups used to reduce the number of through-hole vias in a design are shown in Figure 3. The three most popular HDI stack-ups are shown with the IPC-Type structures (I, II & III). Dielectric materials such as standard prepregs, laser-drillable prepregs, RCCs, reinforced RCCs, and BC cores are all viable between Layers-1 and Layer-2. It is feasible to employ a "skip-via" from Layer-1 to Layer-3, as shown in Figure 3, if the dielectric is thin enough, eliminating the cost of an IPC-Type III structure and therefore saving money. Any dielectric thickness less than 0.005 inches (0.125 mm) connects GND and PWR, resulting in lower power supply (PS) impedance and lower PS resonances and noise.

**Figure 3** Surface layer alternatives for the most common stack-up architectures.

#### 1.7. Stacked Vias

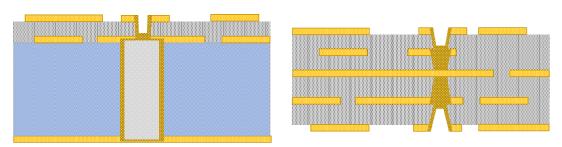

HDI is compounded further when fine-pitch ball-grid-arrays (BGAs) are used and the design parameters do not provide for clearance for staggered blind vias. This is an unavoidable problem when working with HDI. When this problem occurs, it is important to stack microvias one on top of the other or a microvia on top of the buried via. These two scenarios are depicted in Figure 4: On the left, a microvia is layered on top of a filled and remetallized buried via; on the right, a microvia is placed on top of a filled and remetallized buried via. The right figure comprises two laser-drilled microvias. The microvia in the bottom layer (Layer 2/3) has been entirely plated.

**Figure 4** Stacked microvia configuration: Microvia placed on top of the filled and capped buried via (left), and microvia stacked sequenctially on eachother (right).

### 2. OVERALL PROCESS FLOW AND RELATED FABRICATION PROCESSES

#### 2.1. Materials for High-Density Interconnect

The materials utilized to fabricate HDI circuits are discussed in this chapter. There are several excellent guidelines on printed circuit board materials (for example, Coombs' Printed Circuits Handbook), but specific focus on those materials that are unique to HDI's manufacturing process are investigated. Given that nearly all HDI boards have layers that are identical to those on traditional printed circuit boards, a thorough examination is beneficial.

Based on BPA Consulting Ltd. statistics, the global HDI materials market was 51 million square metres in 2006, and 83 million square meters in 2020 with majority of the utilized materials being laser-drillable prepregs, resin coated copper, and conventional prepregs.

#### 2.1.1. Dry Photo Film Dielectric

Photosensitive dry film dielectrics were originally considered to be the ultimate high-density interconnect (HDI) dielectric due to the fact that no additional equipment was required to create the vias. This was not the case, as these were negative acting photosystems. It was necessary to use ultraviolet energy to cure the dielectric permanently, as a result of negative action. It would be beneficial for cleanroom users to utilize dry photofilm dielectrics since this material is already suitable for Class-100 environment, however, over the years, because of the fact that expensive cleanroom infrastructure requirement, this dielectric is limited to original equipment manufacturers (OEMs) in Japan, who have their own manufacturing facilities.

#### 2.1.2. Photo Sensitive Liquid Dielectric

Liquid photosensitive dielectrics degrade similarly to dry film. They have the advantage of producing less waste and allowing for finer coating thickness control. The significant demand for crucial coating equipment and clean-room space is their main disadvantage for industry players. Yet for the research and prototyping purposes, after MEMS chips or ICs are fabricated, dependence for PWBs for testing and measurement to outer suppliers are not ideal. For emerging high frequency applications such as beam forming systems, unconventional buildups are necessary, however, photosensitive liquid photo dielectric is not a common material utilized.

#### 2.1.3. Copper Foil

The sole conductor of electrical currents available to designer is copper metal on printed wiring boards (PWBs). Copper foils come in three different types that are commonly utilised in the fabrication of printed wire boards.

- Electroplated

- Electrodeposited

- Wrought (rolled annealed)

#### 2.1.3.1. Electroplated Copper

The fundamental function of electroplated copper is to deposit copper in through holes. As a result, the HDI fabrication process flows at least includes a step that electroplates via holes. The number of electroplating steps is determined according to type selection, intended application, and metallization scheme (additive, semi-additive, subtractive).

#### 2.1.3.2. Electrodeposited Copper

Electrodeposited (ED) copper foil is the most often used foil in the fabrication of printed circuit boards. Copper is electroplated onto a cylindrical drum, commonly made of

titanium, using a pure copper sulfate/sulfuric acid solution in an electrochemical process. ED foil is used in the production of electronic devices. The thickness of the generated foil is determined by the rotation speed.

#### 2.1.4. Core and Prepreg Materials

The fundamental material components of printed circuit boards are polymer resin (dielectric), which may or may not contain fillers, reinforcement, and metal foil. The layers of dielectric material, either with or without reinforcement, are placed between the layers of metal foil to form a printed circuit board.

The majority of the dielectric materials used in the fabrication of printed circuit boards are reinforced in the resin system as part of the overall design. It is the most frequent type of reinforcement to have fibreglass woven into the structure. Fabric made of woven fibreglass is comparable to any other sort of cloth in that it is composed of separate filaments that are woven together to make one continuous piece of material on a weaving loom. The use of various diameter filaments and weaving patterns can result in a plethora of different types of glass fabric.

#### 2.2. Common Fabrication Technologies for High-Density Interconnect

#### 2.2.1. Fabrication Processes for High-Density Interconnect

In 1980s, researchers aimed to reduce the size of vias in printed circuits, which led to the development of High-Density Interconnect printed circuits. Although the innovator's identity is unknown, early pioneers include Larry Burgess (creator of the LaserVia), Dr. Charles Bauer (inventor of photodielectric vias) [4], and Dr. Walter Schmidt [5] (development of plasma-etched vias). In the late 1970s, laser drilled vias were initially employed in multilayer mainframe computer systems. These vias were not as small as today's laser-drilled vias, and they were only available in FR-4, a difficult-to-manufacture material. The first production build-up or sequentially printed boards were released in 1984 with Hewlett-laser-drilled Packard's FINSTRATE computer boards, IBM-SLC

#### YASU's [2], and Dyconex's DYCOstrate.

Laser drilled microvias were never planned for Finstrate board bt HP. They were developed by reverse engineering their 32-bit microcomputer CPU. High yield and lower cost attracted great attention towards laser processing of microvias and laser via technology is adopted in the industry, yet for prototyping purposes, mechanical vias are still viable down to 100 um in diameter.

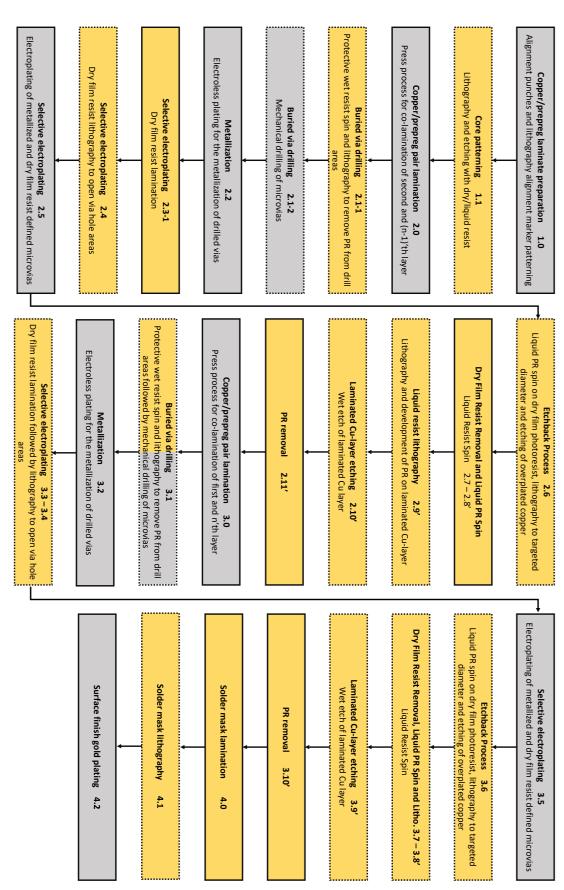

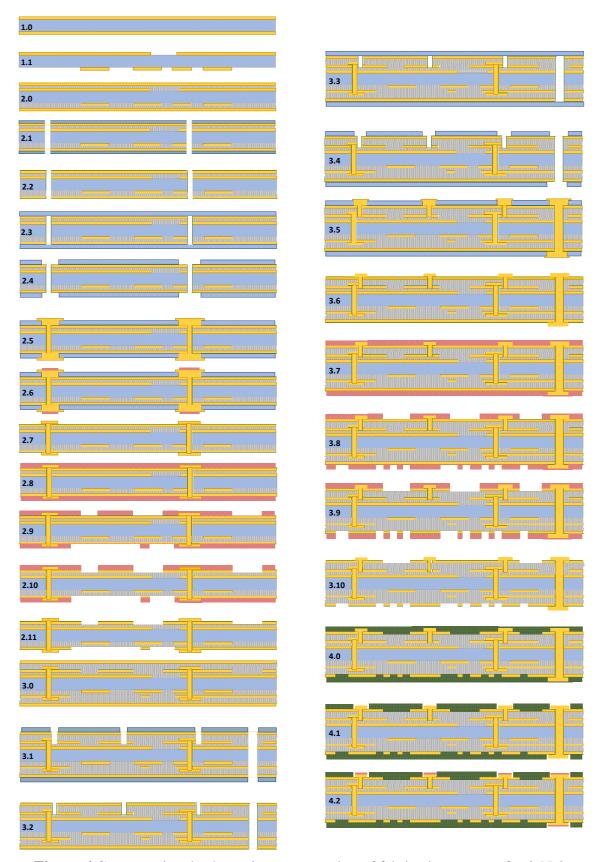

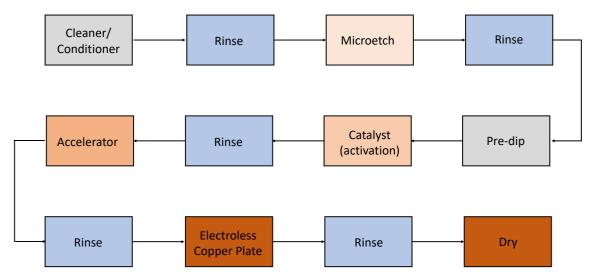

Fabrication process developed within this thesis is given schematically in Figure 5. Yellow boxes refer to a process that requires cleanroom conditions, dashed outline refers to shaping and forming processes having HDI sized (features smaller than 150 µm) features, and grey boxes are performed at regular laboratory conditions. Process flow starts with the preparation of the core layer coded as 1.0, followed by patterning of the active core coded as 1.1. Prepreg-Cu layer pairs are laminated to both sides of the core structure at each lamination step and each new layer increments the first digit by one. Each step explained in the schematic fabrication process flow described in Figure 5 has a corresponding cross-sectional representation with step-specific modification plotted in Figure 6.

**Figure 5** Schematic representation of developed fabrication process for 2-N-2 structre within this thesis.

**Figure 6** Cross-sectional schematic representation of fabrication process for 2-N-2 stack-up within this thesis.

#### 2.2.2. Metallization Processes and Procedures

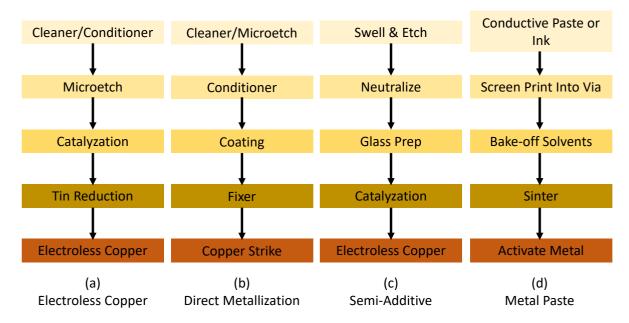

Vertical electrical interconnects are ubiquitous in HDI structures and may be the most important element of the functional stackup. The vertical interconnect elements used in HDI processes can be metallized in one of five different ways are given below. The following procedures apply:

- 1. Electroless and electroplating copper in the conventional sense (Figure 7.a)

- 2. Conventional conductive graphite or other polymers, as opposed to graphite oxide (Figure 7.b)

- 3. Electroless Copper, both fully additive and semi-additive scheme (Figure 7.c)

- 4. Conductive Pastes or Inks (Figure 7.d)

- 5. Fabrication of Solid Metal Vias

**Figure 7** Four common processes for the metallization of vias.

#### 2.2.3. Mechanical Drilling Via Technology

Mechanical drilling was previously the most often employed method of via production on a global scale. However, as a growing number of designs require microvias with a diameter of less than 0.20 mm, novel solutions have evolved. This trend has been accelerated by the growing popularity and use of blind and buried vias. When using a

mechanical drill, the vertical walls are parallel to one another, which is referred to as anisotropic drilling. There are numerous non-mechanical drilling processes that are isotropic, meaning their walls recede laterally in lockstep with their depth, or have sloping walls, meaning the entry opening is larger than the exit opening. While a larger entry opening facilitates less troublesome metallization, the isotropic retreating wall can complicate metallization and plate-up.

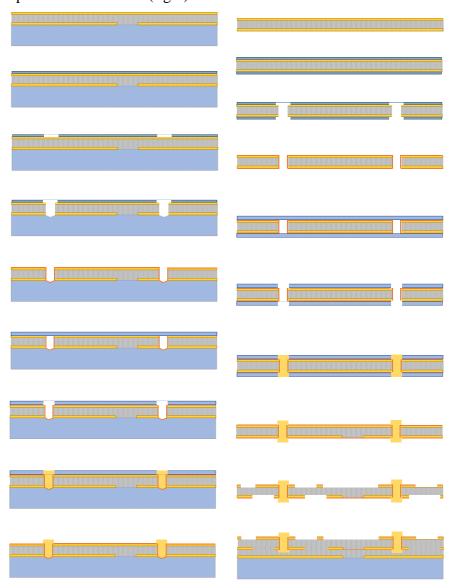

Mechanical vias can either be opened with depth control or directly, which would require different fabrication routes in terms of metallization and lamination. In Figure 8, depth-controlled drilling of blind vias (left) and sequential lamination-based blind via fabrication process is described (right).

**Figure 8** Mechanical drilling of blind vias: (a) controlled depth drilling, and (b) sequential lamination.

#### 2.2.4. Desmear and Metallization

To ensure the reliability of plated through-holes and blind vias, detailed hole preconditioning and metallization are required. The desmear process is used to clean interconnects and via pads of residual via formation residues to prove a tightly adherent contact between the succeeding metallized coating and the interconnects and via pads. Residues are produced by the heat generated during drilling and by items left on the via pads following mechanical drilling. Additionally, it is meant to create topographical modification or micro-roughening in the resin by the desmear process, which can be performed using alkaline permanganate, plasma, or a combination of the two.

Numerous investigations undertaken by experts in the field of PTV/BV dependability have established that long-term reliability is strongly influenced by the quality and consistency of the copper deposit contained within the through-hole and blind vias. Most of the consumers and PCB designers are unaware that the metallization process performed prior to copper electrodeposition application is critical for establishing a homogeneous copper layer in blind vias and through-holes. The methods utilised to establish conduction through these vertical interconnect elements determine whether or not the electroplated copper is continuous and adheres to the resin and any supporting structures, such as glass or other fibre material. There are multiple methods available for making vias conductive, including the following:

- 1. Electroless Copper

- 2. Palladium-based Direct Metallization

- 3. Graphite

- 4. Carbon Black

- 5. Conductive Polymer

These metallization techniques have been extensively explored in recent years for both plated through-hole and blind via metallization applications. Electroless copper specifics and procedure will be discussed in greater detail later in this chapter since the utilized metallization process is electroless copper plating in this thesis work. It is vital to begin with the desmear procedure, as it is critical to the metallization process' overall performance and must be done first.

#### 2.2.4.1. The Alkaline Permanganate Process

In comparison to the dry plasma method, the alkaline permanganate method is a multistep procedure that is meant to remove smear and microroughen the resin. Desmearing the inner layer enables the electroless copper and acid copper to adhere well to it, as the smear is removed during the process. Additionally, this method is used to ensure that the resin surface is sufficiently prepared for the catalyst and electroless copper to adhere to the resin. Four stages comprise the desmear procedure:

- 1. Sweller

- 2. Permanganate

- 3. Neutralizer

- 4. Etch on glass (Optional)

#### Solvent/Sweller/Hole Cleaner

The solvent's function is to expand the resin, making it more susceptible to attack by the permanganate solution that follows. The dwell time, concentration, and temperature are all critical aspects. If the dwell time in the solvent is short, the permanganate will remove just a small amount. When the dwell period in the solvent is prolonged, the solvent may penetrate further than necessary and persist in the resin during permanganate processing.

#### **Permanganate**

By oxidising the resin bonds, permanganate is utilised to remove resin from the body. It is made of permanganate and hydroxide components. The duration of the permanganate and hydroxide solutions, their concentrations, the temperature, and the amount of residue remaining in the solution are all critical factors to consider. Resin may not be completely removed if the dwell time in the permanganate is too short. If the stay time in the permanganate solution is extended, a significant amount of resin is lost, resulting in an uneven profile on the hole wall. Additionally, an excessive dwell time may result in reduced topography along the hole wall, as a result of resin being removed beyond that swollen by the solvent stage.

#### Neutralizer

The neutralizer's purpose is to remove any permanganate residue that may have remained on the panel following cleaning. The duration of the dwell, the sulfuric acid concentration, and temperature of the neutralizer are all critical factors to consider. Allowing permanganate to remain on the panel will obstruct proper catalyst adsorption, resulting in electroless copper gaps in the resin, hole wall pullaway, and general contamination of the via pads and interconnects, among other issues. Separation of plating is more possible if permanganate is left on the copper inner-layer or via pad following plating.

#### 2.2.4.2. Electroless plating

To deposit copper coating on the board surface and along the via wall, an electroless copper plating process is utilized. Its purpose is to carry electricity through the hole, allowing for more copper accumulation in acid copper plating to occur. A total of four key pretreatment processes are required before the electrolytic copper process can begin:

#### 1. Cleaning and Conditioning

The cleaner/conditioner is designed to remove debris from both the surface and from crevices in the via hole surface. Additionally, it conditions the glass and resin to ensure that the catalyst adheres effectively to their surfaces. The duration of time spent in a solution, its concentration, and temperature are all significant factors to consider.

#### 2. Microetching

The microetch process micro-roughens the copper surface to improve the bonding between the electroless and laminate copper layers. Consideration factors are the copper content, sulfuric acid concentration, oxidizer concentration, dwell period, and temperature for microetching. A shallow etching depth can result in poor electroless adhesion. A high etch rate might result in a reduction in copper thickness and a negative etchback.

#### 3. Catalization

The catalyst is designed to deposit palladium on the surface of the via hole. Following that, the palladium will operate as an activation point for the electroless copper deposition process. This is preceded by a pre-dip that acts as a sacrificial bath prior to the addition of the catalyst. The pre-dip process removes oxides from the catalyst, hence reducing copper contamination. Additionally, it aids in the adsorption of common ions into the catalyst. Acid normality, chloride normality, stannous chloride concentration, catalyst concentration, dwell duration, and temperature all play a role in the performance of the catalyst. Void development, insufficient adhesion, and hole wall pullaway are all possible outcomes of insufficient catalysis.

#### 4. Electroless Copper Bath

The basic formulation of electroless copper baths is composed of five major components:

- The presence of copper ions, usually in the form of copper sulphate or copper chloride.

- A reducing agent, usually formaldehyde.

- pH adjusters (commonly sodium hydroxide) used to maintain a pH between 11 and 13.

- Chelating agents, which are substances that help to keep the copper ion in solution.

- Chemicals that are proprietary to the manufacturer, such as stabilisers, wetting agents, ductility enhancers, and grain refiners.

Using the electroless copper bath, copper coating is applied to the board surface as well as along the via wall. It conducts electricity through the via holes, allowing for increased accumulation of electrolytic copper plating. The concentration of bath components, the bath temperature, the micro-roughening of the resin, and the amount of palladium adsorption all have an impact on the plating rate of the electroless copper bath.

### 2.2.4.3. Metallization with Electroless Copper for Microvias and High Aspect Ratio Through-Holes

Securing metallization for blind vias or smaller holes with diameters of 4 mils or less, and

through-hole aspect ratios (AR) of 10:1 or greater, is a difficult task. The ability to maintain appropriate process solution flow in the through-holes, sufficient palladium adsorption on the resin and glass, and the ability to minimise and remove hydrogen gas bubbles that occur as a by-product of the electroless copper deposition are all critical success criteria. Gas bubbles created as a result of hydrogen gas formation are frequently blamed for small hole voiding, particularly in vias with a high aspect ratio and blind vias that are very small. The electroless deposition reaction shown below demonstrates that the creation of H2 gas can sometimes become caught in the via, preventing copper from being deposited:

$$Cu^{2+} + 2HCHO + 4OH \longrightarrow Cu^{+} + 2HCOO^{-} + 2H_{2}$$

It is possible to effectively fill a high AR via by the use of an adequate volume of hydrogen gas during this reaction. The result can be voided, thin and/or irregular plating. The equipment set-up, when the electroless plating process is performed in the horizontal mode, must be agitated properly in order to displace gas bubbles from the via during the plating process. Plated sample should be agitated both vertically and horizontally continuously and the sample has to be flipped in regular intervals since reaction simultaneously occurs on the other side of the board. For high aspect ratio vias, providing a mechanism of refilling chemical reactants into the via while displacing the material (reactants and by-products) that remains is a difficulty. It is vital to expel the gas bubble before it has a chance to develop a void. Schematic representation of electroless plating is given in Figure 9.

Figure 9 Schematic representation of electroless plating.

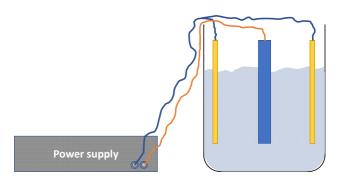

#### 2.2.5. Direct Current Plating Theory

Direct Current (DC) plating is by far the most common and oldest method of electroplating, having existed for hundreds of years. Copper baths containing sulfuric acid are frequently utilised in the fabrication of printed circuit boards, and the configuration of the plating setup in the simplest form is given in Figure 10. To impact the formation of grain structure, grain refiners, wetting agents, and brighteners are added to the basic electrolyte mixture of water, copper sulphate, and sulfuric acid. Electric field is used to redirect copper ions away from the solution during electroplating. To maintain a steady level of copper ion concentration, a solution of copper metal is dissolved in the electrolyte. When an electric current is delivered to a surface, the following reactions take place at the copper anode and sample cathode respectively:

$$Cu_{(s)} --> Cu^{+2}_{(aq)} + 2 e^{-}$$

$$Cu^{+2}_{(aq)} + 2 e^{-} --> Cu_{(s)}$$

Figure 10 Schematic representation of direct current plating setup

#### 2.3. Fine Line Imaging and Etching

This chapter is primarily concerned with image transfer processes, such as resist lamination, resist spinning, resist stripping, and etching fine lines, equipment, and materials for fine-line image transfer.

#### 2.3.1. The Process of Image Transfer

HDI imaging requires significantly more severe controls than standard print and etch applications. To obtain finer lines and gaps, smaller via pads on vias, and plated throughholes, increased vigilance in terms of phototool quality, imaging parameters, and surface preparation is necessary.

#### 2.3.2. The Typical Image Transfer Procedure

At the moment, contact printing is the most often used technique for photolithography of PWBs. Radiation in non-exposure zones is one of the most critical issues that can develop in contact printing, particularly with fine-line boards. The other is a representation of the board's dirt, defects, or other unexpected characteristics. While projection imaging and laser direct imaging have the potential to address some of these concerns, they are not yet widely used in cleanroom environments. This chapter contains a plethora of supplementary information on image transfer operating methods, equipment, and material selection for the full range of image transfer procedures.

#### 2.3.3. Fine-line Adhesion Resist

Fine-line and, by default, extremely dense circuit characteristics necessitate an integrated imaging technique. In this regard, the experimenter exercises extreme caution to

guarantee that the resist adheres to the copper surface. While the next item discusses the resist lamination parameters and their relative importance for adhesion, it is also necessary to examine the surface preparation of the copper foil prior to the lamination process.

#### 2.3.4. Lamination of Dry Film Photoresist

Thermal transfer from the rolls to the resist/copper interface is performed by passing heat through the polyester film coversheet and resist to ensure proper resist to copper conformation and adhesion. Thermally heated rolls can be manufactured in a variety of ways, including using cartridge heaters or putting surface heaters to the inside surface of a hollow roll. Other laminators use an infrared source attached to the laminator to heat the roll's exterior surface. When it comes to achieving the appropriate lamination of the resist, pressure is significantly more important than temperature; nonetheless, temperature is critical for reducing the resist's viscosity and therefore increasing flow. [6]

#### 2.3.5. Spin Coating of Liquid Photoresist

According to standard procedure, a few millilitres of resist is placed (dispensed) on a substrate that has been rotated at a rate of several thousand revolutions per minute either prior to or shortly after. Centrifugal force causes the dispensed resist to spread uniformly to the desired film thickness, and any excess resist is spun away from the substrate's perimeter. Meanwhile, a small amount of solvent is emitted from the resist film, limiting its thinnability on the one hand and making it sufficiently stable to withstand the handling of the coated PCBs on the other.

#### **2.3.6.** Etching

The chemical and mechanical components of etching are given new meaning when HDI is used since the aspect ratio of etched lines and copper thickness is getting close to one in some designs. Because the etching chemical may result in severe undercutting as well

as the loss or lifting of the resist, the experimenter must ensure that the resist adheres strongly to the copper surface prior to etching. Numerous issues arise when etching, some of which are interconnected and others that are distinct. Process optimization may have beneficial impacts in one or more of the above-mentioned problematic areas.

#### **2.3.6.1.** Etch Undercut

First and foremost, while addressing etch undercut, it is important to remember that the wet etching of PWBs is isotropic. In other words, one can see both a lateral attack on the copper traces as well as an attack on the copper in the z-axis direction on the copper. Even when equipment and process modifications are made, the lateral undercut does not disappear completely.

# 3. DEVELOPMENT AND OPTIMIZATION OF PREPREG COPPER LAMINATION PROCESS

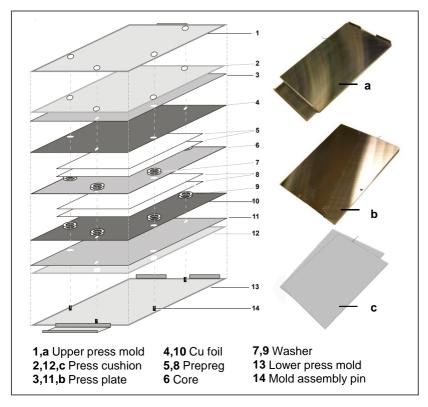

The lamination of 18 µm thick copper foils to the prepreg surface is achieved by a process based on hot pressing (Figure 11). For the lamination process, the optimum temperature and pressure values between 150-200°C and 200-400 psi were determined experimentally. Desktop LPKF Multipress S press device, which was used for these processes and which can offer 9 different temperature, pressure and time profiles with microprocessor support, had been used. Mechanical roughening of the copper surface in the interlayers, chemical oxidation [7], [8] or surface modification with plasma processes [9] are involved in HDI PCB production processes to increase adhesion. Low roughness profile copper foils showed sufficient resistance to delamination on prepreg surface: delamination or surface defects did not occur on copper traces during the multistep fabrication process.

In a typical multi-layer press process setup, from top to bottom as shown in Figure 11: upper mold part, upper press cushion, upper press plate, copper foil, prepreg, core-core, prepreg, copper foil, lower press plate, lower press shroud, and lower die piece line up throughout the assembly.

Figure 11 Typical multilayer press process setup.

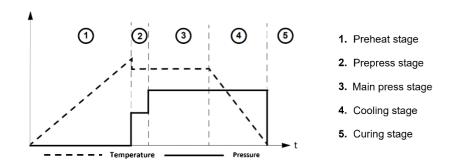

Figure 12 Press profile: Temperature and pressure over time.

The pressing process consists of five steps: preheating, prepressing, main pressing, cooling and curing. For each step, the optimal values for the pressure, temperature and time parameters is given in Table 1 for a 10 cm by 10 cm stackups to be processed and the press profile required for a successful lamination process is given in obtained (Figure 30).

**Table 1** Press profile values for each of the five stages of lamination.