# H.264 BASELINE VIDEO ENCODER IMPLEMENTATION AND OPTIMIZATION ON TMS320DM642 DIGITAL SIGNAL PROCESSOR

by MEHMET GÜNEY

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabancı University Fall 2006

# H.264 BASELINE VIDEO ENCODER IMPLEMENTATION AND OPTIMIZATION ON TMS320DM642 DIGITAL SIGNAL PROCESSOR

| APPROVED BY:      |                                   |  |

|-------------------|-----------------------------------|--|

|                   |                                   |  |

|                   |                                   |  |

|                   | Assist. Prof. Dr. Ayhan Bozkurt   |  |

|                   | (Thesis Supervisor)               |  |

|                   | Assist. Prof. Dr. İlker Hamzaoğlu |  |

|                   | Assist. Prof. Dr. Hasan Ateş      |  |

|                   | Assist. Prof. Dr. Ahmet Onat      |  |

|                   | Assist. Prof. Dr. Mehmet Keskinöz |  |

|                   |                                   |  |

|                   |                                   |  |

| DATE OF APPROVAL: |                                   |  |

© Mehmet Güney 2006 All Rights Reserved

#### **ABSTRACT**

Digital video encoding plays an important role in many applications such as digital surveillance systems, video conference systems as well as digital TV. In this thesis, a H.264 baseline encoder is implemented on Texas Instruments TMS320DM642 digital signal processor.

The TMS320DM642 is a high-performance digital media processor with 2-level memory/cache hierarchy and very-long-instruction-word (VLIW) architecture. The proposed encoder system consists of almost all parts of standard H.264 baseline encoder except quarter-pel motion compensation and error resiliency tools such as Arbitrary Slice Ordering (ASO) and Flexible Macroblok Order (FMO). Instead of quarter-pel motion compensation, integer-pel motion estimation and compensation for both Luminance and Chrominance samples is implemented.

The complete H.264 encoder system is verified to work on both computer and DM642 EVM (Evaluation Module) platform. Basically, the encoder takes the input of a QCIF video sequence (YUV) and converts it to the standard compressed H.264 AnnexB file format. The encoder is fully compliant with the standard H.264 JM Decoder.

The reconstructed video, which is exactly the same with the output of the standard JM H.264 decoder, is being displayed on a TV screen. In addition, by making use of the TI development tools, performance of the complete encoder system is analyzed for real-time applications.

Finally, memory optimization, code optimizations and compiler optimizations are applied to the encoder for higher performance. The proposed H.264 encoder is able to encode, display and store 26.7 QCIF frames per second.

## ÖZET

Sayısal video kodlama sayısal gözetim, video konferans sistemleri ve sayısal televizyon gibi birçok uygulamalarda önemli rol oynar. Bu tezde, H.264 taban profili video kodlayıcı Texas Intruments TMS320DM642 Sayısal Sinyal İşleyici üzerinde gerçeklenmiştir.

TMS320DM642 2-seviyeli hafıza/önbellek hiyerarşisine ve çok uzun komut kelimesi (VLIW) mimarisine sahip yüksek-performanslı bir sayısal sinyal işleyicidir. Burada sunulan kodlayıcı sistem, çeyrek piksel hareket dengeleme, rastgele dilim sıralayıcı ve esnek makro-blok sıralayıcı gibi hata esnekliği araçları hariç standart H.264 taban video kodlayıcının içerdiği hemen hemen tüm kısımları içermektedir. Çeyrek piksel hareket dengeleme yerine, hem ışıklılık hem de renklilik değerleri için tam sayı piksel hareket dengeleme gerçeklenmiştir.

H.264 kodlayıcı sistemin tamamının hem bilgisayar hem de DM642 EVM (Değerlendirme Modülü) üzerinde çalıştığı doğrulanmıştır. Esas olarak, kodlayıcı QCIF video serisini (YUV) alır ve onu sıkıştırılmış standart H.264 AnnexB dosya şekline dönüştürür. Kodlayıcı, kabul edilen H.264 JM çözücü ile tamamen uyumludur.

Yeniden oluşturulmuş video, standart JM H.264 çözücüsünün çıktısıyla tamamen aynıdır ve bu video televizyon ekranında görüntülenir. Buna ek olarak, TI geliştirme araçları kullanılarak, kodlayıcı sistemin bütününün performansı gerçek-zamanlı uygulamalar için analiz edilmiştir.

Son olarak, daha yüksek performans için kodlayıcıya hafıza iyileştirmeleri, kod dönüşümleri ve derleyici iyileştirmeleri uygulanmıştır. Sunulan H.264 kodlayıcı saniyede 26.7 adet QCIF çerçevesini kodlayabilme, görüntüleme ve kaydetme yeteneğindedir.

To my family...

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my supervisor Dr. Ayhan Bozkurt who gave me the chance to join Sabancı University and participate in this project. I appreciate very much for his valuable interest, continuous support and guidance.

Also I would like to thank Dr. Ilker Hamzaoğlu and Dr. Hasan Ates for assisting me during the H.264 project.

I would like to thank Dr. Ahmet Onat and Dr. Mehmet Keskinoz for participating in my thesis jury.

I would also like to thank my partners in H.264 project: Sinan Yalcin, Ozgur Tasdizen, Esra Sahin, and Mustafa Parlak.

Lastly, I would like to thank all my friends and my students at Sabanci University.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IV                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| ÖZET                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V                                   |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VIII                                |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X                                   |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X                                   |

| ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | XIII                                |

| CHAPTER 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                   |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                   |

| 1.1 IMPLEMENTATION COMPLEXITY                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                   |

| CHAPTER 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                   |

| H.264 OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                   |

| 2.1 THE SPECIFIC CODING PARTS OF H.264 2.2 ENCODER COMPLEXITY. 2.3 COMPARISON OF H.264 WITH OTHER VIDEO CODING STANDARDS 2.4 DESCRIPTION OF H.264 2.4.1 Network Abstraction Layer (NAL) 2.4.2 Video Coding Layer (VCL) 2.4.2.1 Intra Prediction 2.4.2.2 Inter Prediction 2.4.2.2.1 Hierarchical Three Step Search 2.4.2.2.2 Motion Vector Prediction 2.4.2.2.3 Transform and Quantisation 2.4.2.2.4 Coded Block Pattern (CBP) 2.4.2.2.5 Entropy Coding 2.4.2.2.6 Deblocking Filter | 11 12 13 13 13 15 15 20 20 20 21 21 |

| CHAPTER 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

| TEXAS INSTRUMENTS TMS320DM642 DSP                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                  |

| 3.1 OVERVIEW OF DM642 DSP CORE  3.1.1 Register Files. 3.1.2 Functional Units 3.1.3 Register File Paths 3.1.4 Memory, Load and Store Paths 3.1.5 Additional Functional Unit Hardware 3.1.6 DM642 Cache Architecture                                                                                                                                                                                                                                                                 |                                     |

| CHAPTER 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                  |

| SOFTWARE DEVELOPMENT AND DSP REALIZATION OF ENCODER                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                  |

| 4.1 SOFTWARE DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                  |

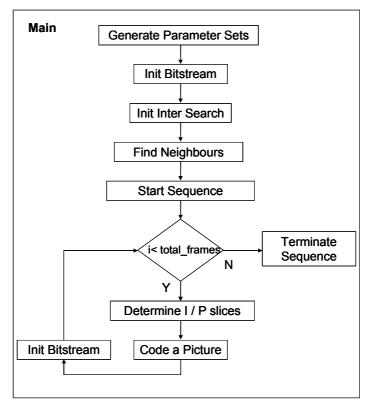

| 4.1.1.1 Main                                                        | 33 |

|---------------------------------------------------------------------|----|

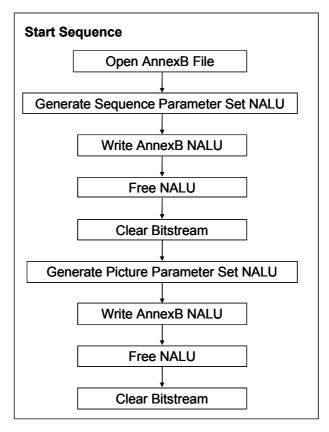

| 4.1.1.2 Start Sequence                                              | 34 |

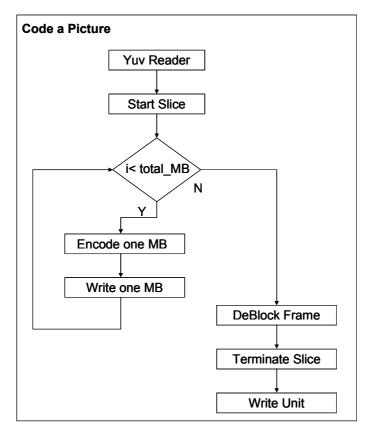

| 4.1.1.3 Code a Picture                                              |    |

| 4.1.1.4 Encode one Macroblock                                       |    |

| 4.1.1.5 Intra 4x4 Mode Decision                                     |    |

| 4.1.1.6 Intra 16x16 Mode Decision                                   |    |

| 4.1.1.7 Motion Search                                               |    |

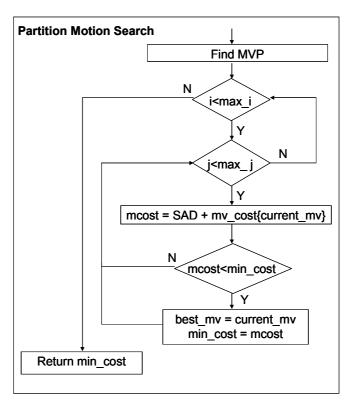

| 4.1.1.8 Partition Motion Search                                     |    |

| 4.2 DSP REALIZATION                                                 |    |

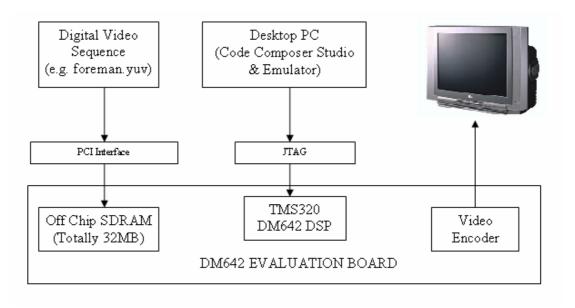

| 4.2.1. Design of Experimental Setup                                 |    |

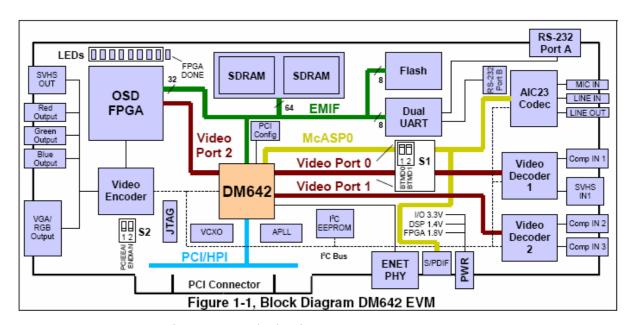

| 4.2.1.1 TMS320DM642 Evaluation Module (EVM)                         |    |

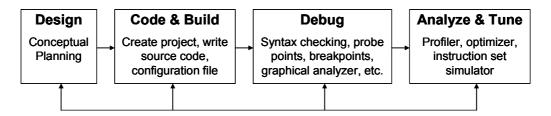

| 4.2.2 Code Generation using Code Composer Studio                    |    |

| 4.2.2.1 DSP/BIOS Real Time Kernel                                   |    |

| 4.2.2.2 Sychronized Communication (SCOM) Module                     |    |

| 4.2.3 Testing and Verification                                      | 51 |

| 4.2.4 Performance Analysis and Tuning                               | 52 |

| CHAPTER 5                                                           | 52 |

|                                                                     |    |

| PERFORMANCE ANALYSIS AND OPTIMIZATION                               | 53 |

| 5.1 TEST ENVIRONMENT.                                               | 53 |

| 5.2 SOFTWARE OPTIMIZATION                                           | 54 |

| 5.2.1 Optimization without Algorithm/Memory Optimizations           | 55 |

| 5.2.2 Optimization with Algorithm/Memory Optimizations              | 57 |

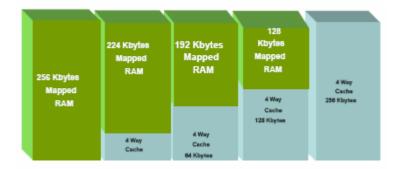

| 5.2.2.1 L2 Cache / Ram Partitioning                                 | 58 |

| 5.2.2.2 Improvements in Memory Access Pattern and Encoder Algorithm | 59 |

| 5.2.2.2.1 Buffering Macroblock Data                                 | 59 |

| 5.2.2.2.2 Improvements for Intra 4x4 Prediction                     | 60 |

| 5.2.2.2.3 Improvements for Intra 16x16 Prediction                   | 61 |

| 5.2.2.2.4 Improvements for Motion Search                            |    |

| 5.2.2.3 Allocation of Compiler Output Sections                      |    |

| 5.2.2.4 Code Optimizations                                          |    |

| 5.2.2.4.1 Fast Library Functions                                    |    |

| 5.2.2.4.2 Compiler Intrinsics                                       | 67 |

| 5.2.2.4.3 Function Inlining.                                        |    |

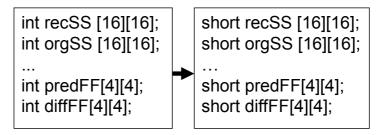

| 5.2.2.4.4 Changing Variable Types                                   | 68 |

| 5.2.2.5 Utilizing Compiler Options for Optimization                 | 69 |

| 5.2.2.5.1 File-Level Optimization ( -o3 Option)                     |    |

| 5.2.2.5.2 Assuming No Bad Memory Alias Occurs (-mt option)          | 70 |

| 5.2.2.6 Allocating Frequently Used Data in the Internal Memory      |    |

| 5.3 SUMMARY OF SOFTWARE OPTIMIZATION                                |    |

| 5.4 PSNR AND COMPRESSION RATE MEASUREMENTS                          | 74 |

| CHAPTER 6                                                           | 76 |

| CONCLUSION AND FUTURE WORK                                          | 76 |

# LIST OF FIGURES

| Figure 2.1: Coding parts of H.264 with respect to the profiles                | 9  |

|-------------------------------------------------------------------------------|----|

| Figure 2.2: The structure of a H.264 coded video sequence                     | 14 |

| Figure 2.3: Block diagram of H.264 encoder                                    | 15 |

| Figure 2.4: Macroblock partitioning in inter prediction                       | 18 |

| Figure 2.5: Zig Zag scan order                                                | 22 |

| Figure 3.1: TMS320C64x DSP Block Diagram                                      | 24 |

| Figure 3.2: C64x Data Cross Paths                                             | 26 |

| Figure 3.3: C64x Memory Load and Store Paths                                  | 27 |

| Figure 3.4: DM642 L1/L2 Cache                                                 | 29 |

| Figure 3.5: Partitioning internal memory into L2 cache/ram                    | 29 |

| Figure 4.1: Flow graph of main                                                | 33 |

| Figure 4.2: Flow graphs of start sequence                                     | 35 |

| Figure 4.3: Flow graph code a picture                                         | 36 |

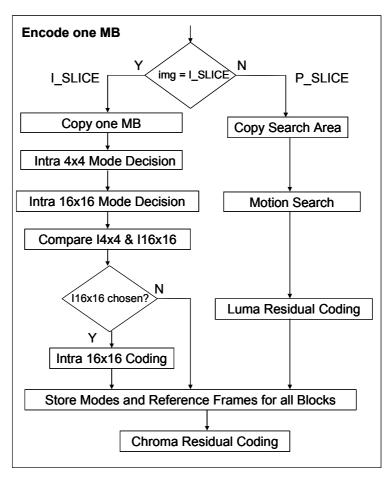

| Figure 4.4: Flow graph of encode one macroblock                               | 37 |

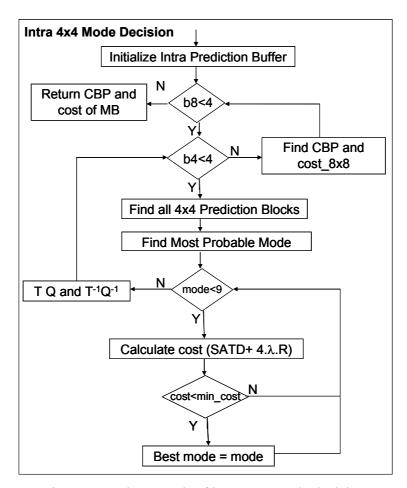

| Figure 4.5: Flow graph of intra 4x4 mode decision                             | 40 |

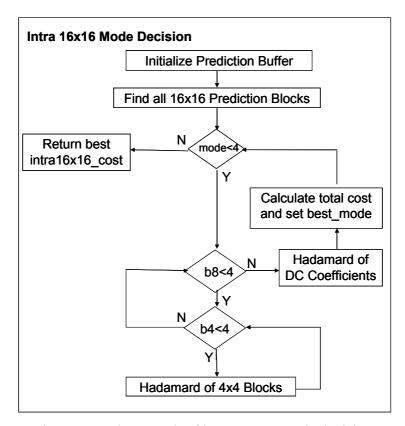

| Figure 4.6: Flow graph of intra 16x16 mode decision                           | 42 |

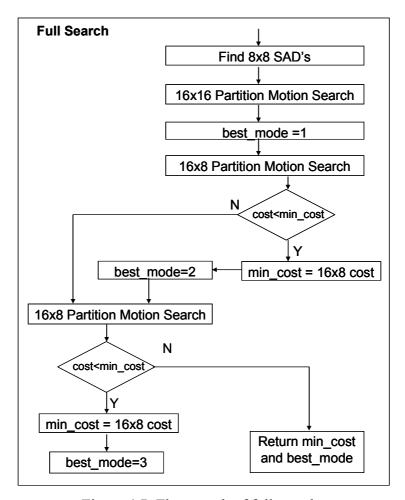

| Figure 4.7: Flow graph of full search                                         | 44 |

| Figure 4.8: Flow graph of partition motion search                             | 45 |

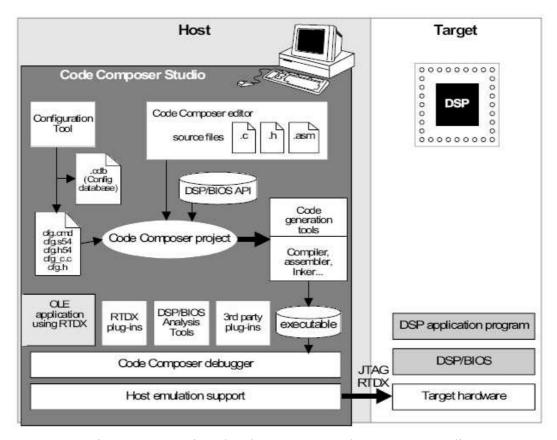

| Figure 4.9: A project development cycle using Code Composer Studio            | 46 |

| Figure 4.10: The experimental setup                                           | 47 |

| Figure 4.11: Block Diagram DM642 EVM                                          | 48 |

| Figure 4.12: Project development on Code Compose Studio                       | 49 |

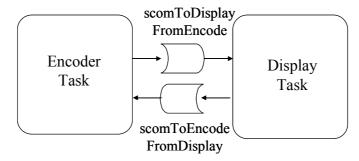

| Figure 4.13: Synchronized communication between encoder task and display task | 51 |

| Figure 4.14: Elecard stream eye's output                                      | 52 |

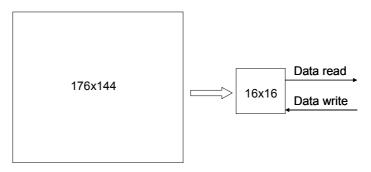

| Figure 5.1: MB Data read/write is performed on the 16x16 macroblock buffer    | 59 |

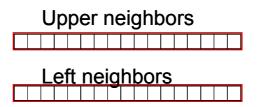

| Figure 5.2: Buffers for intra 4x4 prediction                                  | 60 |

| Figure 5.3: Buffer for intra 16x16 prediction                                 | 61 |

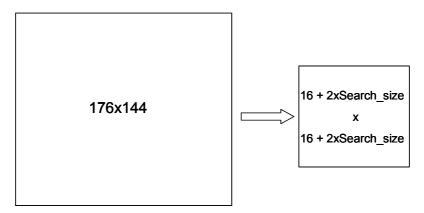

| Figure 5.4: Search window array is created for motion search                     | 62 |

|----------------------------------------------------------------------------------|----|

| Figure 5.5: Mixed Source/Assembly view of the function SATD                      | 65 |

| Figure 5.6: Original code and its transformation into library function           | 66 |

| Figure 5.7: Original code and its transformation into library function           | 66 |

| Figure 5.8 The array is aligned to double word boundary                          | 66 |

| Figure 5.9: Original code and its transformation by using intrinsics             | 67 |

| Figure 5.10: Original code and its transformation by using intrinsics            | 67 |

| Figure 5.11: The integer variables are replaced with short variables             | 68 |

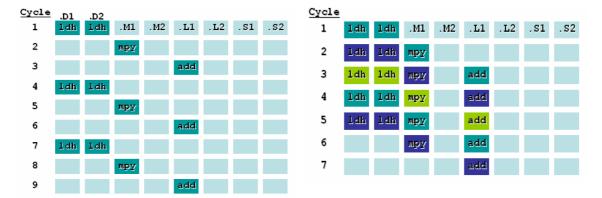

| Figure 5.12: Before software pipelining                                          | 70 |

| Figure 5.13: After software pipelining                                           | 70 |

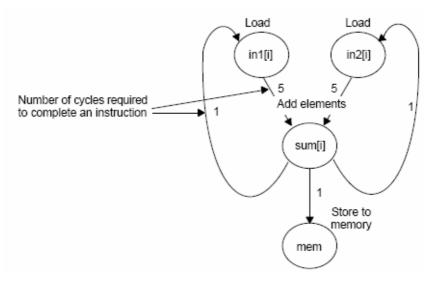

| Figure 5.14: A basic vector sum function                                         | 70 |

| Figure 5.15: Dependency graph of basic vector sum                                | 71 |

| Figure 5.16: Allocation of frequently accessed arrays to internal memory section | 72 |

# LIST OF TABLES

| Table 2.1: H.264 profiles and their application areas                          | 8  |

|--------------------------------------------------------------------------------|----|

| Table 2.2: H.264 profiles with the coding parts they include                   | 11 |

| Table 2.3: 4x4 Luma block intra prediction modes                               | 16 |

| Table 2.4: 16x16 Luma block intra prediction modes                             | 16 |

| Table 2.5 Coding of intra 4x4 prediction modes                                 | 17 |

| Table 2.6: Illustration of calculating cbp values for some coded blocks        | 21 |

| Table 5.1 Performance of the un-optimized encoder                              | 54 |

| Table 5.2: Comparison of encode_one_macroblock with write_one_macroblock       | 55 |

| Table 5.3: Performance increase with software optimizations only               | 56 |

| Table 5.4: Number of NOPs and CPU stalls after applying software optimizations | 56 |

| Table 5.5: Simulation results for different ram/cache partitioning             | 58 |

| Table 5.6: Performance increase with algorithm/memory access improvements only | 62 |

| Table 5.7: Output sections of compiler                                         | 63 |

| Table 5.8: Compiler Options for Higher Performance                             | 69 |

| Table 5.9: Total CPU cycle counts according to the performed optimization      | 73 |

| Table 5.10: Compression efficieny of the encoder                               | 75 |

#### **ABBREVIATIONS**

JVT Joint Video Team

DSP Digital Signal Processor

JM Joint Model

MPEG Motion Picture Experts Group

ISO/IEC International Organization of Standardization, International

**Electrotechnical Commission**

AVC Advanced Video Coding VCEG Video Coding Experts Group

ITU-T International Telecommunication Union, Telecommunications

Standardization Sector

NAL Network Adaptation Layer

VCL Video Coding Layer

MB Macroblock

CIF Common Intermediate Format

QCIF Quarter Common Intermediate Format EDMA Enhanced Direct Memory Access UVLC Universal Variable Length Codeword

CABAC Context Based Adaptive Binary Arithmetic Coding

CAVLC Context Based Adaptive Variable Length Coding

RTP Real Time Transport Protocol UDP User Datagram Protocol

IDR Instantaneous Decoding Refresh

PSNR Peak Signal to Noise Ratio

SAD Sum of Absolute Differences

SATD Sum of Total Absolute Differences

CBP Coded Block Pattern LSB Least Significant Bit

VLIW Very Long Instruction Word

SIMD Single Instruction Multiple Data

PCI Peripheral Communications Interface

JTAG Joint Test Access Group

I/O Input Output

SCOM Synchronized Communication CPU Central Processing Unit

CCS IDE Code Composer Studio Integrated Development Environment

TI Texas Instruments

EMIF External Memory Interface RBSP Raw Byte Sequence Payload

#### **CHAPTER 1**

#### INTRODUCTION

The need for digital video compression is certain. An uncompressed CIF (352x288) 4:2:0 video at 30 frames/sec requires 36.5Mbits/s, and 23.3 Gbytes to store one 90-minute video[1]. Compression is inevitable in order to fit digital video into affordable storages capacities and network bandwidths. H.264 is such a digital video compression standard and is now the most popular and useful one. This emerging standard offers major improvements and produces excellent picture quality with high compression rates. The fact that H.264 is not backwards compatible with other coding standards makes it a milestone in video compression technology.

H.264 provides significant improvement in digital video compression, but it also requires much computation power. Also, implementation of digital compression standards such as H.264 is not an easy task. The trend in implementing video and image processing algorithms is towards using digital signal processors because DSPs are now fast enough and they offer reprogrammable designs. The programmability feature is especially important because it provides us with the ability to tailor video encoder for application needs. One can make innovations in video processing by making use of DSP's flexibility. Moreover, software reuse enables video market to limit design costs. Briefly, H.264 encoder and the design of H.264 especially on a programmable platform is so valuable.

In this thesis, an implementation of H.264 Baseline Encoder on TMS320DM642 digital signal processor is presented. The proposed encoder system includes almost all features of a standard H.264 baseline encoder and its conformance with the H.264 standard is verified by using the H.264 JM Reference Software[2]. For the motion search, full search and hierarchical three step search algorithms are both implemented. The performance results for QCIF video format have shown that real-time execution of

encoder with full search algorithm is possible. Therefore full search is selected for the motion search part.

Besides the software development of H.264, software optimization is also investigated in this thesis. Optimization techniques such as algorithm/system optimization, refinements in memory access pattern, code optimizations and compiler optimizations are experimented. Although the un-optimized encoder's performance is about 3.1 fps, it is shown that the performance can be increased to 26.7 fps for QCIF.

The work proposed in this thesis proved that the huge number of memory accesses is the bottleneck in a video coding system. Unless the memory accesses are optimized, it may not be possible to achieve a real time solution even other optimizations are applied.

The proposed encoder is capable of compressing a QCIF video input into H.264 AnnexB file format. The complete encoder system is realized by using TMS320DM642 Evaluation Module(EVM)[3], a standard definition TV for displaying the reconstructed frames and a desktop computer for storage of output bit-file.

## 1.1 Implementation Complexity

H.264/AVC is a new codec generation featuring an outstanding coding efficiency, but its cost-effective realization is a big challenge. H.264/AVC leads to an average 40% bit saving plus 1-2 PSNR gain compared to previous video coding standards. In this way, it represents the enabling technology for the widespread diffusion of multimedia communication over wired and wireless transmission networks such as xDSL, 3G mobile phones and WLAN. However, this outstanding performance comes with an implementation complexity increase of a factor of 2 for the decoder. At the encoder side, the cost increase is larger than one order of magnitude. This represents a design challenge for resource constrained multimedia systems such as wireless and/or wearable devices and high-volume consumer electronics, particularly for conversational applications (e.g., video telephony), where both the encoder and the decoder functionalities must be integrated in the user's terminal [4].

A single H.264/AVC configuration able to minimize algorithmic performance while minimizing memory and computational burdens does not exist. However, different configurations leading to several performance/cost trade-offs exist. To find these optimal configurations, and hence to highlight the bottenecks of H.264/AVC a good analysis is required. In this thesis, two motion search algorithms (full search and three step hierarchical search) are implemented in order to explore the computational complexity and performance of each. Performance results have shown that computational burden of full search is higher than three step hierarchical search. However, the performance of encoder with full search can be increased up to desired value by applying software optimization techniques.

Data transfer and storage have a dominant impact on the cost-effective realization of multimedia systems for both hardware and software-based platforms. Application specific hardware implementations have the freedom to match the memory and communication bus architectures to the application. An efficient hardware implementation exploits this to reduce area and power. On the other hand, programmable processors rely on the memory architecture that come with them. Efficient use of these resources is crucial to obtain the required speeds as the performance gap between the CPU and DRAM is growing every year [4].

The proposed implementation in this thesis achieves real time execution for QCIF format. Therefore this implementation can be used in a real world application but at low resolution applications. During this implementation at QCIF resolution, a deep exploration of H.264 implementation is done. Therefore this exploration will help us to implement H.264 at higher resolutions. Moreover, because of the flexibility and programmability of dsp implementations this design may be easily adapted for higher performance solutions. Based on this implementation, improvements to H.264 is also possible.

#### **1.2** Literature Survey

In the literature, there are examples of real time implementations of video coding algorithms. In [5], optimization of a baseline H.263 encoder on TMS320C6000 is presented. The work presented in that paper focuses on the optimization issue. They do

not write the software code but they use the University of Columbia's (UBC) H.263 encoder software. Starting from a software code written for a desktop application they obtain a real time implementation of H.263 encoder on TMS320C6701. They demonstrated that memory accesses to external memory are a significant bottleneck in the implementation of real-time embedded video systems. It is shown by simulation that most of the time is spent in data access to external memory. Their optimizations resulted in an overall speedup of 61 times over the un-optimized version. They performed optimization in two steps: efficient use of on-chip data and program memory (memory optimizations), and code optimizations of computationally intensive routines in C as well as in assembly language. The total speedup obtained with memory optimizations alone is about 29 times. With the code optimizations alone, a speedup of only 4 is achieved. The affect of code optimizations without memory optimizations is low because the effect of slow off-chip memory accesses becomes the dominant bottleneck as the code becomes more efficient in performing computations. Combination of the memory and code optimizations gives an improvement of 61 times. For the motion estimation, the macroblock and the corresponding search window are copied into internal data memory before the routine was called. In this thesis, I applied the same approach and obtained very good performance. I also copied each macroblock and neighboring pixels of the macroblock into internal data memory before the mode decision, transform, quant routines are called.

The paper called "Parallelization of a H.263 Encoder for the TMS320C80 MVP" [6] describes a real-time implementation on a multiprocessor system. Texas Instruments' TMS320C80 MVP system contains four signal processors and one RISC-processor. The main aspect of the work is parallelization of the encoder in order to exploit the computational power of the multiprocessor system. They try to increase the utilization of the processors to obtain real-time execution however their implementation is below real-time. They concluded that assembler optimizations are necessary. Usually, Implementation on parallel processor architecture gives better results but the implementation becomes so difficult. Especially, the algorithm should be divided into parts for parallel execution. Since the H.264 algorithm is a very complex one, dividing H.264 into parallely executable parts is so difficult. Moreover, the technical paper [7] shows that real-time realization of H.264 on TMS320DM642 digital signal processor is possible.

There is another study related to memory optimizations called "Memory Centric Design of an MPEG-4 Video Encoder" [8]. In this study, high-level memory optimizations are presented. They observed that motion estimation routine repeatedly access the same set of neighboring pixels. To reduce these accesses to frame size memories, a memory hierarchy is introduced for the motion estimation. Heavily used data is copied from large (frame size) to minimal intermediate memories. The solution is more efficient as soon as the cost of extra memory transfers (due to copies) is balanced by the advantage of using smaller memories.

The study called "Code Transformations for Data Transfer and Storage Exploration Preprocessing in Multimedia Processors" [9] says that platform-independent source code transformations can greatly help alleviate the data-transfer and storage bottleneck. This article also covers code rewriting techniques to improve data reuse. They claim that the code should expose maximal data reuse possibilities in order to optimize data transfer and storage. This idea can be implemented in the implementation of H.264 encoder because there is much data reuse in H.264 software. Especially, during the prediction and filtering some pixels are used repeatedly. Instead of accessing the same pixel from the frame memory, this pixel can be stored in a buffer. In other words, we can create data reuse buffers for frequently accessed data. In my H.264 implementation, I introduce buffers for intra 4x4 prediction, intra 16x16 prediction.

Finally, "Video Encoding Optimization on TMS320DM64x/C64x" summarizes the optimization techniques for video encoders on TMS32320DM64x/C64x processors [10]. These techniques include algorithm/system optimization, memory buffering optimization, enhanced direct memory access (EDMA) and cache utilization optimization. The algorithm/system optimization is performed by breaking the algorithm into loops/modules that fits into L1P cache. In this way, they avoid the huge cache miss penalty and CPU stalling. M macroblocks (MB strip) are processed at a time in each loop instead of a single macroblock. Memory buffering optimization is realized by transferring macroblock from the external memory to internal buffer. In this thesis, a similar approach is used. The proposed encoder in this thesis introduces buffers not only for macroblock data but also for intra prediction samples. The third optimization technique that is experimented in this article is the EDMA usage. EDMA is preferred to transfer code/data between L2 SRAM and off-chip memory. The last optimization technique is improving the cache performance for video coding. With the help of TI's

cache analysis tools, cache efficiency problem areas can be identified, visualized and optimized.

These articles show that video coding applications includes much parallelism. Optimization is possible with techniques such as code transformations, memory optimizations, EDMA and optimizing compiler. Most of the studies show that the bottleneck in video coding is the high number of memory accesses. In this thesis, I experienced the same problem. First, I attempted to start directly with code optimizations. However, code optimizations alone bring up to 10.4fps performance. In order to achieve better performance, algorithmic optimizations and especially improvements in memory access pattern is crucial. Thus, in the second attempt I started with improvements in algorithm and created buffers to optimize memory access pattern. After that, code optimizations and compiler optimizations gave better performance and I achieved performance up to 26.7 fps.

## 1.3 Organization of the Thesis

The organization of the thesis is as follows:

Chapter 2 starts with an overview of H.264 algorithm and specific building blocks of H.264. It also gives a comparison of H.264 with other video coding standards. The description of the algorithm is also briefly explained in chapter 2.

Chapter 3 explains the DM642 digital signal processor core. Understanding the architecture and features of this digital signal processor is necessary for achieving high performance designs.

In chapter 4, the implementation details are explained. Software development phase and software architecture is explained in this chapter. The proposed encoder is presented with software flow graphs. The developed software is transported to DSP environment. This process and the hardware setup for the encoder is also described here.

Chapter 5 gives the performance results of the proposed encoder. Memory optimizations, algorithmic transformations, code optimizations and compiler optimizations for high performance are discussed in this chapter. The compression

efficiency of the proposed encoder with respect to the PSNR is also found in this chapter.

Chapter 6 presents the conclusions and future work.

#### **CHAPTER 2**

#### **H.264 OVERVIEW**

In 1997, the ITU-T Video Coding Experts Group (VCEG) initiated the work on the H.264 standard (formerly known as the H.26L standard). The main objective behind the H.264 project was to develop a high-performance video coding standard by adopting a "back to basics" approach using simple and straightforward design with well-known building blocks. After observing the superiority of video quality offered by H.264-based software over that achieved by the existing most optimized MPEG-4 based software, ISO/IEC MPEG joined ITU-T VCEG by forming a Joint Video Team (JVT) that took over the H.264 project of the ITU-T. The JVT objective was to create a single video coding standard that would simultaneously result in a new part of the MPEG-4 standard (MPEG-4 Part 10 Advanced Video Coding (AVC)) and a new ITU-T Recommendation (H.264) [1]. To this date, 4 major profiles of H.264 have been released. These are named as baseline, main, extended and high profiles. H.264 can be used in many application areas ranging from video conferencing to digital cinema.

Table 2.1: H.264 profiles and their application areas

| Profile                     | Typical Applications                              |

|-----------------------------|---------------------------------------------------|

| Baseline                    | Video Conferencing and Mobile Applications        |

| Main                        | Digital Storage Media and Television Broadcasting |

| Extended                    | Streaming and Mobile Video Applications           |

| High Profile                | Studio Editing, Post Processing, Digital Cinema   |

| (Fidelity Range Extensions) |                                                   |

## 2.1 The Specific Coding Parts of H.264

The common coding parts of H.264 profiles are listed as:

- 1. I slice (Intra-coded slice): The coded slice by using prediction only from decoded samples within the same slice.

- 2. P slice (Predictive-coded slice): The coded slice by using inter prediction from previously-decoded reference pictures, using at most one motion vector and reference index to predict the sample values of each block.

- 3. Context-based Adaptive Variable Length Coding (CAVLC) for entropy coding.

The baseline profile consists of these common coding parts plus some others. The complete list of coding parts for baseline profile and their explanations are:

- 1. Common Parts: I slice, P slice, CAVLC

- 2. FMO (Flexible macroblock order): Macroblocks may not necessarily be in the raster scan order. The map assigns macroblocks to a slice group.

- 3. ASO (Arbitrary Slice Order): The macroblock address of the first macroblock of a slice of a picture may be smaller than the macroblock address of the first macroblocks some other preceding slice of the same coded picture.

- 4. RS (Redundant Slice): This slice belongs to the redundant coded data obtained by same or different coding rate, in comparison with previous coded data of same slice.

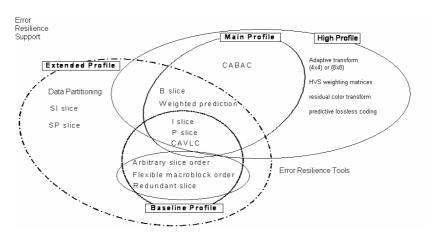

Figure 2.1: Coding parts of H.264 with respect to the profiles.[1]

If a comparison between the profiles is done, baseline is the simplest one. The main profile allows an additional reduction in bandwidth over the Baseline profile through mainly Bi-directional prediction (B-pictures), Context Adaptive Binary Arithmetic Coding (CABAC) and weighted prediction.

B-pictures provide a compression advantage as compared to P-pictures by allowing a larger number of prediction modes for each macroblock. Specifically, bipredictive coding modes are available for each partition of the macroblock. Here, the partition is formed by averaging the sample values in two reference blocks, generally, but not necessarily using one reference block that is forward in time and one that is backward in time with respect to the current picture. In addition, "Direct Mode" prediction is supported, in which the motion vectors for the macroblock are interpolated based on the motion vectors used for coding the co-located macroblock in a nearby reference frame. Thus, no motion information is transmitted. By allowing so many prediction modes, the prediction accuracy is improved, often reducing the bit rate by 5-10%.

Weighted Prediction allows the modification of motion compensated sample intensities using a global multiplier and a global offset. The multiplier and offset may be explicitly send, or implicitly inferred. The use of the multiplier and the offset aims at reducing the prediction residuals due, for example, to global changes in brightness, and consequently, leads to enhanced coding efficiency for sequences with fades, lighting changes, and other special effects.

Context Adaptive Binary Arithmetic Coding (CABAC) makes use of a probability model at both the encoder and decoder for all the syntax elements (transform coefficients, motion vectors, etc.). To increase the coding efficiency of arithmetic coding, the underlying probability model is adapted to the changing statistics within a video frame, though a process called context modeling.

The context modeling provides estimates of conditional probabilities of the coding symbols. Utilizing suitable context models, given inter-symbol redundancy can be exploited by switching between different probability models according to already coded symbols in the neighborhood of the current symbol to encode. The context modeling is responsible for most of CABAC's 10% savings in bit rate over the Baseline entropy coding method (universal and context adaptive VLC) [1].

The coding parts according to the profiles can be summarized as in table 2.2. The baseline encoder proposed in this thesis includes all coding parts except error resiliency

tools and quarter-pel motion compensation. Quarter-pel motion compensation is replaced with integer-pel. In the future, quarter-pel support will be added.

Table 2.2: H.264 profiles with the coding parts they include.

|                                                     | Main | Extended | High | Baseline | Proposed<br>Baseline<br>Encoder |

|-----------------------------------------------------|------|----------|------|----------|---------------------------------|

| I Slices                                            | X    | X        | X    | X        | X                               |

| P Slices                                            | X    | X        | X    | X        | X                               |

| Deblocking Filter                                   | X    | X        | X    | X        | X                               |

| Variable Block Size                                 | X    | X        | X    | X        | X                               |

| <sup>1</sup> / <sub>4</sub> Pel Motion Compensation | X    | X        | X    | X        |                                 |

| CAVLC/UVLC                                          | X    | X        | X    | X        | X                               |

| Error Resilience Tools                              |      | X        |      | X        |                                 |

| (Flexible MB Order, ASO,                            |      |          |      |          |                                 |

| Redundant Slices)                                   |      |          |      |          |                                 |

| SP/SI Slices                                        |      | X        | X    |          |                                 |

| B Slice                                             | X    | X        | X    |          |                                 |

| Interlaced Coding                                   | X    | X        | X    |          |                                 |

| CABAC                                               | X    |          |      |          |                                 |

| Data Partitioning                                   |      | X        |      |          |                                 |

| Weighted Prediction                                 | X    | X        |      |          |                                 |

## 2.2 Encoder Complexity

The H.264 standard is significantly more complex than any of the previous coding standards [23]. Motion estimation, for instance, makes use of 7 block sizes from 16x16 to 4x4. Consequently, the H.264 encoder is expected to be significantly more demanding in terms of computations and memory requirements. Moreover, the development of an embedded encoder/decoder where the internal memory size is limited is a challenging task. [10]

According to [7], in order to implement an H.264 Main profile encoder, multiple DSP encoder architectures needed due to the high complexity. But designing a multiple DSP encoder is not an easy task. Multiple processor architecture brings a couple of problems such as the partitioning of the encoder. Partitioning may also have impact on the quality of the encoder. Another issue to be considered in a multiple DSP design is the handling of inter-DSP communication [7].

To summarize, the high complexity of the H.264 video coding standard makes it difficult to implement but provides us with the video quality at low bit rates especially when compared with previous compression standards.

## 2.3 Comparison of H.264 With Other Video Coding Standards

H.264 is not backward compatible with previous standards. The new compession techniques used in H.264 bring great compression efficiency to it. H.264 offers up to 2x compression compared with MPEG-4 simple profile.

An important concept of H.264 is the separation of the system into two layers: a video coding layer (VCL), providing the high-compressed representation of data, and a network abstraction layer(NAL), packaging the coded data in an appropriate manner based on the characteristics of the transmission network [4]. H.264 gives superior error resilience due to VCL and NAL layer enhancements and error resiliency tools. VCL enables efficient transmission of video data on network by representing video content in integer number of byte units. H.264 is very adaptive to different applications from digital TV to video conferencing. It may operate with low delay constraints for real-time applications or higher delay constraints for applications which require more processing power, such as video content storage

The introduction of the switching mechanism enables fast random access for video decoders. SP and SI frames may be used for switching from low bit rate to high bit rate in the same video stream according to the available bandwidth.

The basic building blocks of the H.264 encoder are similar with the previous standards'. The transform, quantization, motion estimation, motion compensation and entropy coding are found on almost all video coding standards. However, there are major improvements done inside these basic building blocks. For instance, H.264 uses 16x16 or 4x4 block sizes in the intra coding part. Another improvement in H.264 is the addition of new intra prediction modes. For the inter prediction, there are 7 block types changing from 16x16 to 4x4. Moreover, luma motion vectors have quarter pel resolution whereas chrominance vectors have 1/8 pixel. This results in increased precision of motion vectors. Context Adaptive Variable Length Coding (CAVLC) and

Context Based Adaptive Arithmetic Coding (CABAC) are also new. Lastly, in H.264 loop filter is introduced to reduce the blocking artifacts.

## 2.4 Description of H.264

H.264 has a layered structure. It has two different layers one of which is Network Abstraction Layer (NAL) and the other is Video Coding Layer (VCL). The NAL layer abstracts the VCL data. It includes the header information about the VCL format. NAL is appropriate for conveyance by the transport layers or store media. NAL unit (NALU) is a generic format which is used in both packet based and bit-streaming systems. Second layer which is VCL is the core coding layer. VCL concentrates on attaining maximum coding efficiency rather than the transportation.[21]

## 2.4.1 Network Abstraction Layer (NAL)

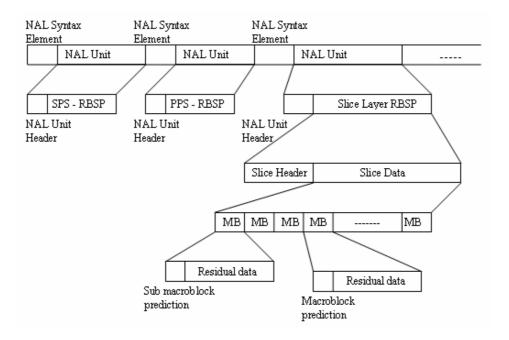

A coded H.264 video sequence consists of a series of Network Abstraction Units (NALUs), each containing an RBSP (Raw Byte Sequence Payload). An example of a typical sequence of RBSP units is shown in figure 2.2. Each of these units is transmitted in a separate NAL unit. The header of the NAL unit (one byte) signals the type of RBSP unit and the RBSP data makes up the rest of the NAL unit.

H.264 introduces the concept of parameter sets which contain information that can be applied to a large number of coded pictures. A sequence parameter set contains parameters which are applied to a complete video sequence. Similarly, a picture parameter set contains parameters which are applied to one or more decoded pictures within a sequence.

Parameters in the Sequence Parameter Set include an identifier, limits on frame numbers and picture order count, the number of reference frames that may be used in decoding, the decoded picture height and width and the choice of progressive or interlaced (frame or field) coding.

Figure 2.2: The structure of a H.264 coded video sequence.

Each Picture Parameter Set includes an identifier, a selected sequence parameter set id, a flag to select VLC or CABAC entropy coding mode, the of slice groups in use, the number of reference pictures in list0 and list1 that may be used for prediction, initial quantizer parameters and a flag indicating whether the default deblocking filter parameters are to be modified.

In a typical application, coded video is required to be transmitted or stored together with associated audio tracks and side information. It is possible to use a range of transport mechanisms to achieve this, such as Real Time Protocol and User Datagram Protocol (RTP/UDP).

Earlier video coding standards such as MPEG-1, MPEG-2 and H.263 did not explicitly define a format for storing compressed audiovisual data in a file. The MPEG-4 file format and AVC File Format are designed to store MPEG-4 Audio Visual and H.264 Video data respectively. Both formats are derived from the ISO Base Media File Format, which in turn is based on Apple Computer's Quick Time Format. In my implementation, the encoder produces an output bitstream in Annex B byte stream file format which is described in the ITU-T H.264 Recommendation [11].

## 2.4.2 Video Coding Layer (VCL)

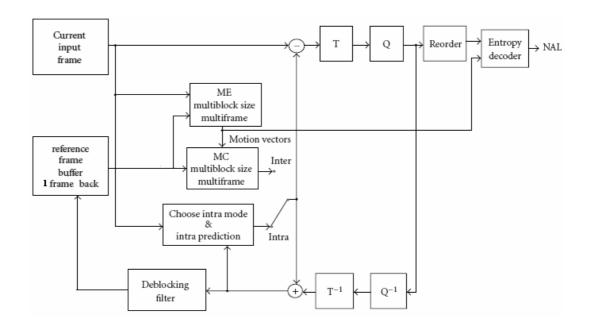

Basically, the coding of a macroblock is obtained with the flow shown in the figure 2.3.

Figure 2.3: Block diagram of H.264 encoder

## 2.4.2.1 Intra Prediction

Intra prediction process exploits the spatial redundancy between adjacent macroblocks in a frame. Intra predicted frames usually have better PSNR than inter coded frames; however they require much more bits to encode and decrease compression rate. Therefore less number of frames of a video sequence is coded in intra that in inter. During the encoding process, propagation errors occur due to the successive inter-coded pictures. At that time, an intra-coded picture should be inserted in order to reduce the propagation of errors to the next predictions. Subsequent inter prediction is done based on this new intra picture. In other words, this intra-coded picture refreshes the prediction and is therefore called Instantaneous Decoding Refresh (IDR) picture. In my implementation, the IDR period can be determined by a parameter inside the software. During the tests it is fixed at 20; meaning that every one frame out of 20 is intra-coded.

The inputs of intra prediction process are previously reconstructed samples prior to the deblocking filter process from neighboring macroblocks. A prediction block is formed in this process and it is subtracted from the current block before encoding. For the luma samples, prediction is formed for each 4x4 block or for a 16x16 macroblock.

The intra\_4x4 mode is based on predicting each 4x4 luma block separately and is well suited for coding parts of a picture with significant detail. The intra\_16x16 mode on the other hand, performs prediction of the whole 16x16 luma block and is more suited for coding very smooth areas of a picture.

There are a total of nine optional prediction modes for intra\_4x4 luma block, four modes for intra\_16x16 luma block.

Table 2.3: 4x4 Luma block intra prediction modes

| Mode 0 : Vertical            | The upper samples are extrapolated vertically                                                 |  |

|------------------------------|-----------------------------------------------------------------------------------------------|--|

| Mode 1 : Horizontal          | The left samples are extrapolated horizontally                                                |  |

| Mode 2 : DC                  | All samples are predicted by the mean of A, B, C, D, I, J, K, L                               |  |

| Mode 3 : Diagonal Down Left  | The samples are interpolated at a 45° angle between lower left and upper samples.             |  |

| Mode 4 : Diagonal Down Right | The samples are extrapolated at a 45° angle down and to the right.                            |  |

| Mode 5 : Vertical Right      | Extrapolation at an angle of approximately 26.6° to the left of vertical.                     |  |

| Mode 6 : Horizontal Down     | Extrapolation at an angle of approximately 26.6° below horizontal.                            |  |

| Mode 7 : Vertical Left       | Extrapolation (or intrapolation) at an angle of approximately 26.6° to the right of vertical. |  |

| Mode 8 : Horizontal Up       | Interpolation at an angle of approximately 26.6° above horizontal                             |  |

Table 2.4: 16x16 Luma block intra prediction modes

| Mode 0 : Vertical   | The upper samples are extrapolated vertically.                                                                         |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Mode 1 : Horizontal | The left samples are extrapolated horizontally.                                                                        |  |

| Mode 2 : DC         | All samples are predicted by the mean of A, B, C, D, I, J, K, L.                                                       |  |

| Mode 3 : Planar     | A linear 'plane' function is fitted to the upper and left-hand samples. This works well in smoothly varying luminance. |  |

The four prediction modes of 8x8 intra chroma blocks are similar to the 16x16 luma block prediction modes, but only the numbering of the modes is different. (Mode

0: DC, Mode 1: Horizontal, Mode 2: Vertical, Mode 3: Plane. Also it is noticeable that both chroma components always use the same prediction mode.

In order to reduce the number of bits that comes from coding the choice of intra prediction modes for each 4x4 blocks, a predictive coding mechanism is developed. This mechanism exploits the correlation between intra 4x4 modes of neighboring blocks. It takes the prediction modes of previously coded 4x4 blocks and finds a "most probable mode" for the current block. If the current block's mode is same as the "most probable mode", then the encoder send a flag with a value of 1 instead of sending the prediction mode. Oppositely, if current block's mode is different from "most probable mode" then the flag is sent with a value of 0. The prediction mode is also sent but with the following change:

- If the current mode is smaller than "most probable mode" it is sent without any change.

- If the current mode is larger than "most probable mode" it is sent after being decreased by one.

Table 2.5 Coding of intra 4x4 prediction modes

| (most probable mode=2) |                                                                                                    |       |

|------------------------|----------------------------------------------------------------------------------------------------|-------|

| Current mode           | Description                                                                                        | Code  |

| 1                      | Flag and mode is coded. Mode value is sent directly without any change (i.e. 1 is sent)            | 0-001 |

| 2                      | Only flag is coded since this mode is equal to the most probable mode.                             | 1     |

| 3                      | Flag and mode information is coded. Mode value is sent after being decreased by 1 (i.e. 2 is sent) | 0-010 |

#### 2.4.2.2 Inter Prediction

Inter Prediction process exploits temporal redundancies in the video stream. In other words, it uses the similarity between successive frames for the compression. Inter prediction creates a prediction model from one or more previously encoded video frames of fields at variable block sizes. H.264 supports a range of block sizes from

16x16 down to 4x4 and fine 1/4 sample motion vectors for luma as well as 1/8 sample motion vectors for chroma component. Using multiple reference frames in inter prediction results in better compression efficiency. In the proposed encoder implementation only one reference frame is used but the design can be easily adapted to support multiple number of reference frames.

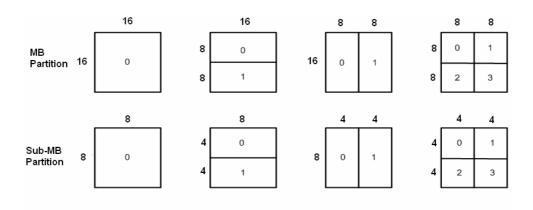

A macroblock can be partitioned into 16x8, 8x16, 8x8 blocks or remain as 16x16. If it is partitioned into 8x8 blocks, then these 8x8 blocks can be further partitioned into sub-blocks of 8x4, 4x8, 4x4 or remain as 8x8. A macroblock partition can not be mixed with sub-macroblock partition. That is to say, wen cannot have 16x8 and 4x8 partitions inside a macroblock.

Figure 2.4: Macroblock partitioning in inter prediction.

The macroblock partitions and sub-macroblock partitions gives rise to a large number of possible combinations within each macroblock. In an ideal encoder, a large partition size should be selected for a homogeneous area whereas a small partition size should be selected for a detailed area. Moreover, choosing a small partition size may give better prediction but it results in increased number of motion vectors and reference indexes since each block has its own vector and reference frame. Thus, small partitioning does not only brings better prediction but also larger number of bits. Finding the optimal partition size is one of the challenging tasks in an encoder.

A chroma motion vector is derived from the corresponding luma motion vector. Since the accuracy of luma motion vectors is one-quarter sample and chroma has half resolution compared to luma, the accuracy of chroma motion vectors is one-eight sample. That is, a value of 1 for the chroma motion vector refers to one-eight sample displacement. When the luma vector applies to 8x16 luma samples, the corresponding

chroma vector applies to 4x8 chroma samples and when the luma vector applies to 4x4 luma samples, the corresponding chroma vector applies to 2x2 chroma samples. The horizontal and vertical components of each luma motion vector are halved when applied to the chroma blocks.

The encoder developed in this thesis does not support quarter-pel motion compensation. Instead, it is based on integer motion search and compensation. In order to make the output bitstream decodable by the JM reference decoder[2], the resultant motion vectors are multiplied by 4. In this way, the JM reference decoder[2] uses pixel locations whose indexes are multiples of 4 (i.e. integer pixel locations) during the motion compensation. The same is true for chroma motion compensation. In the near future, I will make it to support quarter pel motion compensation.

## 2.4.2.2.1 Hierarchical Three Step Search

There are several motion search algorithms used for video compression. Among these, the full search algorithm gives best PSNR but it is not an efficient solution since it requires much computation. For real world implementations much intelligent algorithms with lower computation requirements are desired. Hierarchical three step search is such an algorithm which decreases the number of computations by 10 compared with full search [12].

According to hierarchical search, the search is done in three steps:

- 1-) Level2: At the first step, current frame and reference frame are averaged and down-sampled by 4 and a full search with a search range of 4 is performed. For this full search, we only use SAD of the current and reference blocks.

- 2-) Level1: The resultant vectors from level2 are passed to this step. The current frame and reference frame are now averaged and down sampled by 2 and again a full search with a search range of 4 is performed at the location shown by the vectors passed from level2. For this full search, we only use SAD of the current and reference blocks.

- 3-) Level0: At this final step, a final full search with a range of 4 is performed on the original current and reference frames. However, for this search we do not only use the SAD values but also  $\lambda*R$ . More specifically, a cost is calculated for each search mode and macroblock partition or sub-macroblock partition.

$$\cos t = SAD + \lambda \bullet R\{mv \ cand - mv \ pred\}$$

The R function in the cost formula returns us the number of bits required to transmit a vector with the given value. mv\_cand is the candidate vector for that search location and mv\_pred is the vector predicted using motion vector prediction.

#### 2.4.2.2.2 Motion Vector Prediction

Luminance motion vectors of neighboring blocks are highly correlated, so that each motion vector is predicted from early previously coded blocks. After finding a prediction vector, the difference between the current vector and the predicted vector is transmitted to the decoder. In other words, not the original vector but its difference from the prediction vector is coded in order to reduce the number of transmitted bits. At the decoder side, the predicted vector is formed in the same way and added to the transmitted motion vector difference in order to find current vector.

## 2.4.2.2.3 Transform and Quantisation

H.264 uses three transforms depending on the type of the data to be coded.

- 1. Hadamard transform for the 4x4 array of luma DC coefficients in macroblocks with type intra 16x16.

- 2. Hadamard transform for the 2x2 array of chroma DC coefficients.

- 3. DCT based transform for all other 4x4 blocks in the residual data.

The transformation matrixes and other detailed information about transform and quantization process can be found in [11].

#### 2.4.2.2.4 Coded Block Pattern (CBP)

Coded block pattern is a parameter sent by the encoder to the decoder. It specifies which 8x8 blocks in a macroblock are coded and which are not. According to the coefficients coming out of transform and quant, 8x8 blocks which do not contain any non-zero 4x4 blocks are determined and not coded. CBP is a value that tells the decoder

how many and which blocks are coded and transmitted. This information is hidden in the binary equivalent of cbp value. The least significant bit of cbp represents the zeroth 8x8 luma block. If that block is coded than LSB is 1, else it is 0. Likewise, the next three bits corresponds to other three 8x8 blocks. For instance, if all 8x8 luma blocks are coded the least significant four bits of cbp is 1111. If second 8x8 luma block is not coded then the least significant four bits of cbp is 1011. The leading 2 bits of cbp are for chroma DC and chroma AC blocks. If only chroma DC is found in the bitstream then leading 2 bits is 01; if both are found it is 10 and it is 00 when neither chroma DC nor chroma AC is found. Some of the possible values of cbp and its explanation are given in Table 2.6.

Table 2.6: Illustration of calculating cbp values for some coded blocks.

| CBP Value (binary equivalent) | Coded Blocks                                          |

|-------------------------------|-------------------------------------------------------|

| 47 (101111)                   | All Luma 8x8 Blocks + Chroma DC + Chroma AC           |

| 43 (101011)                   | 0th, 1st, 3rd Luma 8x8 Blocks + Chroma DC + Chroma AC |

| 31 (011111)                   | All Luma 8x8 Blocks + Chroma DC                       |

| 15 (001111)                   | All Luma 8x8 Blocks                                   |

| 7 (000111)                    | 0th, 1st, 2nd Luma 8x8 Blocks                         |

#### 2.4.2.2.5 Entropy Coding

Entropy coding aims at compressing the generated bitstream so that fewer bits are used for coding. It is uniquely decodable or in other words does not provide any error. The generated syntax elements and residual data are entropy coded. Context Adaptive Variable Length Coding (CAVLC) and Context Adaptive Binary Arithmetic Coding (CABAC) are two entropy coding methods of H.264. In the proposed baseline H.264 encoder CAVLC is developed. Context Adaptive Variable Length Coding (CAVLC) is found in all profiles whereas Context Based Adaptive Binary Arithmetic Coding (CABAC) is found in main profile. Other details about entropy coding are listed as follows:

All syntax elements other than residual transform coefficients are encoded by the Exp-Golomb code (UVLC)

Zig-zag ordered, 4x4 (and 2x2) blocks of transform coefficients are encoded by CAVLC.

Coefficients of residual data are scanned in zig-zag order.

Figure 2.5: Zig Zag scan order.

## 2.4.2.2.6 Deblocking Filter

This adaptive filter is designed to reduce the blocking artifacts in the block boundary and prevent propagation of accumulated coded noise. Filtering is applied to horizontal or vertical edges of 4x4 blocks in a macroblock adaptively. The filter smoothens block edges, improving the appearance of decoded frames. The filtered image is then used for motion-compensated prediction of future frames. The inter prediction for a P-Slice following an I-Slice is carried out using the filtered version of the I-Slice. However, the intra prediction inside the I-Slice is done using the previously reconstructed but unfiltered macroblocks.

The inclusion of deblocking filter before motion compensated predition stage is beneficial in terms of compression efficiency. Because the filtered image is much more resembles the original image than a blocky, unfiltered image.

The main principle of this filter is that it adjusts the amount of filtering adaptively according to the coding modes of neighbouring blocks and the gradient of image samples across the boundary. More detail about deblocking filter can be found in [11].

#### **CHAPTER 3**

#### TEXAS INSTRUMENTS TMS320DM642 DSP

Programmable digital signal processors (DSPs) are increasingly important in a wide range of video and imaging applications, such as machine vision, medical imaging, security monitoring, digital cameras and printers, and a large number of consumer applications driven by digital video processing including DVDs, digital TV, video telephony and many others. The importance of multimedia technology, services and applications is widely recognized by microprocessor designers. The number of special-purpose multimedia processors such as the Trimedia processor from Philips, Mitsubishi's multimedia processor and digital media processors of Texas Instruments are becoming more popular. These special purpose multimedia processors are being used in low-cost embedded applications such as set-top boxes, wireless terminals, digital TVs, DVDs and mobile applications.

Multimedia applications are characterized by requirements for processing flexibility, sophisticated algorithms and high data rates. One of the processor architectures to exploit parallelism of multimedia applications is the very long instruction word (VLIW) architecture. VLIW processors can exploit instruction level parallelism (ILP) in programs [13]. TMS320DM642 device is based on VLIW architecture and it seems to be a perfect choice for H.264 encoder implementation.

#### 3.1 Overview of DM642 DSP Core

The TMS320DM642 device is based on the high-performance, very-long-instruction-word (VLIW) architecture VelociTI.2 [14] developed by Texas Instruments. The key features of this device such as VLIW architecture, 2-level memory/cache

hierarchy, and EDMA engine makes it an excellent choice for computationally intensive video/image applications such as video coding and analysis.

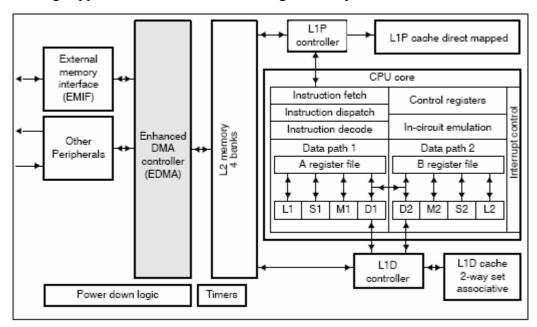

Figure 3.1: TMS320C64x DSP Block Diagram [14].

DM642 DSP core and essential features are listed as follows:

- The VelociTI.2 extensions in the eight functional units of DM642 include new instructions which accelerate performance in video and imaging applications.

- Two general-purpose register files (A and B)

- Eight functional units (.L1, .L2, .S1, .S2, .M1, .M2, .D1 and .D2)

- Two load-from-memory data paths (LD1 and LD2)

- Two store-to-memory data paths (ST1 and ST2)

- Two data address paths (DA1 and DA2)

- Two register file data cross paths (1X and 2X)

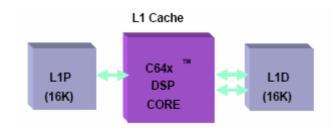

- It has a 16Kbytes direct mapped L1P program cache with 32-byte cache line (8-cycle L1P cache miss penalty). The L1D cache is 16Kbytes 2-way setassociative and has a 64-byte cache line. (6-cycle L1D cache miss penalty).

- 256Kbytes of internal memory can be mapped either RAM or cache (flexible RAM/cache allocation, 8-cycle L2 cache miss penalty). L2 4-way set associative cache has 128 byte cache line.

### 3.1.1 Register Files

There are two general purpose register files (A and B) in the C6000 data paths. For the C64x each of these files contains 32 32-bit registers (A0-A31 for file A and B0-B31 for file B). The general-purpose registers can be used for data; data address pointers, or condition registers. On the C64x, registers A0, A1, A2, B0, B1 and B2 can be used as condition registers. In all C6000 devices, registers A4-A7 and B4-B7 can be used for circular addressing.

The C64x register file supports data ranging in size from packed 8-bit data, packed 16-bit data, through 40-bit fixed point, 64-bit fixed point and 64-bit floating point data. Values larger than 32 bits, such as 40-bit long and 64-bit long quantities, are stored in register pairs, with the 32LSBs of data placed in an even-numbered register and the remaining 8 or 32 MSBs in the next upper register (which is always an odd-numbered register). Packed data types store either four 8-bit values or two 16-bit values in a single 32-bit register or four 16-bit values in a 64-bit register pair.

#### 3.1.2 Functional Units

The eight functional units in the C6000 data paths can be divided into two groups of four; each functional unit in one data path s almost identical to the corresponding unit in the other data path. The C64x contain many 8-bit and 16-bit instructions to support video and imaging applications.

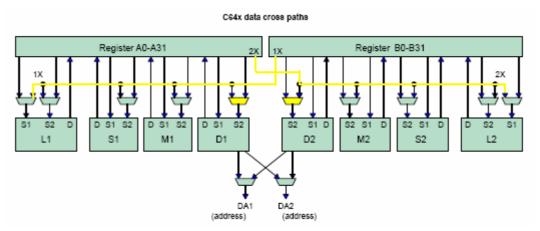

### 3.1.3 Register File Paths

Each functional unit reads directly from and writes directly to the register file within its own data path. That is, the .L1, .S1, .D1 and .M1 units write to register file A, and the .L2, .S2, .D2 and .M2 units write to the register file B.

Most data lines in the CPU support 32-bit operands, and some supporting long (40-bit) and double word (64-bit) operands. Each functional unit has its own 32-bit

write port into a general-purpose register file. Each functional unit has two 32-bit read ports for source operands src1 and src2. Four units (.L1, .L2, .S1 and .S2) have an extra 8-bit wide port for 40-bit long writes, as well as an 8-bit input for 40-bit long reads. Because each unit has its own 32-bit write port, all eight units can be used in parallel with every cycle when performing 32 bit operations. Since each C64x multiplier can return up to a 64-bit result, an extra write port has been added from the multipliers to the register file.

The register files are also connected to the opposite-side register file's functional units via the 1X and 2X cross paths. These cross paths allow functional units from one data path to access a 32-bit operand from the opposite side's register file. The 1X cross path allows functional units from data path A to read its source from register file B. Similarly, the 2X cross path allows functional units from data path B to read its source from register file A.

Figure 3.2: C64x Data Cross Paths [14]

On the C64x, all eight of the functional units have access to the register file on the opposite side via a cross path. The .M1, .M2, .S1, .S2, .D1 and .D2 units' src2 inputs are selectable between the cross path and the register file found on the same side. In the case of the .L1 and .L2, both src1 and src2 inputs are also selectable between the cross path and the same-side register file.

The C64x pipelines data cross path accesses allow multiple units per side to read the same cross-path source simultaneously. The cross path operand for one side may be used by up to two functional units on that side in an execute packet.

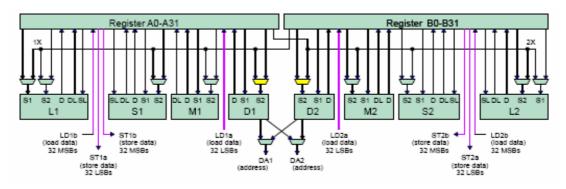

### 3.1.4 Memory, Load and Store Paths

The data address paths named DA1 and DA2 are each connected to the .D units in both data paths. Load/Store instructions can use an address register from one register file while loading to or storing from the other register file.

Figure 3.3: C64x Memory Load and Store Paths [14]

The C64x device supports double-word loads and stores. There are four 32-bit paths for loading data for memory to the register file. For side A, LD1a is the load path for the 32 LSBs; LD1b is the load path for the 32 MSBs. There are also four 32-bit paths for storing register values to memory from each register file. ST1a is the write path for the 32 LSBs on side A; ST1b is the write path for the 32MSBs for side A. For side B, ST2a is the write path for the 32 LSBs and ST2b is the write path for the 32 MSBs. Wide loads are essential in sustaining processing throughput.

The C64x device can also access words and double words at any byte boundary using non-aligned loads and stores. As a result, word and double-word data does not always need alignment to 32-bit or 64-bit boundaries. This feature is particularly useful in motion estimation and video filtering operations, where one may need access to data from any arbitrary byte boundary in memory. Non-aligned loads and stores combined with the pack and unpack instructions mean that the compiler does not have to format the data to take advantage of the 8-bit and 16-bit hardware extensions. Without these operations, significant effort would be needed to leverage the parallelism. C64x provides a complete set of data flow operations to sustain the maximum performance

improvement made possible by the 8-bit and 16-bit extensions added to the C6000 architecture.

#### 3.1.5 Additional Functional Unit Hardware

Additional hardware has been built into the eight functional units of the C64x. Each .M unit can perform two 16x16 bit multiplies or four 8x8 bit multiplies every clock cycle. Also, the .D units can access words and double words on any byte boundary by using load and store instructions.