# A High Power Handling Capability CMOS T/R Switch for X-Band Phased Array Antenna Systems

Tolga Dinc, Samet Zihir, Ferhat Tasdemir, and Yasar Gurbuz

Faculty of Engineering and Natural Sciences, Sabanci University Orhanli, Tuzla, 34956 Istanbul, Turkey

Abstract — This paper presents a single-pole double-throw (SPDT) transmit/receive (T/R) switch fabricated in 0.25-µm SiGe BiCMOS process for X-Band (8 – 12 GHz) phased array radar applications. The switch is based on series-shunt topology with combination of techniques to improve insertion loss (IL), isolation and power handling capability (P<sub>1dB</sub>). These techniques include optimization of transistor widths for lower insertion loss and parallel resonance technique to improve isolation. In addition, DC biasing of input and output ports, on-chip impedance transformation networks (ITN) and resistive body-floating are used to improve P<sub>1dB</sub> of the switch. All these design techniques resulted in a measured IL of 3.6 dB, isolation of 30.8 dB and P<sub>1dB</sub> of 28.2 dBm at 10 GHz. The return losses at both input and output ports are better than 16 dB from 8 to 12 GHz. To our knowledge, this work presents the highest  $P_{1dB}$  at X-Band compared to other reported singleended CMOS T/R switches in the literature.

Index Terms — T/R switch, SPDT switch, phased array radar, 0.25 µm CMOS, body-floating, DC biasing.

## I. INTRODUCTION

As a result of recent advances in Si-based IC technologies, next generation X-band Phased Array Radar aim to use low-cost, fully integrated transmit/receive (T/R) modules in order to decrease deployment and operational expenses [1]. In fully integrated T/R module design, one particular challenge is the design of CMOS T/R switch since it can directly affect the transmission efficiency and the noise figure of the receiver/system [2]. Therefore, in the recent years, CMOS T/R switch design has become an active area of research and several design techniques are reported to enhance IL, isolation and P<sub>IdB</sub> compression point of T/R switches implemented in CMOS process [3]-[9]. In this work, we present a new CMOS SPDT T/R switch designed, based on design techniques for improving IL, isolation, and P<sub>1dB</sub>.

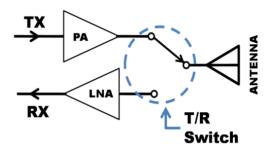

As shown in Fig.1, SPDT T/R switch is a block in a TR module that routes antenna to either transmitter (TX) or receiver (RX). Hence, a typical SPDT T/R switch can operate either in transmit or receive mode at which low-loss paths are formed between ANT and TX or RX while isolating the other port, respectively.

In a typical transceiver system, primary aims are to direct high power RF signal from transmitter to antenna

Fig. 1. A simple block diagram of T/R module.

while preventing leakage of that large signal into more sensitive front-end of receiver and to provide a low loss path between TX/ANT and particularly ANT/RX ports. Therefore, a T/R switch designed for a transceiver system should provide low loss and high isolation between TX-RX ports, as well as handling high power output signals of power amplifier during transmit mode of operation.

# II. CIRCUIT DESIGN

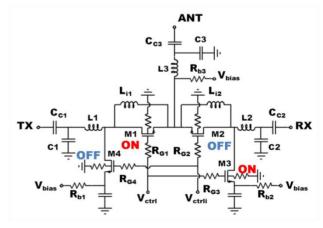

In this work, an X-Band SPDT T/R switch whose schematic is shown in Fig. 2 is designed. It is mainly based on series-shunt topology reported in [3]. M1 and M2 transistors perform the main switching function of directing signal between TX/ANT or ANT/RX ports. M3

Fig. 2. Circuit schematic of the designed SPDT T/R switch. In TX mode, M1 and M3 operate in deep triode region ( ON ) while M2 and M4 operate in cut off region ( OFF ).

and M4 transistors improve isolation between TX and RX ports by grounding the leakage signal. Operation of the switch is as follow: when V<sub>ctrl</sub> is high and V<sub>ctrli</sub> is low, the switch operates in the transmit mode. In that mode, M1 and M3 operate in deep triode region (ON state) while M2 and M4 operate in cut off region (OFF state). Hence, channel resistance of M1 is very low and it forms a low loss connection between TX and ANT so that incoming signal from transmitter can be routed to antenna. Since M2 is operating in cut off region, channel resistance is very large and RX port is isolated from TX and ANT. Also, leakage signal due to parasitic coupling in M2 is directed to ground through low resistance path formed by M3 transistor before reaching receiver end. In receive mode, basic operation of the switch is similar to transmit mode and only difference is that roles of M1 and M3 are interchanged by M2 and M4, respectively.

Several techniques are incorporated into basic series/shunt topology to improve IL, isolation and power handling capability. Firstly, the sizes of the NMOS transistors in Fig. 2 are scaled for lower insertion loss, without degrading the isolation significantly. Insertion loss is mainly determined by resistances of M1 or M2 in the ON state. Resistance of the MOS transistor in the ON state should be as low as possible to decrease insertion loss of the switch. The resistance of a MOS transistor operating in the deep triode region ( $R_{on}$ ) is defined by

$$R_{on} = \frac{1}{\mu_{n} C_{ox} (\frac{W}{I}) (V_{GS} - V_{th})}$$

(1)

As can be seen in (1), as the width increases for fixed length of transistors, on resistance decreases and in return insertion loss decreases. However, there is a practical limit in increasing transistor width since as the width is increased, source/drain to body parasitic capacitances and, in return, coupling to substrate increases. In other words, there is a trade-off between  $R_{\rm on}$  and parasitic capacitance which results in an optimum value for width of the transistor at a given operating frequency. The optimum width for minimum insertion loss at 10GHz has been found as 600-um.

To improve the insertion loss and power handling capability, we have taken into account the effect of  $\mathbf{DC}$  biasing. Based on the analysis of this effect, antenna node and sources of shunt transistors are biased at 2V through  $R_{b1}$  -  $R_{b3}$  resistors. This is to increase turn-on voltage of source/drain-to-body junctions and to decrease voltage dependent parasitic capacitances of NMOS transistors. The values of  $R_{b1}$  -  $R_{b3}$  should be high enough to prevent leakage into bias port. Otherwise, considerable amount of

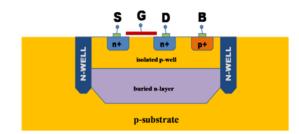

Fig. 3. Cross-sectional view of a typical isolated NMOS transistor.

the input signal would be lost due to leakage and thus insertion loss would increase. Based on our analysis and confirmation by simulations,  $R_{b1}$  -  $R_{b3}$  resistors are chosen as  $10\text{-k}\Omega$  to prevent this phenomenon. Complete biasing method is shown in Fig. 2. A value of 8 pF for  $C_{B1}$  and  $C_{B2}$  by-pass capacitors are used to bias source terminals of M3/M4 while introducing RF ground to the sources of M3 and M4 [10].

As the frequency increases, parasitic capacitances' effect on the isolation becomes significant. Therefore, **to** improve the isolation of the switch at X-Band, shunt inductor resonance technique is used. To implement this technique, 680 pH inductors  $L_{i1}$  and  $L_{i2}$  are connected in parallel with M1 and M2 transistors. At resonance frequency in TX mode, inductor  $L_{i2}$  resonates with total parasitic capacitance of M2 to form a high impedance path to RX port. Hence, coupling through OFF switching transistor M2 to RX port reduces.

Power handling of the T/R switches is mainly limited by forward biasing of source/drain-to-body junctions during negative cycles of large RF signal. Body floating technique is used to improve power handling of the switch by reducing the signal loss through source/drain-to-body junctions. To implement this technique, body of the all transistors are connected to ground through  $10\text{-}k\Omega$  resistors. Isolated NMOS (iNMOS) transistors, shown in Fig. 3, offered by IHP 0.25  $\mu m$  BiCMOS process is used to separate the body of each transistor from the p-substrate to be able to use transistors as four terminals device and apply body floating technique.

Besides DC biasing and body floating techniques, impedance transformation networks are employed to improve  $P_{1dB}$  of the switch. A 50  $\Omega$  source and load impedances at TX, RX and ANT port are transformed into lower impedances. Both series C - shunt L and shunt C-series L matching networks were tried in analysis and simulations. According to these results, a matching is achieved by shunt C- series L, in a broader frequency band and thus becoming our choice for matching network. 200fF metal-insulator-metal (MiM) capacitors and 540 pH octagonal integrated inductors are used to implement these networks.

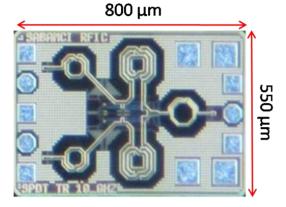

#### III. MEASUREMENT

The switch was fabricated in IHP, 0.25- $\mu$ m SiGe BiCMOS technology. This technology provides one-poly and five-metal layers, including thick metal layers to implement high-Q integrated inductors. The die photo of the switch is shown in Fig. 4. The chip area, including pads, is  $0.44~\text{mm}^2$ . Inductors are custom designed with the thickest top metal layer in the process to take advantage of its lower resistivity and lower capacitance to ground.

Fig. 4. Die photo of the SPDT T/R switch. The chip area including pads is  $0.44 \text{ mm}^2$ .

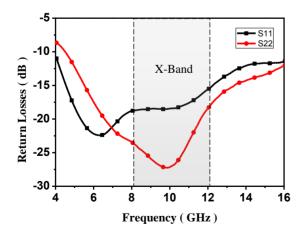

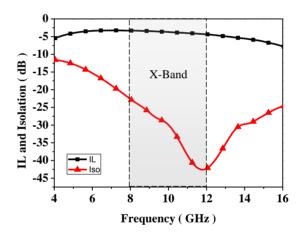

Measurements of T/R switch were performed under 4.5 V and 0 V control voltages. As shown in Fig. 5, the measured insertion loss and isolation is 3.6 dB and 30.8 dB, respectively, at 10 GHz. Insertion loss of the switch varies between 3.2 dB and 4.1 dB in the whole span of X-Band. The measured isolation is between ANT and RX ports. According to analysis and simulations, TX-RX isolation is almost same with ANT-RX isolation. Measured return losses are shown in Fig. 6. The return loss at TX port, S<sub>11</sub>,

Fig. 6. Measured input return loss, S11, and output return loss, S22 of the T/R switch.

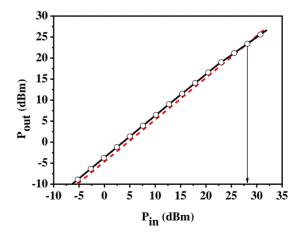

is -18 dB at 10 GHz and ranges from -19 dB to -16 dB at X-Band. The return loss at ANT port,  $S_{22}$ , is -28 dB at 10 GHz and ranges between -18 dB and -28 dB at X-Band. Due to the symmetry of the switch, IL and RL in the receive mode are almost equal to transmit mode values. As shown in Fig. 7, the switch results in an input 1 dB compression point (IP<sub>1dB</sub>) of 28.2 dBm at 10 GHz. By biasing sources and drains of the transistors to a higher potential, higher power handling can be achieved at the expense of reliability of the switch. In addition to operation in the X-Band, switch can also operate from 6 GHz to 8 GHz with adequate figures of merit.

TABLE I compares performance of our new switch with that of other single-ended CMOS T/R switches, in the literature, operating at X-Band. This work achieves the highest power handling capability among the single-ended CMOS X-Band switches to up to the date, to the best of our knowledge.

Fig. 5. Measured insertion loss and isolation of the T/R switch.

Fig. 7. Measured 1 dB compression point (P1dB) of the T/R switch at 10 GHz.

TABLE I COMPARISON OF THE SWITCH WITH REPORTED WORKS

| Frequency (GHz) | Figures of Merit |                |                        | Chip Area | Chip Area Technique                                                     | Technology                | Ref.         |

|-----------------|------------------|----------------|------------------------|-----------|-------------------------------------------------------------------------|---------------------------|--------------|

|                 | IL (dB)          | Isolation (dB) | P <sub>1dB</sub> (dBm) | $(mm^2)$  | recinique                                                               | reciniology               | Kel.         |

| 8-12            | 3.2 – 4.1        | 23.2-42.5      | 28.2                   | 0.44      | Series-shunt, Body<br>floating, ITN, Parallel<br>Resonance, S/D Biasing | 0.25 μm<br>SiGe<br>BiCMOS | This<br>work |

| 3-10            | $3.1 \pm 1.3$    | 25–32          | 18-20                  | 0.62      | Distributed Topology                                                    | 0.18 μm<br>CMOS           | [11]         |

| 3- 10.6         | 2.2 – 4.2        | 33–37          | -                      | 0.9       | Synthetic Transmission<br>Line                                          | 0.25 μm<br>CMOS           | [12]         |

| 10              | 1.81             | 21.9           | 10.1                   | 0.67      | Shunt                                                                   | 0.13 μm<br>SiGe           | [1]          |

|                 | 2.25             | 23.1           | 11.1                   | 0.58      | Series/Shunt                                                            | BiCMOS                    |              |

## IV. CONCLUSION

This paper presented an X-Band T/R switch fabricated in 0.25- $\mu m$  SiGe BiCMOS technology. To authors' knowledge this paper presents the single-ended CMOS T/R switch with highest P1d at X-Band. The switch is based on series-shunt topology with combination of the different design techniques such as parallel resonance technique to improve isolation, DC biasing the input and output ports, using on-chip impedance transformation networks (ITN) and resistive body-floating to improve  $P_{1dB}$  and finally scaling of transistor sizes for lower insertion loss of the switch.

### ACKNOWLEDGEMENT

This work is supported by The Scientific and Technological Research Council of Turkey under grant 110E107. The authors would like to thank IHP Microelectronics for providing IC fabrication and technical support.

#### REFERENCES

- [1] W.-M. L. Kuo, J. P. Comeau, J. M. Andrews, J. D. Cressler and M. A. Mitchel, "Comparison of Shunt and Series/Shunt nMOS Single-Pole Double-Throw Switches for X-Band Phased Array T/R Modules," in *Silicon Monolithic Integrated Circuits in RF Systems*, 2007, pp. 249-252.

- [2] C. Hove, J. L. Faaborg, M. B. Jenner, S. Lindfors, "0.35 μm CMOS TR Switch for 2.4GHz Short Range Wireless Applications", Analog *Integrated Circuits and Signal Processing*, Vol. 38, pp. 35-42, 2004.

- [3] F.-J. Huang and K. O, "A 0.5-\_m CMOS T/R switch for 900-MHz wireless applications," *IEEE J. Solid-State Circuits*, vol. 36, no. 3, pp. 486–492, Mar. 2001.

- [4] F.-J. Huang and K. K. O, "Single-pole double-throw CMOS switches for 900-MHz and 2.4-GHz applications on psilicon substrates," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 35–41, Jan. 2004.

- [5] X. J. Li, Y. P. Zhang, "Flipping the CMOS Switch," *IEEE Microwave Magazine*, Vol. 11, pp. 86-96, Feb. 2010.

- [6] M. C. Yeh, et al., "Design and analysis for a miniature CMOS SPDT switch using body-floating technique to improve power performance", *IEEE Transactions Microwave Theory and Techniques*, Vol. 54, Jan. 2006.

- [7] C. Y. Ou, C. Y. Hsu, H. R. Lin, H. R. Chuang, "A High-Isolation High-Linearity 24-GHz CMOS T/R Switch in the 0.18um CMOS Process," in *European Microwave Integrated Circuits Conference*, 2009, pp. 250-253.

- [8] P. Park, D.H. Shin, J.J. Pekarik, M. Rodwell and C. P. Yue, "A High-Linearity, LC-Tuned, 24-GHz T/R Switch in 90-nm CMOS," in *IEEE RFIC Symposium*, 2008, pp. 369-372.

- [9] Q. Li and Y. P. Zhang, "CMOS T/R Switch Design: Towards Ultra-Wideband and Higher Frequency," in *IEEE Journal of Solid-State Circuits*, Vol. 42, pp. 563-570, March 2007.

- [10] Dinc, T., Zihir, S., Gurbuz, Y., "CMOS SPDT T/R switch for X-band, on-chip radar applications," *Electronics Letters*, vol.46, no.20, pp.1382-1384, September 30 2010.

- [11] K. -H. Pao, et al., "A 3-10 GHz Broadband CMOS T/R Switch for UWB Applications," in Proceedings of European Microwave Integrated Circuits Conference, 2006, pp. 452-455.

- [12] Y. Jin and C. Nguyen, "A 0.25- μm CMOS T/R Switch for UWB Wireless Communications," in *IEEE Microwave and Wireless Components Letters*, Vol. 15, pp. 502-504, August 2005.